概述

存儲器

存儲器存儲器的主要功能是存儲程式和各種數據,並能在計算機運行過程中高速、自動地完成程式或數據的存取。存儲器是具有“記憶”功能的設備,它採用具有兩種穩定狀態的物理器件來存儲信息。這些器件也稱為記憶元件。在計算機中採用只有兩個數碼“0”和“1”的二進制來表示數據。記憶元件的兩種穩定狀態分別表示為“0”和“1”。日常使用的十進制數必須轉換成等值的二進制數才能存入存儲器中。計算機中處理的各種字元,例如英文字母、運算符號等,也要轉換成二進制代碼才能存儲和操作。

存儲器:存放程式和數據的器件;

存儲位:存放一個二進制數位的存儲單元,是存儲器最小的存儲單位,或稱記憶單元;

存儲字:一個數(n位二進制位)作為一個整體存入或取出時,稱存儲字;

存儲單元:存放一個存儲字的若干個記憶單元組成一個存儲單元;

存儲體:大量存儲單元的集合組成存儲體;

存儲單元地址:存儲單元的編號;

字編址:對存儲單元按字編址;

位元組編址:對存儲單元按位元組編址;

定址:由地址尋找數據,從對應地址的存儲單元中訪存數據;

結構組成

存儲器

存儲器構成存儲器的存儲介質,目前主要採用半導體器件和磁性材料。存儲器中最小的存儲單位就是一個雙穩態半導體電路或一個CMOS電晶體或磁性材料的存儲元,它可存儲一個二進制代碼。由若干個存儲元組成一個存儲單元,然後再由許多存儲單元組成一個存儲器。 一個存儲器包含許多存儲單元,每個存儲單元可存放一個位元組。每個存儲單元的位置都有一個編號,即地址,一般用十六進制表示。一個存儲器中所有存儲單元可存放數據的總和稱為它的存儲容量。假設一個存儲器的地址碼由20位二進制數(即5位十六進制數)組成,則可表示220,即1M個存儲單元地址。每個存儲單元存放一個位元組,則該存儲器的存儲容量為1KB。

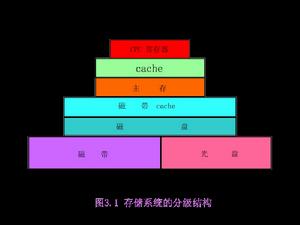

存儲系統的分級結構

存儲系統的分級結構把存儲器分為幾個層次主要基於下述原因:

各存儲器之間的關係

各存儲器之間的關係2、使用磁碟作為外存,不僅價格便宜,可以把存儲容量做得很大,而且在斷電時它所存放的信息也不丟失,可以長久保存,且複製、攜帶都很方便。

分類

1.按存儲介質分類

半導體存儲器

半導體存儲器(1)半導體存儲器用半導體器件組成的存儲器稱為半導體存儲器;特點:集成度高、容量大、體積小、存取速度快、功耗低、價格便宜、維護簡單.主要分兩大類:雙極型存儲器:TTL型和ECL型.金屬氧化物半導體存儲器(簡稱MOS存儲器):靜態MOS存儲器和動態MOS存儲器。

(2)磁表面存儲器用磁性材料做成的存儲器稱為磁表面存儲器,簡稱磁存儲器。它包括磁碟存儲器、磁帶存儲器等。特點:體積大、生產自動化程度低、存取速度慢,但存儲容量比半導體存儲器大得多且不易丟失。

(3)雷射存儲器信息以刻痕的形式保存在盤面上,用雷射束照射盤面,靠盤面的不同反射率來讀出信息。光碟可分為唯讀型光碟(CD-ROM)、只寫一次型光碟(WORM)和磁光碟(MOD)三種.

2.按存取方式分類

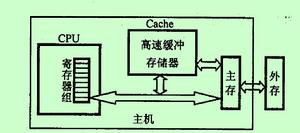

(1)隨機存儲器(RAM):如果存儲器中任何存儲單元的內容都能被隨機存取,且存取時間與存儲單元的物理位置無關,則這種存儲器稱為隨機存儲器(RAM)。RAM主要用來存放各種輸入/輸出的程式、數據、中間運算結果以及存放與外界交換的信息和做堆疊用。隨機存儲器主要充當高速緩衝存儲器和主存儲器。

(2)串列訪問存儲器(SAS):如果存儲器只能按某種順序來存取,也就是說,存取時間與存儲單元的物理位置有關,則這種存儲器稱為串列訪問存儲器。串列存儲器又可分為順序存取存儲器(SAM)和直接存取存儲器(DAM)。順序存取存儲器是完全的串列訪問存儲器,如磁帶,信息以順序的方式從存儲介質的始端開始寫入(或讀出);直接存取存儲器是部分串列訪問存儲器,如磁碟存儲器,它介於順序存取和隨機存取之間。

(3)唯讀存儲器(ROM):唯讀存儲器是一種對其內容只能讀不能寫入的存儲器,即預先一次寫入的存儲器。通常用來存放固定不變的信息。如經常用作微程式控制存儲器。目前已有可重寫的唯讀存儲器。常見的有掩模ROM(MROM),可擦除可程式ROM(EPROM),電可擦除可程式ROM(EEPROM).ROM的電路比RAM的簡單、集成度高,成本低,且是一種非易失性存儲器,計算機常把一些管理、監控程式、成熟的用戶程式放在ROM中。

3.按信息的可保存性分類

非永久記憶的存儲器:斷電後信息就消失的存儲器,如半導體讀/寫存儲器RAM。

永久性記憶的存儲器:斷電後仍能保存信息的存儲器,如磁性材料做成的存儲器以及半導體ROM.

4.按在計算機系統中的作用分

根據存儲器在計算機系統中所起的作用,可分為主存儲器、輔助存儲器、高速緩衝存儲器、控制存儲器等。為了解決對存儲器要求容量大,速度快,成本低三者之間的矛盾,目前通常採用多級存儲器體系結構,即使用高速緩衝存儲器、主存儲器和外存儲器。

工作原理

這裡只介紹動態存儲器(DRAM)的工作原理。

動態存儲器每片只有一條輸入數據線,而地址引腳只有8條。為了形成64K地址,必須在系統地址匯流排和晶片地址引線之間專門設計一個地址形成電路。使系統地址匯流排信號能分時地加到8個地址的引腳上,藉助晶片內部的行鎖存器、列鎖存器和解碼電路選定晶片內的存儲單元,鎖存信號也靠著外部地址電路產生。

當要從DRAM晶片中讀出數據時,CPU首先將行地址加在A0-A7上,而後送出RAS鎖存信號,該信號的下降沿將地址鎖存在晶片內部。接著將列地址加到晶片的A0-A7上,再送CAS鎖存信號,也是在信號的下降沿將列地址鎖存在晶片內部。然後保持WE=1,則在CAS有效期間數據輸出並保持。

當需要把數據寫入晶片時,行列地址先後將RAS和CAS鎖存在晶片內部,然後,WE有效,加上要寫入的數據,則將該數據寫入選中的存貯單元。

由於電容不可能長期保持電荷不變,必須定時對動態存儲電路的各存儲單元執行重讀操作,以保持電荷穩定,這個過程稱為動態存儲器刷新。PC/XT機中DRAM的刷新是利用DMA實現的。首先套用可程式定時器8253的計數器1,每隔1⒌12μs產生一次DMA請求,該請求加在DMA控制器的0通道上。當DMA控制器0通道的請求得到回響時,DMA控制器送出到刷新地址信號,對動態存儲器執行讀操作,每讀一次刷新一行。

作用

存儲器主要是存儲程式和數據。就象存放貨物的倉庫一樣,人們在倉庫中存放貨物時為了便於存放和拿取,通常將貨物在放的位置進行編號,並且留有存放及拿取的通路。

管理方式

存儲器晶片

存儲器晶片伺服器在存儲器環境按這樣的方法分配存儲器:在某個環境分配的存儲器可以被環境析構器釋放而不會影響其他環境中分配的存儲器.所有存儲器分配(通過 palloc 等)都被當作在當前環境的區域中分配存儲器.如果你試圖釋放(或再分配)不在當前環境的存儲器,你將得到不可預料的結果。創建存儲器環境和切換存儲器環境是SPI 管理器中存儲器管理器的任務。

SPI 過程處理兩種存儲器環境:上層執行器存儲器環境和過程存儲器環境(如果已聯接)。在一個過程與 SPI 管理器聯接之前,當前存儲器環境是上層執行器環境,所以所有由過程自身通過 palloc/repalloc 或通過 SPI 套用函式在聯接到 SPI 管理器之前分配的存儲器都在這個環境裡.在進行 SPI_connect 調用之後,當前環境是過程自身所有的.通過 palloc/repalloc 或通過 SPI 套用函式分配的存儲器(除了 SPI_copytuple,SPI_modifytuple,SPI_palloc 和 SPI_repalloc 以外)都在這個環境中分配.當進程與 SPI 管理器斷開(通過調用 SPI_finish)後,當前環境恢復為上層執行器環境並且所有在過程存儲器環境分配的存儲器都被釋放,並且不可繼續使用。如果你想返回一些東西給上層執行器,那么你必須為此在上層環境分配一片存儲器。SPI 不能自動釋放在上層執行器環境裡分配的存儲器。SPI 在查詢完成後自動釋放查詢執行期間的存儲器分配。

常見實體

各種存儲器

各種存儲器cf快閃記憶體卡

一種袖珍快閃記憶體卡,(compact flash card)。像pc卡那樣插入數位相機,它可用適配器,(又稱轉接卡),使之適應標準的pc卡閱讀器或其他的pc卡設備。CF存儲卡的部分結構採用強化玻璃及金屬外殼,cf存儲卡採用standard ata/ide接口界面,配備有專門的pcm-cia適配器(轉接卡),筆記本電腦的用戶可直接在pcmcia插槽上使用,使數據很容易在數位相機與電腦之間傳遞。

SM快閃記憶體卡

即smart media,智慧型媒體卡,一種存儲媒介。sm卡採用了ssfdg/flash記憶體卡,具有超小超薄超輕等特性,體積37(長)×45(寬)×0.76(厚)毫米,重量是1.8g,功耗低,容易升級,sm轉換卡也有pcmcia界面,方便用戶進行數據傳送。

memory stick duo

memory stick duo即微型記憶棒,微型記憶棒的體積和重量都為普通記憶棒的三分之一左右,目前最大存儲容量可以達到128mb。

sd快閃記憶體卡

即SecureDigital, 32×24×2.11 存儲的速度快,非常小巧,外觀和MMC一樣,目前市面上較多數數位相機使用這種格式的存儲卡,市場占有率第一。

1G SD存儲卡

1G SD存儲卡xd快閃記憶體卡

即Fuji film(富士膠捲)和OLYMPUS(奧林巴斯)聯合推出的xD-Picture卡,體形很小,傳輸速度很快,不過價格很昂貴。

mmc快閃記憶體卡

即MultiMedia Card ,外型和SD完全一樣,很多時候也通用。

微硬碟

是一種比較高端的存貯產品,目前“IBM(日立)”和國產品牌“南方匯通”都推出了自己的微硬碟產品。微型硬碟外型和CF卡完全一樣,使用同一型號接口。

優卡

優卡是Lexar公司生產的一種數位相機存儲介質,外形和一般的cf卡相同,可以用在使用cf卡的數位相機、pda、mp3等數碼設備上,同時可以直接通過usb接口與計算機系統在線上,用作移動存儲器。

數字膠捲

數字膠捲是lexar公司生產的的一種數位相機的存儲介質,同日立的sm卡、松下的sd卡、索尼的memorystick屬同類的數字存儲媒體。

另外,PC卡轉換器是一種接外掛程式,可以把cf卡或sm卡插入其中,然後,整體作為一個pc卡插入計算機的pcmica插口,這是常用於便攜機的一種通用擴展接口,可以接入pcmica記憶體卡、pcmica硬碟、pcmica數據機等。

擴展

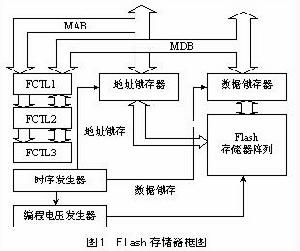

存儲器是單片機系統中使用最多的外擴晶片,對MCS-51單片機而言,由於程式存儲器與數據存儲器空間在物理空間的上的各自獨立性,使得兩者的擴展方法略有不同。

單片機一直處於不斷的取指令碼-執行-取指令碼-執行的工作過程中,在取指令碼時和執行MOVC指令時PSEN會變為有效,和其它信號配合完成從程式存儲器讀取數據。在本

節中,介紹目前常用的EPROM、RAM、E2PROM以及Flash存儲器的擴展方法。

一、外部程式存儲器擴展概述

目前單片機有ROM型、EPROM型和無ROM型晶片。不管使用哪種晶片,當片內程式存儲器容量滿足不了要求時,均需進行系統擴展。擴展時要注意以下幾點:

(1)程式存儲器有單獨的地址編號(0000H~FFFFH),可定址64KB範圍。雖然與數據存儲器地址重疊,但不會被占用。程式存儲器與數據存儲器共用地址匯流排和數據匯流排。

(2)對片內有ROM(EPROM)的單片機,片內EPROM與片外EPROM採用相同的操作指令,片內與片外程式存儲器的選擇靠硬體結構實現,即由的高低電平來選擇。

(3)程式存儲器使用單獨的控制信號和指令,其數據讀取控制及指令不用數據存儲器的 信號和MOVX指令,而是由 控制,讀取數據用MOVC查表指令。

(4)隨著大規模積體電路的發展,單片程式存儲器的容量越來越大,構成系統時所使用的EPROM晶片數量越來越少,因此地址選擇大多採用線選法,而不用地址解碼法。

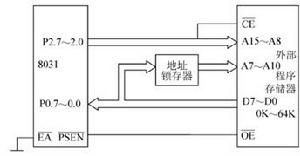

MCS-51系列單片機外部EPROM擴展原理如圖6-6所示。

圖6-6 外部EPROM擴展原理

圖6-6 外部EPROM擴展原理由圖可見,P0口和P2口提供16位地址碼。其中P0口作為分時復用的地址/數據匯流排。當從外部EPROM取指令時,從P0口輸出低8位地址,由ALE地址鎖存允許信號的下降沿將低8位地址碼打入地址鎖存器,它的輸出與存儲器的低8位地址A7~A0相連。存儲器的8位數據線D7~D0與P0口相連,以便輸入讀取的指令代碼。在一個唯讀存儲器讀周期中,P0口前半周期輸出低8位地址碼,後半周期輸入讀取的指令代碼。

由P2口輸出高8位地址碼。由於P2口輸出由鎖存功能,而且在整個讀指令周期內不作它用,故直接與存儲器的高8位地址A15~A8相連。

主機的 為外部程式存儲器選通信號,它與存儲器的 (指令代碼輸出選通)信號相連。

EPROM晶片的片選端 如何連線,與單片機系統的地址分配和硬體結構有關。可以直接接地;可以與P2口某位以線選法直接將來;也可以通過解碼器的輸出進行相連,應視具體

設計情況而定。

目前常用於單片機的程式存儲器為紫外線可擦除的唯讀存儲器EPROM,這種存儲器在斷電狀態下能保存所寫入的數據,在需要寫入新程式代碼之前,需要使用紫外線對晶片上石

英玻璃視窗進行光照,將原有程式擦除,再寫入新程式即可。需要說明的是,對於EPROM型的存儲器,要寫入程式數據時,應使用專門的寫入器。這類晶片在單片機套用系統中

以2716、2732、2764、27128、27256使用較多。

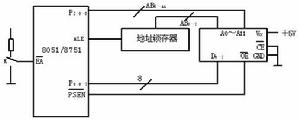

二、8051/8751的程式存儲器擴展

8051/8751是片內有ROM/EPROM的供應狀態。一般來說,採用8051/8751的單片機套用系統中,很少再用到外部程式存儲器擴展,這是因為同時使用片內、片外程式存儲器時會失

去選用8051/8751的優點,不如轉而採用單純的外部程式存儲器的8031套用系統。

圖6-7 擴展4k位元組EPROM的8051/8751

圖6-7 擴展4k位元組EPROM的8051/87518051/8751外部擴展4kEPROM程式存儲器的套用系統如圖6-7所示。在有外部程式存儲器的8051/8751系統中,程式存儲器的選擇線 的輸入電平會影響程式存儲器的結構。當圖中為高電平時,該系統具有8K位元組程式存儲器。8051/8751內部4k位元組ROM/EPROM程式存儲器地址為0000H~0FFFH;外部4k位元組2732EPROM程式存儲器地址為1000H~1FFFH。當程式計數器PC值在0000H~0FFFH時,指向片內程式存儲器,當PC值大於0FFFH時,則指向片外程式存儲器。當 為低電平時,8051/8751內部程式存儲器無效,系統只有外部程式存儲器4k位元組,其地址為0000H~0FFFH。此時,8051/8751相當於8031。

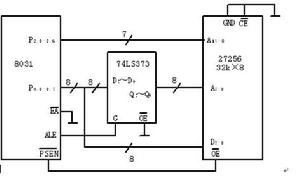

三、8031的程式存儲器擴展

圖6-8為使用一片EPROM27256和鎖存器74LS373構成的8031程式存儲器擴展電路。圖中8031的無關電路部分均未畫出。

對於需要較大程式存儲器容量的單片機套用系統則要進行片外存儲器的進一步擴展。擴展時,可以採用多個小容量存儲晶片組合擴展方式或者直接選用大容量存儲晶片進行擴

展。

圖6-8 一片27256的EPROM的擴展電路

圖6-8 一片27256的EPROM的擴展電路存儲器技術大多數根據其運行速度來命名。例如,PC100 SDRAM器件是指數據速率為100MHz的存儲技術,PC133則表示數據速率為133MHz,等等。儘管這種命名的習慣隨著時間發展而變化,但通常還是能給潛在買家提供關於存儲器運行速度的信息。事實上,今天的主流存儲技術都是按照其峰值數據速率來命名的,這將繼續成為評估存儲系統性能的要素之一。不過,在實際系統中,沒有存儲器能完全工作在其峰值速率下。

性能影響

從寫命令轉換到讀命令,在某個時間訪問某個地址,以及刷新數據等操作都要求數據匯流排在一定時間內保持休止狀態,這樣就不能充分利用存儲器通道。此外,寬並行匯流排和DRAM核心預取都經常導致不必要的大數據量存取。在指定的時間段內,存儲器控制器能存取的有用數據稱為有效數據速率,這很大程度上取決於系統的特定套用。有效數據速率隨著時間而變化,常低於峰值數據速率。在某些系統中,有效數據速率可下降到峰值速率的10%以下。

通常,這些系統受益於那些能產生更高有效數據速率的存儲器技術的變化。在CPU方面存在類似的現象,最近幾年諸如AMD和 TRANSMETA等公司已經指出,在測量基於CPU的系統的性能時,時鐘頻率不是唯一的要素。存儲器技術已經很成熟,峰值速率和有效數據速率或許並不比以前匹配的更好。儘管峰值速率依然是存儲器技術最重要的參數之一,但其他結構參數也可以極大地影響存儲器系統的性能。

有幾類影響有效數據速率的參數,其一是導致數據匯流排進入若干周期的停止狀態。在這類參數中,匯流排轉換、行周期時間、CAS延時以及RAS到CAS的延時(tRCD)引發系統結構中的大部分延遲問題。

匯流排轉換本身會在數據通道上產生非常長的停止時間。以GDDR3系統為例,該系統對存儲器的開放頁不斷寫入數據。在這期間,存儲器系統的有效數據速率與其峰值速率相當。不過,假設100個時鐘周期中,存儲器控制器從讀轉換到寫。由於這個轉換需要6個時鐘周期,有效的數據速率下降到峰值速率的 94%。在這100個時鐘周期中,如果存儲器控制器將匯流排從寫轉換到讀的話,將會丟失更多的時鐘周期。這種存儲器技術在從寫轉換到讀時需要15個空閒周期,這會將有效數據速率進一步降低到峰值速率的79%。表1顯示出針幾種高性能存儲器技術類似的計算結果。

顯然,所有的存儲器技術並不相同。需要很多匯流排轉換的系統設計師可以選用諸如XDR、RDRAM或者DDR2這些更高效的技術來提升性能。另一方面,如果系統能將處理事務分組成非常長的讀寫序列,那么匯流排轉換對有效頻寬的影響最小。不過,其他的增加延遲現象,例如庫(bank)衝突會降低有效頻寬,對性能產生負面影響。

DRAM技術要求庫的頁或行在存取之前開放。一旦開放,在一個最小周期時間,即行周期時間(tRC)結束之前,同一個庫中的不同頁不能開放。對存儲器開放庫的不同頁存取被稱為分頁遺漏,這會導致與任何tRC間隔未滿足部分相關的延遲。對於還沒有開放足夠周期以滿足tRC間隙的庫而言,分頁遺漏被稱為庫衝突。而tRC決定了庫衝突延遲時間的長短,在給定的DRAM上可用的庫數量直接影響庫衝突產生的頻率。

大多數存儲器技術有4個或者8個庫,在數十個時鐘周期具有tRC值。在隨機負載情況下,那些具有8個庫的核心比具有4個庫的核心所發生的庫衝突更少。儘管tRC與庫數量之間的相互影響很複雜,但是其累計影響可用多種方法量化。

考慮三種簡單的存儲器讀事務處理情況。第一種情況,存儲器控制器發出每個事務處理,該事務處理與前一個事務處理產生一個庫衝突。控制器必須在打開一個頁和打開後續頁之間等待一個tRC時間,這樣增加了與頁循環相關的最大延遲時間。在這種情況下的有效數據速率很大程度上決定於I/O,並主要受限於DRAM核心電路。最大的庫衝突頻率將有效頻寬削減到當前最高端存儲器技術峰值的20%到30%。

在第二種情況下,每個事務處理都以隨機產生的地址為目標。此時,產生庫衝突的機會取決於很多因素,包括tRC和存儲器核心中庫數量之間的相互作用。tRC值越小,開放頁循環地越快,導致庫衝突的損失越小。此外,存儲器技術具有的庫越多,隨機地址存取庫衝突的機率就越小。

第三種情況,每個事務處理就是一次頁命中,在開放頁中定址不同的列地址。控制器不必訪問關閉頁,允許完全利用匯流排,這樣就得到一種理想的情況,即有效數據速率等於峰值速率。

第一種和第三種情況都涉及到簡單的計算,隨機情況受其他的特性影響,這些特性沒有包括在DRAM或者存儲器接口中。存儲器控制器仲裁和排隊會極大地改善庫衝突頻率,因為更有可能出現不產生衝突的事務處理,而不是那些導致庫衝突的事務處理。

然而,增加存儲器佇列深度未必增加不同存儲器技術之間的相對有效數據速率。例如,即使增加存儲器控制佇列深度,XDR的有效數據速率也比 GDDR3高20%。存在這種增量主要是因為XDR具有更高的庫數量以及更低的tRC值。一般而言,更短的tRC間隔、更多的庫數量以及更大的控制器佇列能產生更高的有效頻寬。

實際上,很多效率限制現象是與行存取粒度相關的問題。tRC約束本質上要求存儲器控制器從新開放的行中存取一定量的數據,以確保數據管線保持充滿。事實上,為保持數據匯流排無中斷地運行,在開放一個行之後,只須讀取很少量的數據,即使不需要額外的數據。

另外一種減少存儲器系統有效頻寬的主要特性被歸類到列存取粒度範疇,它規定了每次讀寫操作必須傳輸的數據量。與之相反,行存取粒度規定每個行激活(一般指每個RAS的CAS操作)需要多少單獨的讀寫操作。列存取粒度對有效數據速率具有不易於量化的巨大影響。因為它規定一個讀或寫操作中需要傳輸的最小數據量,列存取粒度給那些一次只需要很少數據量的系統帶來了問題。例如,一個需要來自兩列各8位元組的16位元組存取粒度系統,必須讀取總共32位元組以存取兩個位置。因為只需要32個位元組中的16個位元組,系統的有效數據速率降低到峰值速率的50%。匯流排頻寬和脈衝時間長度這兩個結構參數規定了存儲器系統的存取粒度。

匯流排頻寬是指連線存儲器控制器和存儲器件之間的數據線數量。它設定最小的存取粒度,因為對於一個指定的存儲器事務處理,每條數據線必須至少傳遞一個數據位。而脈衝時間長度則規定對於指定的事務處理,每條數據線必須傳遞的位數量。每個事務處理中的每條數據線只傳一個數據位的存儲技術,其脈衝時間長度為1。總的列存取粒度很簡單:列存取粒度=匯流排寬度×脈衝時間長度。

很多系統架構僅僅通過增加DRAM器件和存儲匯流排頻寬就能增加存儲系統的可用頻寬。畢竟,如果4個400MHz數據速率的連線可實現 1.6GHz的總峰值頻寬,那么8個連線將得到3.2GHz。增加一個DRAM器件,電路板上的連線以及ASIC的管腳就會增多,總峰值頻寬相應地倍增。

首要的是,架構師希望完全利用峰值頻寬,這已經達到他們通過物理設計存儲器匯流排所能達到的最大值。具有256位甚或512位存儲匯流排的圖形控制器已並不鮮見,這種控制器需要1,000個,甚至更多的管腳。封裝設計師、ASIC底層規劃工程師以及電路板設計工程師不能找到採用便宜的、商業上可行的方法來對這么多信號進行布線的矽片區域。僅僅增加匯流排寬度來獲得更高的峰值數據速率,會導致因為列存取粒度限制而降低有效頻寬。

假設某個特定存儲技術的脈衝時間長度等於1,對於一個存儲器處理,512位寬系統的存取粒度為512位(或者64位元組)。如果控制器只需要一小段數據,那么剩下的數據就被浪費掉,這就降低了系統的有效數據速率。例如,只需要存儲系統32位元組數據的控制器將浪費剩餘的32位元組,進而導致有效的數據速率等於50%的峰值速率。這些計算都假定脈衝時間長度為1。隨著存儲器接口數據速率增加的趨勢,大多數新技術的最低脈衝時間長度都大於1。

一種稱為核心預取的功能主要負責增加最小的脈衝時間長度。DRAM核心電路不能跟上I/O電路速度的速增。由於數據不能再連續地從核心中取出以確保控制器需求,核心通常為I/O提供比DRAM匯流排寬度更大的數據集。

核心傳輸足夠的數據到接口電路,或者從接口電路傳輸足夠的數據,以使接口電路保持足夠長時間的繁忙狀態,以便讓核心準備下一個操作。例如,假設DRAM核心每個納秒才能對操作回響一次。不過,接口可以支持每納秒兩位的數據速率。

DRAM核心每次操作取兩個數據位,而不是一個數據位,因而不必浪費接口一半的容量。在接口傳輸數據之後,核心已經準備好回響下一個請求,而不需增加延時。增加的核心預取導致最小脈衝時間長度增加為2,這將直接影響列存取粒度。

對於每個增加到匯流排寬度的額外信號,存儲器接口將傳輸兩個額外的數據位。因此具有最小脈衝時間長度為2的512位寬的存儲系統,其取粒度為 1,024位(128位元組)。很多系統對最小存取粒度的問題並不敏感,因為它們存儲大量的數據。不過,某些系統依賴存儲器系統提供小的數據單元,並獲益於更窄、更有效的存儲器技術。

隨著存儲技術向峰值數據速率發展,有效的數據速率變的越來越重要。在選擇存儲器時,設計師必須深入了解已公布的存儲器規範,並明白某個特定的技術特性將對套用設計產生怎樣的影響。存儲器系統設計師必須超越峰值數據速率規範,就像CPU設計師不再用千兆Hz作為唯一的性能衡量標準一樣。儘管對於存儲器接口而言,峰值數據速率依然是最終要的性能規範,但有效的數據速率已開始為系統設計師和架構師提供更大的空間。未來產品的性能將極大地取決於其存儲器系統的有效利用程度

選擇技巧

存儲器的類型將決定整個嵌入式系統的操作和性能,因此存儲器的選擇是一個非常重要的決策。無論系統是採用電池供電還是由市電供電,套用需求將決定存儲器的類型(易失性或非易失性)以及使用目的(存儲代碼、數據或者兩者兼有)。另外,在選擇過程中,存儲器的尺寸和成本也是需要考慮的重要因素。對於較小的系統,微控制器自帶的存儲器就有可能滿足系統要求,而較大的系統可能要求增加外部存儲器。為嵌入式系統選擇存儲器類型時,需要考慮一些設計參數,包括微控制器的選擇、電壓範圍、電池壽命、讀寫速度、存儲器尺寸、存儲器的特性、擦除/寫入的耐久性以及系統總成本。

選擇存儲器時應遵循的基本原則

1、內部存儲器與外部存儲器

一般情況下,當確定了存儲程式代碼和數據所需要的存儲空間之後,設計工程師將決定是採用內部存儲器還是外部存儲器。通常情況下,內部存儲器的性價比最高但靈活性最低,因此設計工程師必須確定對存儲的需求將來是否會增長,以及是否有某種途徑可以升級到代碼空間更大的微控制器。基於成本考慮,人們通常選擇能滿足套用要求的存儲器容量最小的微控制器,因此在預測代碼規模的時候要必須特別小心,因為代碼規模增大可能要求更換微控制器。目前市場上存在各種規模的外部存儲器器件,我們很容易通過增加存儲器來適應代碼規模的增加。有時這意味著以封裝尺寸相同但容量更大的存儲器替代現有的存儲器,或者在匯流排上增加存儲器。即使微控制器帶有內部存儲器,也可以通過增加外部串列EEPROM或快閃記憶體來滿足系統對非易失性存儲器的需求。

2、引導存儲器

在較大的微控制器系統或基於處理器的系統中,設計工程師可以利用引導代碼進行初始化。套用本身通常決定了是否需要引導代碼,以及是否需要專門的引導存儲器。例如,如果沒有外部的定址匯流排或串列引導接口,通常使用內部存儲器,而不需要專門的引導器件。但在一些沒有內部程式存儲器的系統中,初始化是操作代碼的一部分,因此所有代碼都將駐留在同一個外部程式存儲器中。某些微控制器既有內部存儲器也有外部定址匯流排,在這種情況下,引導代碼將駐留在內部存儲器中,而操作代碼在外部存儲器中。這很可能是最安全的方法,因為改變操作代碼時不會出現意外地修改引導代碼。在所有情況下,引導存儲器都必須是非易失性存儲器。

3、配置存儲器

對於現場可編程門陣列(FPGA)或片上系統(SoC),人們使用存儲器來存儲配置信息。這種存儲器必須是非易失性EPROM、EEPROM或快閃記憶體。大多數情況下,FPGA採用SPI接口,但一些較老的器件仍採用FPGA串列接口。串列EEPROM或快閃記憶體器件最為常用,EPROM用得較少。

4、程式存儲器

所有帶處理器的系統都採用程式存儲器,但設計工程師必須決定這個存儲器是位於處理器內部還是外部。在做出了這個決策之後,設計工程師才能進一步確定存儲器的容量和類型。當然有的時候,微控制器既有內部程式存儲器也有外部定址匯流排,此時設計工程師可以選擇使用它們當中的任何一個,或者兩者都使用。這就是為什麼為某個套用選擇最佳存儲器的問題,常常由於微控制器的選擇變得複雜起來,以及為什麼改變存儲器的規模也將導致改變微控制器的選擇的原因。如果微控制器既利用內部存儲器也利用外部存儲器,則內部存儲器通常被用來存儲不常改變的代碼,而外部存儲器用於存儲更新比較頻繁的代碼和數據。設計工程師也需要考慮存儲器是否將被線上重新編程或用新的可程式器件替代。對於需要重編程功能的套用,人們通常選用帶有內部快閃記憶體的微控制器,但帶有內部OTP或ROM和外部快閃記憶體或EEPROM的微控制器也滿足這個要求。為降低成本,外部快閃記憶體可用來存儲代碼和數據,但在存儲數據時必須小心避免意外修改代碼。

在大多數嵌入式系統中,人們利用快閃記憶體存儲程式以便線上升級固件。代碼穩定的較老的套用系統仍可以使用ROM和OTP存儲器,但由於快閃記憶體的通用性,越來越多的套用系統正轉向快閃記憶體。表1給出了程式存儲器類型的參數比較。

5、數據存儲器

與程式存儲器類似,數據存儲器可以位於微控制器內部,或者是外部器件,但這兩種情況存在一些差別。有時微控制器內部包含SRAM(易失性)和EEPROM(非易失)兩種數據存儲器,但有時不包含內部EEPROM,在這種情況下,當需要存儲大量數據時,設計工程師可以選擇外部的串列EEPROM或串列快閃記憶體器件。當然,也可以使用並行EEPROM或快閃記憶體,但通常它們只被用作程式存儲器。當需要外部高速數據存儲器時,通常選擇並行SRAM並使用外部串列EEPROM器件來滿足對非易失性存儲器的要求。一些設計還將快閃記憶體器件用作程式存儲器,但保留一個扇區作為數據存儲區。這種方法可以降低成本、空間並提供非易失性數據存儲器。針對非易失性存儲器要求,串列EEPROM器件支持I2C、SPI或微線(Microwire)通訊匯流排,而串列快閃記憶體通常使用SPI匯流排。由於寫入速度很快且帶有I2C和SPI串列接口,FRAM在一些系統中得到套用。

6、易失性和非易失性存儲器

存儲器可分成易失性存儲器或者非易失性存儲器,前者在斷電後將丟失數據,而後者在斷電後仍可保持數據。設計工程師有時將易失性存儲器與後備電池一起使用,使其表現猶如非易失性器件,但這可能比簡單地使用非易失性存儲器更加昂貴。然而,對要求存儲器容量非常大的系統而言,帶有後備電池的DRAM可能是滿足設計要求且性價比很高的一種方法。在有連續能量供給的系統中,易失性或非易失性存儲器都可以使用,但必須基於斷電的可能性做出最終決策。如果存儲器中的信息可以在電力恢復時從另一個信源中恢復出來,則可以使用易失性存儲器。選擇易失性存儲器與電池一起使用的另一個原因是速度。儘管非易失存儲器件可以在斷電時保持數據,但寫入數據(一個位元組、頁或扇區)的時間較長。

存儲器

存儲器7、串列存儲器和並行存儲器

在定義了套用系統之後,微控制器的選擇是決定選擇串列或並行存儲器的一個因素。對於較大的套用系統,微控制器通常沒有足夠大的內部存儲器,這時必須使用外部存儲器,因為外部定址匯流排通常是並行的,外部的程式存儲器和數據存儲器也將是並行的。較小的套用系統通常使用帶有內部存儲器但沒有外部地址匯流排的微控制器。如果需要額外的數據存儲器,外部串列存儲器件是最佳選擇。大多數情況下,這個額外的外部數據存儲器是非易失性的。根據不同的設計,引導存儲器可以是串列也可以是並行的。如果微控制器沒有內部存儲器,並行的非易失性存儲器件對大多數套用系統而言是正確的選擇。但對一些高速套用,可以使用外部的非易失性串列存儲器件來引導微控制器,並允許主代碼存儲在內部或外部高速SRAM中。

8、EEPROM與快閃記憶體

存儲器技術的成熟使得RAM和ROM之間的界限變得很模糊,如今有一些類型的存儲器(如EEPROM和快閃記憶體)組合了兩者的特性。這些器件像RAM一樣進行讀寫,並像ROM一樣在斷電時保持數據,它們都可電擦除且可程式,但各自有它們優缺點。從軟體角度看,獨立的EEPROM和快閃記憶體器件是類似的,兩者主要差別是EEPROM器件可以逐位元組地修改,而快閃記憶體器件只支持扇區擦除以及對被擦除單元的字、頁或扇區進行編程。對快閃記憶體的重新編程還需要使用SRAM,因此它要求更長的時間內有更多的器件在工作,從而需要消耗更多的電池能量。設計工程師也必須確認在修改數據時有足夠容量的SRAM可用。存儲器密度是決定選擇串列EEPROM或者快閃記憶體的另一個因素。市場上目前可用的獨立串列EEPROM器件的容量在128KB或以下,獨立快閃記憶體器件的容量在32KB或以上。如果把多個器件級聯在一起,可以用串列EEPROM實現高於128KB的容量。很高的擦除/寫入耐久性要求促使設計工程師選擇EEPROM,因為典型的串列EEPROM可擦除/寫入100萬次。快閃記憶體一般可擦除/寫入1萬次,只有少數幾種器件能達到10萬次。大多數快閃記憶體器件的電壓範圍為2.7V到3.6V。如果不要求位元組定址能力或很高的擦除/寫入耐久性,在這個電壓範圍內的套用系統採用快閃記憶體,可以使成本相對較低。

網路存儲器

網路存儲器9、EEPROM與FRAM

EEPROM和FRAM的設計參數類似,但FRAM的可讀寫次數非常高且寫入速度較快。然而通常情況下,用戶仍會選擇EEPROM而不是FRAM,其主要原因是成本(FRAM較為昂貴)、質量水平和供貨情況。設計工程師常常使用成本較低的串列EEPROM,除非耐久性或速度是強制性的系統要求。DRAM和SRAM都是易失性存儲器,儘管這兩種類型的存儲器都可以用作程式存儲器和數據存儲器,但SRAM主要用於數據存儲器。DRAM與SRAM之間的主要差別是數據存儲的壽命。只要不斷電,SRAM就能保持其數據,但DRAM只有極短的數據壽命,通常為4毫秒左右。與SRAM相比,DRAM似乎是毫無用處的,但位於微控制器內部的DRAM控制器使DRAM的性能表現與SRAM一樣。DRAM控制器在數據消失之前周期性地刷新所存儲的數據,所以存儲器的內容可以根據需要保持長時間。由於比特成本低,DRAM通常用作程式存儲器,所以有龐大存儲要求的套用可以從DRAM獲益。它的最大缺點是速度慢,但計算機系統使用高速SRAM作為高速緩衝存儲器來彌補DRAM的速度缺陷。

可以使用任何類型的存儲器來滿足嵌入式系統的要求,但終端套用和總成本要求通常是影響我們做出決策的主要因素。有時,把幾個類型的存儲器結合起來使用能更好地滿足套用系統的要求。例如,一些PDA設計同時使用易失性存儲器和非易失性存儲器作為程式存儲器和數據存儲器。把永久的程式保存在非易失性ROM中,而把由用戶下載的程式和數據存儲在有電池支持的易失性DRAM中。不管選擇哪種存儲器類型,在確定將被用於最終套用系統的存儲器之前,設計工程師必須仔細折中考慮各種設計因素。

測試

存儲器測試的目的是確認在存儲設備中的每一個存儲位置都在工作。換一句話說,如果你把數 50存儲在一個具體的地址,你希望可以找到存儲在那裡的那個數,直到另一個數

寫入。任何存儲器測試的基本方法是,往存儲器寫入一些數據,然後根據記憶體設備的地址,校驗讀回的數據。如果所有讀回的數據和那些寫入的數據是一樣的,那么就可以說

存儲設備通過了測試。只有通過認真選擇的一組數據你才可以確信通過的結果是有意義的。

當然,像剛才描述的有儲器的測試不可避免地具有破壞性。在記憶體測試過程中,你必須覆蓋它原先的內容。因為重寫非易失性存儲器內容通常來說是不可行的,這一部分描述

的測試通常只適用於 RAM 的測試。

在學習具體的測試算法之前,你應該了解可能遇到的各種存儲器問題。在軟體工程師中一個普遍的誤解是,大部分的存儲器問題發生在晶片的內部。儘管這類問題一度是一個

主要的問題,但是它們在日益減少。存儲設備的製造商們對於每一個批量的晶片都進行了各種產品後期測試。因此,即使某一個批量有問題,其中某個壞晶片進人到你的系統

的可能性是微乎其微的。

你可能遇到的一種類型的存儲晶片問題是災難性的失效。這通常是在加工好之後晶片受到物理或者是電子損傷造成的。災難性失效是少見的,通常影響晶片中的大部分。因為

一大片區域受到影響,所以災難性的失效當然可以被合適的測試算法檢測到。

存儲器出問題比較普遍的原因是電路板故障。典型的電路板故障有:

(1)在處理器與存儲設備之間的連線問題

(2)無存儲器晶片

(3)存儲器晶片的不正確插人

最好有三個獨立的測試:數據匯流排的測試、地址匯流排的測試以及設備的測試。前面兩個測試針對電子連線的問題以及晶片的不正確插入;第三個測試更傾向於檢測晶片的有無

以及災難性失效。作為一個意外的結果,設備的測試也可以發現控制匯流排的問題,儘管它不能提供關於問題來源的有用信息。

執行這三個測試的順序是重要的。正確的順序是:首先進行數據匯流排測試,接著是地址匯流排測試,最後是設備測試。那是因為地址匯流排測試假設數據匯流排在正常工作,除非數

據匯流排和地址匯流排已知是正常的,否則設備測試便毫無意義。如果任何測試失敗,你都應該和一個硬體工程師一起確定問題的來源。通過查看測試失敗處的數據值或者地址,

應該能夠迅速地找出電路板上的問題。

1,數據匯流排測試

我們首先要測試的就是數據匯流排。我們需要確定任何由處理器放置在數據匯流排上的值都被另一端的存儲設備正確接收。最明顯的測試方法就是寫人所有可能的數據值並且驗證

存儲設備成功地存儲了每一個。然而,那並不是最有效率的測試方法。一個更快的測試方法是一次測試匯流排上的一位。如果每一個數據上可被設定成為 0 和 1,而不受其他數

據位的影響,那么數據匯流排就通過了測試。

2,地址匯流排測試

在確認數據匯流排工作正常之後,你應該接著測試地址匯流排。記住地址匯流排的問題將導致存儲器位置的重疊。有很多可能重疊的地址。然而,不必要測試每一個可能的組合。你

應該努力在測試過程中分離每一個地址位。你只需要確認每一個地址線的管腳都可以被設定成 0和 1,而不影響其他的管腳。

3,設備測試

一旦你知道地址和數據匯流排是正確的,那么就有必要測試存儲設備本身的完整性。要確認的是設備中的每一位都能夠保持住 0和 1。這個測試實現起來十分簡單,但是它花費的時間比執行前面兩項測試花費的總時間還要長。

對於一個完整的設備測試,你必須訪問(讀和寫)每一個存儲位置兩次。你可以自由地選擇任何數據作為第一步測試的數據,只要在進行第二步測試的時候把這個值求反即可

。因為存在沒有存儲器晶片的可能性,所以最好選擇一組隨著地址變化(但是不等於地址)的數。

發展趨勢

一、 產品技術發展趨勢

存儲器晶片按存取方式(讀寫方式)可分為隨機存取存儲器晶片(RAM)和唯讀存儲器晶片(ROM)。ROM中的信息只能被讀出,而不能被操作者修改或刪除,故一般用於存放固定的程式,如監控程式、彙編程式等,以及存放各種表格。RAM主要用來存放各種現場的輸入、輸出數據,中間計算結果,以及與外部存儲器交換信息和作堆疊用。它的存儲單元根據具體需要可以讀出,也可以寫入或改寫。由於RAM由電子器件組成,所以只能用於暫時存放程式和數據,一旦關閉電源或發生斷電,其中的數據就會丟失。現在的RAM多為MOS型半導體電路,它分為靜態和動態兩種。靜態RAM是靠雙穩態觸發器來記憶信息的;動態RAM是靠MOS電路中的柵極電容來記憶信息的。由於電容上的電荷會泄漏,需要定時給與補充,所以動態RAM需要設定刷新電路。但動態RAM比靜態RAM集成度高、功耗低,從而成本也低,適於作大容量存儲器。

按照不同的技術,存儲器晶片可以細分為EPROM、EEPROM、SRAM、DRAM、FLASH、MASK ROM和FRAM等。存儲器技術是一種不斷進步的技術,隨著各種專門套用不斷提出新的要求,新的存儲器技術也層出不窮,每一種新技術的出現都會使某種現存的技術走進歷史,因為開發新技術的初衷就是為了消除或減弱某種特定存儲器產品的不足之處。例如,快閃記憶體技術脫胎於EEPROM,它的一個主要用途就是為了取代用於PC機BIOS的EEPROM晶片,以便方便地對這種計算機中最基本的代碼進行更新。儘管目前非揮發性存儲器中最先進的就是快閃記憶體,但技術卻並未就此停步。生產商們正在開發多種新技術,以便使快閃記憶體也擁有像DRAM和SDRAM那樣的高速、低價、壽命長等特點。總之,存儲器技術將會繼續發展,以滿足不同的套用需求。就PC市場來說,更高密度、更大頻寬、更低功耗、更短延遲時間、更低成本的主流DRAM技術將是不二之選。而在其它非揮發性存儲器領域,供應商們正在研究快閃記憶體之外的各種技術,以便滿足不同套用的需求,未來必將有更多更新的存儲器晶片技術不斷湧現。

二、產品市場發展趨勢

1、FLASH的套用越來越廣泛

隨著FLASH在通信領域、消費領域、計算機領域的普遍套用,未來FLASH必將成為發展最快、最有市場潛力的存儲器晶片產品。在電信領域,我國電信運營商已經開通了彩信業務,以MOTOROLA 388和多普達為代表的“PDA+手機”已經得到越來越多的消費者的青睞。這些多功能行動電話需要更大的存儲容量,以存儲更大的程式和更多的數據。在行動電話中FLASH還有一個更大的套用——可拆卸式快閃記憶體卡。下一代以信息為中心的手機將對快閃記憶體卡有很大的需求,手機使用者可用快閃記憶體卡來儲存欲在無線網路中傳送的影像,或作檔案備份或其它用途。目前有多家手機製造商宣布計畫在未來的手機上採用快閃記憶體卡,包括Sony Ericsson的P800、NTT DoCoMo的i-shot mova D25li、Lexar Media的Secure Digital快閃記憶體卡等。

在消費領域,FLASH主要套用在PDA、數位相機、數碼攝象機、MP3等數字電子產品,在這些產品中的套用,更多的是以FDD、Compact Flash、SmartMedia、clik、Microdrive與Memory Stick等快閃記憶體卡形式。隨著經濟的發展及科技的進步,消費者對數位相機、數碼攝象機的認同感越來越強,已掀起了一股數字消費潮流,數字消費電子產品對FLASH的需求潛力很大。在計算機領域,FLASH最早的套用是在BIOS中取代PROM和EPROM以適應消費者對計算機的升級需求。另外,基於USB的移動快閃記憶體以其大容量、易攜帶、速度快等優勢,受到越來越多的消費者的青睞,可以預期移動快閃記憶體市場將會出現爆炸式的增長,對FLASH的市場需求前景非常光明。

2、基於FLASH的移動存儲器逐漸取代軟碟

移動快閃記憶體不僅具有易於操作和方便攜帶的特點,同時,移動快閃記憶體還具有高速、輕便、技術先進、大存儲量的特點,因此移動快閃記憶體不僅將成為個人存儲套用的主要產品,而且還將在各類企業、學校及行業用戶領域具有廣泛的套用前景,必將成為未來存儲市場的主流。自從朗科公司在國內最先推出快閃記憶體產品“朗科優盤”之後,這種新型的移動儲存產品就將矛頭直接指向了計算機最老的配置之一——軟碟機。朗科公司最早提出了“取代軟碟軟碟機”的口號。而市場似乎也應合了這一趨勢。

網路存儲器

網路存儲器2002年剛過新年,Intel公司就已經對外宣布將在新款處理器中徹底停止對軟碟機的支持。而三星公司也宣布要在所有三星新款電腦中以USB移動存儲盤徹底取代軟碟機。占據磁碟50%市場的索尼在1個月前也以極快的速度成立了一個閃盤事業部,專門負責自有品牌閃盤的推廣工作。國內的IT廠商聯想、方正也先後宣布旗下V系列筆記本電腦、商祺9000電腦選擇朗科優盤為標準配置,從而徹底廢除了軟碟機。其實移動存儲盤取代軟碟機,從任何一個方面來看都是理所當然的。從技術上來看,快閃記憶體的讀取速度和容量大大高於軟碟機,使用壽命也更長。有些移動存儲盤還具有抗震性能。軟碟不僅體積相對較大,而且讀取速度慢、使用壽命短、容量小。從價格上看,32M的快閃記憶體盤是軟碟機的兩倍左右,可是性能等方面卻是後者的20-30倍。據了解,2002年快閃記憶體的市場容量將達到150萬片。對於一種新產品而言,這樣的市場容量是誘人的。因此,聯想、清華同方等也受不住誘惑,相繼推出自己的快閃記憶體產品:魔盤和惠存星鑽。而國外的LG和美國百事靈也相繼進入了我國移動快閃記憶體市場。

3、DDR SDRAM將逐步取代RDRAM成為市場主流

存儲器晶片市場發展趨勢有兩大陣營:RDRAM(RAMBUS)和DDR與PC133。無論哪種產品,若想在市場獲得成功,除了技術外最關鍵的是能否獲得產業鏈中晶片組、OEM廠商和組裝電腦廠商大力支持。RDRAM出貨量最多的三星電子公司稱,RDRAM的需求量在過去幾個月中大幅增加,這種存儲器晶片晶片預計將占這家韓國公司DRAM全年產量的10%以上。中國我國台灣省矽統公司2002年7月份推出了R658晶片組,該晶片組支持RDRAM,包括新的1066MHz晶片。但業內最重要的晶片組廠商英特爾於2002年8月證實,該公司將逐漸停止生產支持Rambus公司RDRAM存儲器晶片的個人電腦和工作站,取而代之的是DDR和SDRAM存儲器晶片。這標誌著Rambus公司和英特爾一度非常密切的夥伴關係走到了盡頭。英特爾曾試圖將RDRAM存儲器晶片作為下一代個人電腦的主流存儲器晶片,但未獲成功。英特爾公司聲稱所有的新晶片組將只支持DDR存儲器晶片。支持RDRAM存儲器晶片的英特爾台式850晶片組將一直延用至2005年,但其後將不會再推出採用RDRAM存儲器晶片的新產品。其850系列將在幾個月內進行升級,以支持新的1066MHz RDRAM存儲器晶片晶片,但不會進一步升級850系列,使其支持1200MHz或1300MHz的RDRAM存儲器晶片。

由於採用DDR存儲器晶片的兩款新的工作站晶片組,即採用Xeon雙處理器的Placer晶片組和採用Xeon單處理器的Granite Bay晶片組將在2002年第四季度面市。它們出現之日就是860系列消失之時,因此沒有必要升級860系列,使其支持1066MHz的RDRAM。新款Placer晶片組將支持PCI-X和AGP8X,並可升級至支持DDR266,將來可能會支持DDR333。現存的845系列晶片組將在第四季度升級至支持DDR333。DDR SDRAM由於得到了產業鏈的支持,將逐漸取代RDRAM成為市場主流。

虛擬存儲器

網路存儲器

網路存儲器虛擬存儲器的核心思路:根據程式運行的局部性原理,一個程式運行時,在一小段時間內,只會用到程式和數據的很小一部分,僅把這部分程式和數據裝入主存儲器即可。更多的部分可以在用到時隨時從磁碟調入主存。在作業系統和相應硬體的支持下,數據在磁碟和主存之間按程式運行的需要自動成批量地完成交換。

虛擬存儲器中經常使用兩種基本管理技術:段式存儲管理,頁式存儲管理。

核心問題都在於處理數據的存放與調度。

一、段式存儲管理

1、段:通常一個大的程式是由在邏輯上、處理功能上有一定的獨立性的程式段組成的,可用段名或段號來標明程式段,每個段的長度是隨意的,由指令的條數確定。

2、段式存儲管理:當運行有若干段組成的程式時,把主存按段進行分配與管理,以段作為信息單位,實現在主存-輔存之間的傳送。這種管理方式稱為段式存儲管理。

3、邏輯地址的組成:段式存儲管理的核心問題是:變邏輯地址中的邏輯段號為主存中的一個存儲區的起始地址,這是通過在系統中(一般在主存中)設定一個段表來完成。段表由多個表項組成:段起始地址,段長,段的裝入位。

二、頁式存儲管理

1、頁:把虛擬邏輯地址空間和主存實際物理地址空間都劃分容量相等(為2的冪)的大小區域,稱為頁。所有的地址都可以用頁號拼接頁內地址來表示。

2、頁式存儲管理:在一個計算機系統中頁的長度是人為劃分的,並通過分頁方式進行存儲器管理,實現以頁為單位來完成在虛存和主存之間信息交換,稱為頁式存儲管理。

計算機硬體知識解析

| 在我們的日常生活中,計算機一般指電子計算機中用的個人電腦。計算機是一種能夠按照指令對各種數據和信息進行自動加工和處理的電子設備。它由多個零配件組成,如中央處理器、主機板、記憶體、電源、顯示卡等。接收、處理和提供數據的一種裝置,通常由輸入輸出設備、存儲器、運算和邏輯部件以及控制器組成。在此我們的任務是為這些複雜的硬體做出詳細的功能性能的解析,讓更多的人可以更直接的認識到這些專業的硬體屬性。 |