結構

圖1

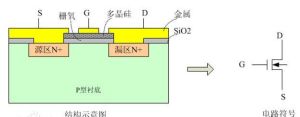

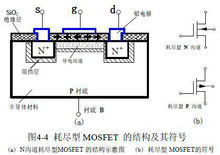

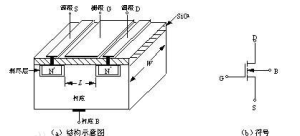

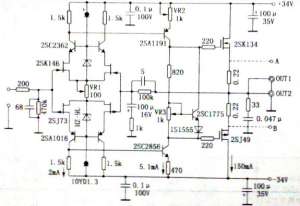

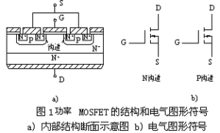

圖1圖1是常見的N溝道增強型MOSFET的基本結構圖。為了改善某些參數的特性,如提高工作電流、提高工作電壓、降低導通電阻、提高開關特性等有不同的結構及工藝,構成所謂VMOS、DMOS、TMOS等結構。雖然有不同的結構,但其工作原理是相同的,這裡就不一一介紹了。

工作原理

工作原理

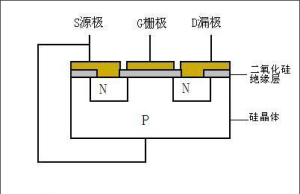

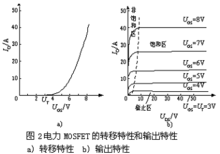

工作原理若先不接VGS(即VGS=0),在D與S極之間加一正電壓VDS,漏極D與襯底之間的PN結處於反向,因此漏源之間不能導電。如果在柵極G與源極S之間加一電壓VGS。此時可以將柵極與襯底看作電容器的兩個極板,而氧化物絕緣層作為電容器的介質。當加上VGS時,在絕緣層和柵極界面上感應出正電荷,而在絕緣層和P型襯底界面上感應出負電荷。這層感應的負電荷和P型襯底中的多數載流子(空穴)的極性相反,所以稱為“反型層”,這反型層有可能將漏與源的兩N型區連線起來形成導電溝道。當VGS電壓太低時,感應出來的負電荷較少,它將被P型襯底中的空穴中和,因此在這種情況時,漏源

工作原理

工作原理 工作原理

工作原理 工作原理

工作原理詳細信息

概述

從名字表面的角度來看MOSFET的命名,事實上會讓人得到錯誤的印象。因為MOSFET里代表“metal”的第一個字母M在當下大部分同類的元件里是不存在的。早期MOSFET的柵極(gateelectrode)使用金屬作為其材料,但隨著半導體技術的進步,隨後MOSFET柵極使用多晶矽取代了金屬。在處理器中,多晶矽柵已經不是主流技術,從英特爾採用45納米線寬的P1266處理器開始,柵極開始重新使用金屬。。

MOSFET在概念上屬於“絕緣柵極場效電晶體”(Insulated-GateFieldEffectTransistor,IGFET),而IGFET的柵極絕緣層有可能是其他物質而非MOSFET使用的氧化層。有些人在提到擁有多晶矽柵極的場效電晶體元件時比較喜歡用IGFET,但是這些IGFET多半指的是MOSFET。

MOSFET里的氧化層位於其通道上方,依照其操作電壓的不同,這層氧化物的厚度僅有數十至數百埃(Å)不等,通常材料是二氧化矽(silicondioxide,SiO2),不過有些新的進階製程已經可以使用如氮氧化矽(siliconoxynitride,SiON)做為氧化層之用。

今日半導體元件的材料通常以矽(silicon)為首選,但是也有些半導體公司發展出使用其他半導體材料的製程,當中最著名的例如IBM使用矽與鍺(germanium)的混合物所發展的矽鍺製程(silicon-germaniumprocess,SiGeprocess)。而可惜的是很多擁有良好電性的半導體材料,如砷化鎵(galliumarsenide,GaAs),因為無法在表面長出品質夠好的氧化層,所以無法用來製造MOSFET元件。

當一個夠大的電位差施於MOSFET的柵極與源極(source)之間時,電場會在氧化層下方的半導體表面形成感應電荷,而這時所謂的“反型層”(inversionchannel)就會形成。通道的極性與其漏極(drain)與源極相同,假設漏極和源極是N型,那么通道也會是N型。通道形成後,MOSFET即可讓電流通過,而依據施於柵極的電壓值不同,可由MOSFET的通道流過的電流大小亦會受其控制而改變。

電路符號

電路符號

電路符號 MOSFET

MOSFET MOSFET

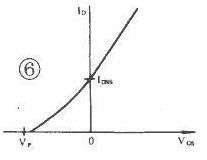

MOSFET這樣,MOSFET就有了4鍾類型:P溝道增強型,P溝道耗盡型,N溝道增強型,N溝道耗盡型,它們的電路符號和套用特性曲線如下圖所示。

操作原理

MOSFET的核心:金屬—氧化層—半導體電容

金屬—氧化層—半導體結構MOSFET在結構上以一個金屬—氧化層—半導體的電容為核心(如前所述,今日的MOSFET多半以多晶矽取代金屬作為其柵極材料),氧化層的材料多半是二氧化矽,其下是作為基極的矽,而其上則是作為柵極的多晶矽。這樣子的結構正好等於一個電容器(capacitor),氧化層扮演電容器中介電質(dielectricmaterial)的角色,而電容值由氧化層的厚度與二氧化矽的介電常數(dielectricconstant)來決定。柵極多晶矽與基極的矽則成為MOS電容的兩個端點。

當一個電壓施加在MOS電容的兩端時,半導體的電荷分布也會跟著改變。考慮一個P型的半導體(空穴濃度為NA)形成的MOS電容,當一個正的電壓VGB施加在柵極與基極端(如圖)時,空穴的濃度會減少,電子的濃度會增加。當VGB夠強時,接近柵極端的電子濃度會超過空穴。這個在P型半導體中,電子濃度(帶負電荷)超過空穴(帶正電荷)濃度的區域,便是所謂的反轉層(inversionlayer)。

MOS電容的特性決定了MOSFET的操作特性,但是一個完整的MOSFET結構還需要一個提供多數載流子(majoritycarrier)的源極以及接受這些多數載流子的漏極。

結構

結構

結構對這個NMOS而言,真正用來作為通道、讓載流子通過的只有MOS電容正下方半導體的表面區域。當一個正電壓施加在柵極上,帶負電的電子就會被吸引至表面,形成通道,讓N型半導體的多數載流子—電子可以從源極流向漏極。如果這個電壓被移除,或是放上一個負電壓,那么通道就無法形成,載流子也無法在源極與漏極之間流動。

假設操作的對象換成PMOS,那么源極與漏極為P型、基體則是N型。在PMOS的柵極上施加負電壓,則半導體上的空穴會被吸引到表面形成通道,半導體的多數載流子—空穴則可以從源極流向漏極。假設這個負電壓被移除,或是加上正電壓,那么通道無法形成,一樣無法讓載流子在源極和漏極間流動。

特別要說明的是,源極在MOSFET里的意思是“提供多數載流子的來源”。對NMOS而言,多數載流子是電子;對PMOS而言,多數載流子是空穴。相對的,漏極就是接受多數載流子的端點。

主要參數

場效應管的參數很多,包括直流參數、交流參數和極限參數,但一般使用時關注以下主要參數:

1、IDSS—飽和漏源電流。是指結型或耗盡型絕緣柵場效應管中,柵極電壓UGS=0時的漏源電流。

2、UP—夾斷電壓。是指結型或耗盡型絕緣柵場效應管中,使漏源間剛截止時的柵極電壓。

3、UT—開啟電壓。是指增強型絕緣柵場效管中,使漏源間剛導通時的柵極電壓。

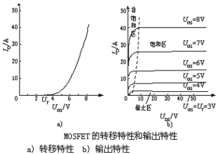

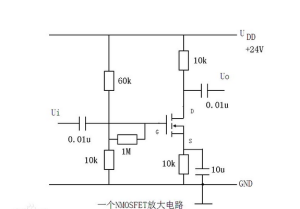

4、gM—跨導。是表示柵源電壓UGS—對漏極電流ID的控制能力,即漏極電流ID變化量與柵源電壓UGS變化量的比值。gM是衡量場效應管放大能力的重要參數。

5、BUDS—漏源擊穿電壓。是指柵源電壓UGS一定時,場效應管正常工作所能承受的最大漏源電壓。這是一項極限參數,加在場效應管上的工作電壓必須小於BUDS。

6、PDSM—最大耗散功率。也是一項極限參數,是指場效應管性能不變壞時所允許的最大漏源耗散功率。使用時,場效應管實際功耗應小於PDSM並留有一定餘量。

7、IDSM—最大漏源電流。是一項極限參數,是指場效應管正常工作時,漏源間所允許通過的最大電流。場效應管的工作電流不應超過IDSM。

型號命名

中國命名法

有兩種命名方法。

場效應管通常有下列兩種命名方法。

第一種命名方法是使用“中國半導體器件型號命名法”的第3、第4和第5部分來命名,其中的第3部分用字母CS表示場效應管,第4部分用阿拉伯數字表示器件序號,第5部分用漢語拼音字母表示規格號。例如CS2B、CS14A、CS45G等。

第二種命名方法與雙極型三極體相同,第一位用數字代表電極數;第二位用字母代表極性(其中D是N溝道,C是P溝道);第三位用字母代表類型(其中J代表結型場效應管,O代表絕緣柵場效應管)。例如,3DJ6D是N溝道結型場效應三極體,3D06C是N溝道絕緣柵型場效應三極體。

日本命名法

日本生產的半導體分立器件,由五至七部分組成。通常只用到前五個部分,其各部分的符號意義如下:

第一部分:用數字表示器件有效電極數目或類型。0-光電(即光敏)二極體三極體及上述器件的組合管、1-二極體、2三極或具有兩個pn結的其他器件、3-具有四個有效電極或具有三個pn結的其他器件、┄┄依此類推。

第二部分:日本電子工業協會JEIA註冊標誌。S-表示已在日本電子工業協會JEIA註冊登記的半導體分立器件。

第三部分:用字母表示器件使用材料極性和類型。A-PNP型高頻管、B-PNP型低頻管、C-NPN型高頻管、D-NPN型低頻管、F-P控制極可控矽、G-N控制極可控矽、H-N基極單結電晶體、J-P溝道場效應管、K-N溝道場效應管、M-雙向可控矽。

第四部分:用數字表示在日本電子工業協會JEIA登記的順序號。兩位以上的整數-從“11”開始,表示在日本電子工業協會JEIA登記的順序號;不同公司的性能相同的器件可以使用同一順序號;數字越大,越是近期產品。

第五部分:用字母表示同一型號的改進型產品標誌。A、B、C、D、E、F表示這一器件是原型號產品的改進產品。

如2SK134為N溝道MOSFET,2SJ49為P溝道MOSFET。

套用優勢

MOSFET

MOSFET2、有些場效應管的源極和漏極可以互換使用,柵壓也可正可負,靈活性比雙極電晶體好。

3、場效應管是利用多數載流子導電,所以稱之為單極型器件,而雙極結型電晶體是即有多數載流子,也利用少數載流子導電。因此被稱之為雙極型器件。

4、場效應管能在很小電流和很低電壓的條件下工作,而且它的製造工藝可以很方便地把很多場效應管集成在一塊矽片上,因此場效應管在大規模積體電路中得到了廣泛的套用。

MOSFET

MOSFET由於MOSFET元件的性能逐漸提升,除了傳統上套用於諸如微處理器、微控制器等數位信號處理的場合上,也有越來越多模擬信號處理的積體電路可以用MOSFET來實現,以下分別介紹這些套用。

數字電路

數字科技的進步,如微處理器運算效能不斷提升,帶給深入研發新一代MOSFET更多的動力,這也使得MOSFET本身的操作速度越來越快,幾乎成為各種半導體主動元件中最快的一種。MOSFET在數位訊號處理上最主要的成功來自CMOS邏輯電路的發明,這種結構最大的好處是理論上不會有靜態的功率損耗,只有在邏輯門(logicgate)的切換動作時才有電流通過。CMOS邏輯門最基本的成員是CMOS反相器(inverter),而所有CMOS邏輯門的基本操作都如同反相器一樣,在邏輯轉換的瞬間同一時間內必定只有一種電晶體(NMOS或是PMOS)處在導通的狀態下,另一種必定是截止狀態,這使得從電源端到接地端不會有直接導通的路徑,大量節省了電流或功率的消耗,也降低了積體電路的發熱量。

MOSFET在數字電路上套用的另外一大優勢是對直流(DC)信號而言,MOSFET的柵極端阻抗為無限大(等效於開路),也就是理論上不會有電流從MOSFET的柵極端流向電路里的接地點,而是完全由電壓控制柵極的形式。這讓MOSFET和他們最主要的競爭對手BJT相較之下更為省電,而且也更易於驅動。在CMOS邏輯電路里,除了負責驅動晶片外負載(off-chipload)的驅動器(driver)外,每一級的邏輯門都只要面對同樣是MOSFET的柵極,如此一來較不需考慮邏輯門本身的驅動力。相較之下,BJT的邏輯電路(例如最常見的TTL)就沒有這些優勢。MOSFET的柵極輸入電阻無限大對於電路設計工程師而言亦有其他優點,例如較不需考慮邏輯門輸出端的負載效應(loadingeffect)。

模擬電路

有一段時間,MOSFET並非模擬電路設計工程師的首選,因為模擬電路設計重視的性能參數,如電晶體的轉導(transconductance)或是電流的驅動力上,MOSFET不如BJT來得適合模擬電路的需求。但是隨著MOSFET技術的不斷演進,今日的CMOS技術也已經可以符合很多模擬電路的規格需求。再加上MOSFET因為結構的關係,沒有BJT的一些致命缺點,如熱破壞(thermalrunaway)。另外,MOSFET線上性區的壓控電阻特性亦可在積體電路里用來取代傳統的多晶矽電阻(polyresistor),或是MOS電容本身可以用來取代常用的多晶矽—絕緣體—多晶矽電容(PIPcapacitor),甚至在適當的電路控制下可以表現出電感(inductor)的特性,這些好處都是BJT很難提供的。也就是說,MOSFET除了扮演原本電晶體的角色外,也可以用來作為模擬電路中大量使用的被動元件(passivedevice)。這樣的優點讓採用MOSFET實現模擬電路不但可以滿足規格上的需求,還可以有效縮小晶片的面積,降低生產成本。

隨著半導體製造技術的進步,對於整合更多功能至單一晶片的需求也跟著大幅提升,此時用MOSFET設計模擬電路的另外一個優點也隨之浮現。為了減少在印刷電路板(PrintedCircuitBoard,PCB)上使用的積體電路數量、減少封裝成本與縮小系統的體積,很多原本獨立的類比晶片與數位晶片被整合至同一個晶片內。MOSFET原本在數位積體電路上就有很大的競爭優勢,在類比積體電路上也大量採用MOSFET之後,把這兩種不同功能的電路整合起來的困難度也顯著的下降。另外像是某些混合信號電路(Mixed-signalcircuits),如類比/數位轉換器(Analog-to-DigitalConverter,ADC),也得以利用MOSFET技術設計出效能更好的產品。

還有一種整合MOSFET與BJT各自優點的製程技術:BiCMOS(Bipolar-CMOS)也越來越受歡迎。BJT元件在驅動大電流的能力上仍然比一般的CMOS優異,在可靠度方面也有一些優勢,例如不容易被“靜電放電”(ESD)破壞。所以很多同時需要復噪聲號處理以及強大電流驅動能力的積體電路產品會使用BiCMOS技術來製作。

尺寸縮放

過去數十年來,MOSFET的尺寸不斷地變小。早期的積體電路MOSFET製程里,通道長度約在幾個微米(micrometer)的等級。但是到了今日的積體電路製程,這個參數已經縮小了幾十倍甚至超過一百倍。2006年初,Intel開始以65納米(nanometer)的技術來製造新一代的微處理器,實際的元件通道長度可能比這個數字還小一些。至90年代末,MOSFET尺寸不斷縮小,讓積體電路的效能大大提升,而從歷史的角度來看,這些技術上的突破和半導體製程的進步有著密不可分的關係。

為何要把MOSFET的尺寸縮小

基於以下幾個理由,我們希望MOSFET的尺寸能越小越好。第一,越小的MOSFET象徵其通道長度減少,讓通道的等效電阻也減少,可以讓更多電流通過。雖然通道寬度也可能跟著變小而讓通道等效電阻變大,但是如果能降低單位電阻的大小,那么這個問題就可以解決。其次,MOSFET的尺寸變小意味著柵極面積減少,如此可以降低等效的柵極電容。此外,越小的柵極通常會有更薄的柵極氧化層,這可以讓前面提到的通道單位電阻值降低。不過這樣的改變同時會讓柵極電容反而變得較大,但是和減少的通道電阻相比,獲得的好處仍然多過壞處,而MOSFET在尺寸縮小後的切換速度也會因為上面兩個因素加總而變快。第三個理由是MOSFET的面積越小,製造晶片的成本就可以降低,在同樣的封裝里可以裝下更高密度的晶片。一片積體電路製程使用的晶圓尺寸是固定的,所以如果晶片面積越小,同樣大小的晶圓就可以產出更多的晶片,於是成本就變得更低了。

雖然MOSFET尺寸縮小可以帶來很多好處,但同時也有很多負面效應伴隨而來。

MOSFET的尺寸縮小後出現的困難

把MOSFET的尺寸縮小到一微米以下對於半導體製程而言是個挑戰,不過新挑戰多半來自尺寸越來越小的MOSFET元件所帶來過去不曾出現的物理效應。

次臨限傳導

由於MOSFET柵極氧化層的厚度也不斷減少,所以柵極電壓的上限也隨之變少,以免過大的電壓造成柵極氧化層崩潰(breakdown)。為了維持同樣的性能,MOSFET的臨界電壓也必須降低,但是這也造成了MOSFET越來越難以完全關閉。也就是說,足以造成MOSFET通道區發生弱反轉的柵極電壓會比從前更低,於是所謂的次臨限電流(subthresholdcurrent)造成的問題會比過去更嚴重,特別是今日的積體電路晶片所含有的電晶體數量劇增,在某些VLSI的晶片,次臨限傳導造成的功率消耗竟然占了總功率消耗的一半以上。

不過反過來說,也有些電路設計會因為MOSFET的次臨限傳導得到好處,例如需要較高的轉導/電流轉換比(transconductance-to-currentratio)的電路里,利用次臨限傳導的MOSFET來達成目的的設計也頗為常見。

晶片內部連線導線的寄生電容效應

傳統上,CMOS邏輯門的切換速度與其元件的柵極電容有關。但是當柵極電容隨著MOSFET尺寸變小而減少,同樣大小的晶片上可容納更多電晶體時,連線這些電晶體的金屬導線間產生的寄生電容效應就開始主宰邏輯門的切換速度。如何減少這些寄生電容,成了晶片效率能否向上突破的關鍵之一。

晶片發熱量增加

當晶片上的電晶體數量大幅增加後,有一個無法避免的問題也跟著發生了,那就是晶片的發熱量也大幅增加。一般的積體電路元件在高溫下操作可能會導致切換速度受到影響,或是導致可靠度與壽命的問題。在一些發熱量非常高的積體電路晶片如微處理器,需要使用外加的散熱系統來緩和這個問題。

在功率電晶體(PowerMOSFET)的領域裡,通道電阻常常會因為溫度升高而跟著增加,這樣也使得在元件中pn-接面(pn-junction)導致的功率損耗增加。假設外置的散熱系統無法讓功率電晶體的溫度保持在夠低的水平,很有可能讓這些功率電晶體遭到熱破壞(thermalrunaway)的命運。

柵極氧化層漏電流增加

柵極氧化層隨著MOSFET尺寸變小而越來越薄,主流的半導體製程中,甚至已經做出厚度僅有1.2納米的柵極氧化層,大約等於5個原子疊在一起的厚度而已。在這種尺度下,所有的物理現象都在量子力學所規範的世界內,例如電子的穿隧效應(tunnelingeffect)。因為穿隧效應,有些電子有機會越過氧化層所形成的位能障壁(potentialbarrier)而產生漏電流,這也是今日積體電路晶片功耗的來源之一。

為了解決這個問題,有一些介電常數比二氧化矽更高的物質被用在柵極氧化層中。例如鉿(Hafnium)和鋯(Zirconium)的金屬氧化物(二氧化鉿、二氧化鋯)等高介電常數的物質均能有效降低柵極漏電流。柵極氧化層的介電常數增加後,柵極的厚度便能增加而維持一樣的電容大小。而較厚的柵極氧化層又可以降低電子透過穿隧效應穿過氧化層的機率,進而降低漏電流。不過利用新材料製作的柵極氧化層也必須考慮其位能障壁的高度,因為這些新材料的傳導帶(conductionband)和價帶(valenceband)和半導體的傳導帶與價帶的差距比二氧化矽小(二氧化矽的傳導帶和矽之間的高度差約為8ev),所以仍然有可能導致柵極漏電流出現。

製程變異更難掌控

現代的半導體製程工序複雜而繁多,任何一道製程都有可能造成積體電路晶片上的元件產生些微變異。當MOSFET等元件越做越小,這些變異所占的比例就可能大幅提升,進而影響電路設計者所預期的效能,這樣的變異讓電路設計者的工作變得更為困難。

MOSFET的柵極材料

理論上MOSFET的柵極應該儘可能選擇電性良好的導體,多晶矽在經過重(讀作zhong)摻雜之後的導電性可以用在MOSFET的柵極上,但是並非完美的選擇。MOSFET使用多晶矽作為的理由如下:

⒈MOSFET的臨界電壓(thresholdvoltage)主要由柵極與通道材料的功函式(workfunction)之間的差異來決定,而因為多晶矽本質上是半導體,所以可以藉由摻雜不同極性的雜質來改變其功函式。更重要的是,因為多晶矽和底下作為通道的矽之間能隙(bandgap)相同,因此在降低PMOS或是NMOS的臨界電壓時可以藉由直接調整多晶矽的功函式來達成需求。反過來說,金屬材料的功函式並不像半導體那么易於改變,如此一來要降低MOSFET的臨界電壓就變得比較困難。而且如果想要同時降低PMOS和NMOS的臨界電壓,將需要兩種不同的金屬分別做其柵極材料,對於製程又是一個很大的變數。

⒉矽—二氧化矽接面經過多年的研究,已經證實這兩種材料之間的缺陷(defect)是相對而言比較少的。反之,金屬—絕緣體接面的缺陷多,容易在兩者之間形成很多表面能階,大為影響元件的特性。

⒊多晶矽的融點比大多數的金屬高,而在現代的半導體製程中習慣在高溫下沉積柵極材料以增進元件效能。金屬的融點低,將會影響製程所能使用的溫度上限。

不過多晶矽雖然在過去二十年是製造MOSFET柵極的標準,但也有若干缺點使得未來仍然有部份MOSFET可能使用金屬柵極,這些缺點如下:

⒈多晶矽導電性不如金屬,限制了信號傳遞的速度。雖然可以利用摻雜的方式改善其導電性,但成效仍然有限。有些融點比較高的金屬材料如:鎢(Tungsten)、鈦(Titanium)、鈷(Cobalt)或是鎳(Nickel)被用來和多晶矽製成合金。這類混合材料通常稱為金屬矽化物(silicide)。加上了金屬矽化物的多晶矽柵極有著比較好的導電特性,而且又能夠耐受高溫製程。此外因為金屬矽化物的位置是在柵極表面,離通道區較遠,所以也不會對MOSFET的臨界電壓造成太大影響。

在柵極、源極與漏極都鍍上金屬矽化物的製程稱為“自我對準金屬矽化物製程”(Self-AlignedSilicide),通常簡稱salicide製程。

⒉當MOSFET的尺寸縮的非常小、柵極氧化層也變得非常薄時,例如編輯此文時最新製程可以把氧化層縮到一納米左右的厚度,一種過去沒有發現的現象也隨之產生,這種現象稱為“多晶矽耗盡”。當MOSFET的反轉層形成時,有多晶矽耗盡現象的MOSFET柵極多晶矽靠近氧化層處,會出現一個耗盡層(depletionlayer),影響MOSFET導通的特性。要解決這種問題,金屬柵極是最好的方案。可行的材料包括鉭(Tantalum)、鎢、氮化鉭(TantalumNitride),或是氮化鈦(TitaliumNitride)。這些金屬柵極通常和高介電常數物質形成的氧化層一起構成MOS電容。另外一種解決方案是將多晶矽完全的合金化,稱為FUSI(FUlly-SIlicidepolysilicongate)製程。

各種常見的MOSFET技術

雙柵極MOSFET

雙柵極(dual-gate)MOSFET通常用在射頻(RadioFrequency,RF)積體電路中,這種MOSFET的兩個柵極都可以控制電流大小。在射頻電路的套用上,雙柵極MOSFET的第二個柵極大多數用來做增益、混頻器或是頻率轉換的控制。

耗盡型MOSFET

一般而言,耗盡型(depletionmode)MOSFET比前述的增強型(enhancementmode)MOSFET少見。耗盡型MOSFET在製造過程中改變摻雜到通道的雜質濃度,使得這種MOSFET的柵極就算沒有加電壓,通道仍然存在。如果想要關閉通道,則必須在柵極施加負電壓。耗盡型MOSFET最大的套用是在“常閉型”(normally-off)的開關,而相對的,加強式MOSFET則用在“常開型”(normally-on)的開關上。

NMOS邏輯

同樣驅動能力的NMOS通常比PMOS所占用的面積小,因此如果只在邏輯門的設計上使用NMOS的話也能縮小晶片面積。不過NMOS邏輯雖然占的面積小,卻無法像CMOS邏輯一樣做到不消耗靜態功率,因此在1980年代中期後已經漸漸退出市場。

功率MOSFET

MOSFET

MOSFET功率MOSFET和前述的MOSFET元件在結構上就有著顯著的差異。一般積體電路里的MOSFET都是平面式(planar)的結構,電晶體內的各端點都離晶片表面只有幾個微米的距離。而所有的功率元件都是垂直式(vertical)的結構,讓元件可以同時承受高電壓與高電流的工作環境。一個功率MOSFET能耐受的電壓是雜質摻雜濃度與N型磊晶層(epitaxiallayer)厚度的函式,而能通過的電流則和元件的通道寬度有關,通道越寬則能容納越多電流。對於一個平面結構的MOSFET而言,能承受的電流以及崩潰電壓的多寡都和其通道的長寬大小有關。對垂直結構的MOSFET來說,元件的面積和其能容納的電流成大約成正比,磊晶層厚度則和其崩潰電壓成正比。

功率MOSFET的工作原理

MOSFET

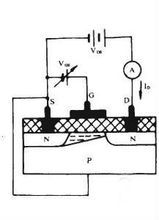

MOSFET導電:在柵源極間加正電壓UGS,柵極是絕緣的,所以不會有柵極電流流過。但柵極的正電壓會將其下面P區中的空穴推開,而將P區中的少子—電子吸引到柵極下面的P區表面

當UGS大於UT(開啟電壓或閾值電壓)時,柵極下P區表面的電子濃度將超過空穴濃度,使P型半導體反型成N型而成為反型層,該反型層形成N溝道而使PN結J1消失,漏極和源極導電。

值得一提的是採用平面式結構的功率MOSFET也並非不存在,這類元件主要用在高級的音響放大器中。平面式的功率MOSFET在飽和區的特性比垂直結構的MOSFET更好。垂直式功率MOSFET則取其導通電阻(turn-onresistance)非常小的優點,多半用來做開關切換之用。

DMOS

DMOS是雙重擴散MOSFET(double-DiffusedMOSFET)的縮寫,它主要用於高壓,屬於高壓MOS管範疇。

以MOSFET實現模擬開關

MOSFET在導通時的通道電阻低,而截止時的電阻近乎無限大,所以適合作為模擬信號的開關(信號的能量不會因為開關的電阻而損失太多)。MOSFET作為開關時,其源極與漏極的分別和其他的套用是不太相同的,因為信號可以從MOSFET柵極以外的任一端進出。對NMOS開關而言,電壓最負的一端就是源極,PMOS則正好相反,電壓最正的一端是源極。MOSFET開關能傳輸的信號會受到其柵極—源極、柵極—漏極,以及漏極到源極的電壓限制,如果超過了電壓的上限可能會導致MOSFET燒毀。

MOSFET開關的套用範圍很廣,舉凡需要用到取樣持有電路(sample-and-holdcircuits)或是截波電路(choppercircuits)的設計,例如類比數位轉換器(A/Dconverter)或是切換電容濾波器(switch-capacitorfilter)上都可以見到MOSFET開關的蹤影。

單一MOSFET開關

當NMOS用來做開關時,其基極接地,柵極為控制開關的端點。當柵極電壓減去源極電壓超過其導通的臨界電壓時,此開關的狀態為導通。柵極電壓繼續升高,則NMOS能通過的電流就更大。NMOS做開關時操作線上性區,因為源極與漏極的電壓在開關為導通時會趨向一致。

PMOS做開關時,其基極接至電路里電位最高的地方,通常是電源。柵極的電壓比源極低、超過其臨界電壓時,PMOS開關會打開。

NMOS開關能容許通過的電壓上限為(Vgate-Vthn),而PMOS開關則為(Vgate+Vthp),這個值通常不是信號原本的電壓振幅,也就是說單一MOSFET開關會有讓信號振幅變小、信號失真的缺點。

雙重MOSFET(CMOS)開關

為了改善前述單一MOSFET開關造成信號失真的缺點,於是使用一個PMOS加上一個NMOS的CMOS開關成為目前最普遍的做法。CMOS開關將PMOS與NMOS的源極與漏極分別連線在一起,而基極的接法則和NMOS與PMOS的傳統接法相同。當輸入電壓在(VDD-Vthn)和(VSS+Vthp)時,PMOS與NMOS都導通,而輸入小於(VSS+Vthp)時,只有NMOS導通,輸入大於(VDD-Vthn)時只有PMOS導通。這樣做的好處是在大部分的輸入電壓下,PMOS與NMOS皆同時導通,如果任一邊的導通電阻上升,則另一邊的導通電阻就會下降,所以開關的電阻幾乎可以保持定值,減少信號失真。

對比

PowerMOSFET全稱功率場效應電晶體。它的三個極分別是源極(S)、漏極(D)和柵極(G)。主要優點:熱穩定性好、安全工作區大。缺點:擊穿電壓低,工作電流小。IGBT全稱絕緣柵雙極電晶體,是MOSFET和GTR(功率晶管)相結合的產物。它的三個極分別是集電極(C)、發射極(E)和柵極(G)。特點:擊穿電壓可達1200V,集電極最大飽和電流已超過1500A。由IGBT作為逆變器件的變頻器的容量達250kVA以上,工作頻率可達20kHz。