雙極型積體電路

正文

在半導體內,多數載流子和少數載流子兩種極性的載流子(空穴和電子)都參與有源元件的導電,如通常的NPN或PNP雙極型電晶體。以這類電晶體為基礎的單片積體電路,稱為雙極型積體電路。雙極型積體電路是最早製成集成化的電路,出現於1958年。雙極型積體電路主要以矽材料為襯底,在平面工藝基礎上採用埋層工藝和隔離技術,以雙極型電晶體為基礎元件。它包括數字積體電路和線性積體電路兩類。

發展簡況 雙極型積體電路是在矽平面電晶體的基礎上發展起來的,最早的是雙極型數字邏輯積體電路。在數字邏輯積體電路的發展過程中,曾出現過多種不同類型的電路形式。常見的雙極型積體電路可分類如下。

雙極型積體電路

雙極型積體電路以上均屬飽和型電路。在進一步探索提高飽和型電路開關速度的同時,發現電晶體多餘載流子的存儲效應是一個極重要的障礙。存儲現象實質上是電路在開關轉換過程中由多餘載流子所引起。要提高電路開關速度,除了減少電晶體pn結電容,或者設法縮短多餘載流子的壽命以外,就得減少和消除電晶體內載流子存儲現象。60年代末和70年代初,人們開始在積體電路中利用熟知的肖特基效應。在TTL電路上製備肖特基勢壘二極體,把它並接在原有電晶體的基極和集電極上,使電晶體開關時間縮短到1納秒左右;帶肖特基勢壘二極體箝位的TTL門電路的平均傳輸延遲時間達2~4納秒。

肖特基勢壘二極體-電晶體-電晶體邏輯電路(STTL)屬於第三代 TTL電路。它線上路上採用了肖特基勢壘二極體箝位方法,使電晶體處於臨界飽和狀態,從而消除和避免了載流子存儲效應。與此同時,在TTL電路與非門輸出級倒相器的基極引入電晶體分流器,可以改善與非門特性。三極體帶有肖特基勢壘二極體,可避免進入飽和區,具有高速性能;輸出管加上分流器,可保持輸出級倒相的抗飽和程度。這類雙極型積體電路,已不再屬於飽和型積體電路,而屬於另一類開關速度快得多的抗飽和型積體電路。

發射極耦合邏輯電路(ECL)是電流型邏輯電路(CML)。這是一種電流開關電路, 電路的電晶體工作在非飽和狀態,電路的開關速度比通常TTL電路又快幾倍。ECL邏輯電路把電路開關速度提高到 1納秒左右,大大超過 TTL和STTL電路。ECL電路的出現,使雙極型積體電路進入超高速電路範圍。

集成注入邏輯電路 (I2L)又稱合併電晶體邏輯電路(MTL),是70年代研製成的。在雙極型積體電路中,I2L電路的集成密度是最高的。

三層結構邏輯電路(3TL)是1976年中國在I2L電路的基礎上改進而成,因有三層結構而得名。3TL邏輯電路採用NPN管為電流源,輸出管採用金屬做集電極(PNM),不同於I2L結構。

多元邏輯電路(DYL)和雙層邏輯電路(DLL),是1978年中國研製成功的新型邏輯電路。DYL邏輯電路線性與或門,能同時實現開關邏輯和線性邏輯處理功能。DLL電路是通過ECL和TTL邏輯電路雙信息內部變換來實現電路邏輯功能的。

此外,在雙極型積體電路發展過程中,還有許多其他型式的電路。例如,發射極功能邏輯電路(EFL)、互補電晶體邏輯電路(CTL)、抗輻照互補恆流邏輯電路(C3L)、電流參差邏輯電路(CHL)、三態邏輯電路(TSL)和非閾值邏輯電路(NTL)等。

特點和原理 雙極型積體電路的製造工藝,是在平面工藝基礎上發展起來的。與製造單個雙極型電晶體的平面工藝相比,具有若干工藝上的特點。

① 雙極型積體電路中各元件之間需要進行電隔離。積體電路的製造,先是把矽片劃分成一定數目的相互隔離的隔離區;然後在各隔離區內製作電晶體和電阻等元件。在常規工藝中大多採用PN結隔離,即用反向PN結達到元件之間相互絕緣的目的。除PN結隔離以外,有時也採用介質隔離或兩者混合隔離法(見隔離技術)。

② 雙極型積體電路中需要增添隱埋層。通常,雙極型積體電路中電晶體的集電極,必須從底層向上引出連線點,因而增加了集電極串連電阻,這不利於電路性能。為了減小集電極串連電阻,製作電晶體時在集電極下邊先擴散一層隱埋層,為集電極提供電流低阻通道和減小集電極的串聯電阻。隱埋層,簡稱埋層,是隱埋在矽片體內的高摻雜低電阻區。埋層在製作積體電路之前預先“埋置”在晶片體內。其工藝過程是:在 P型矽片上,在預計製作集電極的正下方某一區域裡先擴散一層高濃度施主雜質即N+區;而後在其上再外延生長一層N型矽單晶層。於是,N型外延層將N+區隱埋在下面,再在這一外延層上製作電晶體。

③ 雙極型積體電路通常採用擴散電阻。電路中按電阻阻值大小選擇製備電阻的工藝,大多數是利用電晶體基區P型擴散的同時,製作每方約 150~200歐·厘米的P型擴散電阻。但是,擴散電阻存在阻值誤差大、溫度係數高和有寄生效應等缺點。除採用擴散電阻外,有時也採用矽單晶體電阻。

④ 雙極型積體電路元件間需要互連線,通常為金屬鋁薄層互連線。單層互連布線時難以避免交叉的位置,必要時可採用濃磷擴散低阻區,簡稱磷橋連線法。

⑤ 雙極型積體電路存在寄生效應。雙極型積體電路的縱向NPN電晶體,比分立電晶體多一個P型襯底層和一個PN結。它是三結四層結構。增加的襯底層是所有元件的公共襯底,增加的一個PN結是隔離結(包括襯底結)。雙極型積體電路因是三結四層結構而會產生特有的寄生效應:無源寄生效應、擴散電阻的寄生電容和有源寄生效應。隔離電容是集電極N型區與隔離槽或襯底P型區形成的PN結產生的電容。隔離和襯底接最低電位,所以這個電容就是集電極對地的寄生電容。擴散電阻的寄生電容是擴散電阻P型區與集電極外延層N型區產生的PN結電容,也屬無源寄生效應。這一PN結電容總是處於反偏置工作狀態。有源寄生效應即 PNP寄生電晶體。在電路中,NPN電晶體的基區、集電區(外延層)和襯底構成PNP寄生電晶體。在通常情況下,因PN結隔離,外延層和襯底之間總是反向偏置。只有當電路工作時,NPN管的集電結正偏,寄生PNP管才進入有源區。

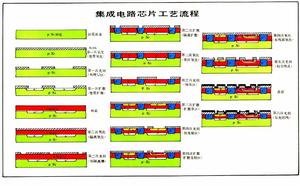

工藝製備 (見彩圖)是利用PN結隔離技術製備雙極型積體電路倒相器的工藝流程,圖中包括一個NPN電晶體和一個負載電阻R。原始材料是直徑為75~150毫米摻P型雜質的矽單晶棒,電阻率ρ=10歐·厘米左右。其工藝流程是:先經過切片、研磨和拋光等工藝(是矽片製備工藝)製備成厚度約300~500微米的圓形矽片作為襯底,然後進行外延生長、氧化、光刻、擴散、蒸發、壓焊和多次矽片清洗,最後進行表面鈍化和成品封裝。

雙極型積體電路

雙極型積體電路版圖設計 按照線路要求和工藝條件設計元件的圖形和尺寸,並進行布局和布線,同時設計出一套光刻掩模版圖形。

版圖設計的第一步,是對既定線路按不同電位劃分隔離區和確定元件之間的布線。然後,轉入對元件的設計。雙極型積體電路的元件包括電晶體、二極體、電阻和電容。其中 NPN電晶體的設計是核心。設計一個性能良好的積體電路,首先要設計出電學性能符合要求的電晶體,而電晶體的特性又是由其圖形、尺寸和工藝條件所決定的。

在雙極型積體電路中,常用的電晶體圖形有5種,每一種圖形各有其特殊作用(見)。這 5種圖形是單基極條形、雙基極條形、雙基極、雙集電極條形、基極馬蹄形(並聯擴展可設計成梳形結構)和發射極馬蹄形。在版圖設計中,往往在同一塊版圖中幾種電晶體圖形會同時出現,這是因為不同電晶體在電路中所起作用不同。

雙極型積體電路

雙極型積體電路在雙極型積體電路的版圖設計中,電阻通常是隨同電晶體的某一擴散工藝同時進行而製成擴散電阻的。原則上,不論發射區、基區和集電區(外延層),都可以製作電阻。①基區硼擴散電阻:其薄層電阻值為 150~200歐/□左右,邏輯積體電路中的電阻值範圍比較適中,而且溫度係數也較小,一般為 1.9×10-3/

。②發射區磷擴散電阻:其薄層電阻值為2~5歐/□,可用作低值電阻。但實際上常用作“磷橋”,代替內部金屬連線遇到難以避免交叉時完成交越;③基區溝道電阻:這是利用基區擴散和發射區擴散形成的。因為薄層很薄,擴散雜質濃度也低,薄層電阻可高達5~20千歐/□。溫度係數較高,一般為3~5×10-3/

。②發射區磷擴散電阻:其薄層電阻值為2~5歐/□,可用作低值電阻。但實際上常用作“磷橋”,代替內部金屬連線遇到難以避免交叉時完成交越;③基區溝道電阻:這是利用基區擴散和發射區擴散形成的。因為薄層很薄,擴散雜質濃度也低,薄層電阻可高達5~20千歐/□。溫度係數較高,一般為3~5×10-3/ 。這種電阻器又受到工作電壓的限制,當反偏壓升高時,pn結勢壘區擴張,使溝道變得更薄,阻值變大;反之,偏壓降低,阻值變小;④體電阻:外延層體電阻阻值很難控制,可用作高阻值電阻,其溫度係數高,約為5×10-3/

。這種電阻器又受到工作電壓的限制,當反偏壓升高時,pn結勢壘區擴張,使溝道變得更薄,阻值變大;反之,偏壓降低,阻值變小;④體電阻:外延層體電阻阻值很難控制,可用作高阻值電阻,其溫度係數高,約為5×10-3/ 。

。 參考書目

復旦大學微電子教研組編:《積體電路設計原理》,人民教育出版社,北京,1978。

汪希時編著:《電晶體-電晶體邏輯積體電路與數位技術》,科學出版社,北京,1978。