肖特基勢壘MOSFET 的優點:等效於使源和漏的結深減小(幾乎為0),短溝道效應大大減弱;源和漏接觸的高導電性,使得源、漏的串聯電阻降低;源和漏接觸的製作不需要高溫退火, 這可保證SiO2層的質量和幾何圖形在加工過程中不發生變化;對寬禁帶半導體硫化鎘(cds)等之類的單極性半導體, 可用此接觸來避免製作p-n結上的困難。

肖特基勢壘MOSFET 的缺點:為了提高源-漏電壓, 對半導體表面處理的工藝要求較高;對Si-MOSFET而言, 一般只能作成p-溝MOSFET,因為電極材料常用的是PtSi, 它與p-型Si的Schottky勢壘高度只有0.25eV, 與n-型Si的Schottky勢壘高度有0.85eV。

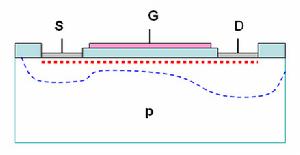

去掉了源和漏的pn結

去掉了源和漏的pn結