簡介

絕緣體上矽SOI

在整個行業向新一代半導體器件的衍變過程中,晶片製造商面臨著嚴峻的挑戰。具體的講,生產高性能晶片的製造商面臨的挑戰來自對速度更快、溫度更低的晶片設計的需求。用於移動套用的晶片製造商需要的是功耗更小的半導體器件。為了應對這些挑戰,大多數業界領先的器件製造商都選擇了絕緣體上矽(SOI)。

主要結構

SOI 是指以“工程化的”基板代替傳統的體型襯底矽的基板技術,這種基板由以下三層構成:

● 薄薄的單晶矽頂層,在其上形成蝕刻電路

● 相當薄的絕緣二氧化矽中間層

● 非常厚的體型襯底矽襯底層,其主要作用是為上面的兩層提供機械支撐。

用途

開始採用SOI材料做基板時,晶片製造商在生產過程中仍然能夠繼續使用傳統的製造工藝和設備。事實證明,SOI完全能夠滿足主流MOSFET(金屬氧化物半導體場效應電晶體)的性能需求。對部分耗盡型和全部耗盡型CMOS(互補金屬氧化物半導體) 器件的性能改善、漏電流減小以及功耗減少等都會產生極大地影響,特別適合於低電壓器件結構等。

除了CMOS器件,SOI還可用來製造技術領先的微電子機械系統(MEMS

),MEMS 可用於感測器以及微光電技術電路等。此外,也可以利用SOI增強BiCMOS、功率器件和高壓器件的性能,另外還能夠改善在高溫環境或者曝光在電離輻射環境下的積體電路的性能。

基於SOI的器件

SOI晶圓製造的晶片由數百萬含電晶體的絕緣區組成,每個絕緣區都與其它絕緣區和其下的體型襯底矽基板互相隔離。這一特點極大地簡化了電路的設計:由於電晶體之間是互相隔離的,設計師無需為了實現反偏結點的電氣絕緣而設計複雜的電路方案。同時絕緣層也會保護頂層和體矽襯底基板上寄生的活動矽層。SOI的這兩個優點,使得設計師們能夠研發出更加緊湊的超大規模積體電路(VLSI)晶片。

同時,積體電路製造商利用SOI還能夠生產出在待機和操作模式下功耗更低的CMOS電路。由於此結構中絕緣層把活動矽膜層與體型襯底矽基板分隔開來,因此大面積的p-n結將被介電隔離(dielectric isolation)取代。源極和漏極(drain regions)向下延伸至氧化埋層(buried oxide BOX),有效減少了漏電流和結電容。其結果必然是大幅度提高了晶片的運行速度,拓寬了器件工作的溫度範圍。

與通過傳統的體型襯底矽晶圓生產的晶片相比,基於SOI的晶片受“簡訊道”效應的影響更小。簡訊道效應是門極和結點之間“電荷共享”的結果。門極電場與源極和漏極互相競爭。但是由於膜層厚度大大低於源極和漏極之間的空間,電晶體本身的厚度因此受到了限制,簡訊道效應也將大幅度減少,甚至消失。

製造技術

SOI 晶圓的製造

SOI晶圓製造技術已經開發了很多種。然而,由Soitec 倡導的被命名為Smart CutTM的粘合技術是最具有實踐意義和最堅固耐用的技術之一,非常適合於量產和工業化生產。目前超過90%的SOI晶圓市場都是以Smart Cut 技術為基礎打造的。

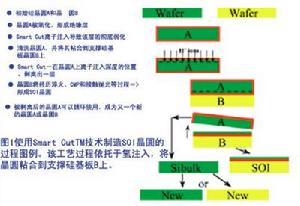

Smart Cut 是一種創新性的技術,用來將晶圓基板材料(如矽晶)生成的超薄單晶體層移植到另一個表面。該技術採用離子注入和熱激活工藝作為一種“原子解剖刀”(atomic scalpel),逐一將晶圓水平切片,從“原”基板上剝起薄薄的一層,並將它放到新的基板上(參見圖1)。

高級的工程基板

SOI 是目前套用最廣泛的工程基板。對於現有的器件,頂層矽的厚度普遍為500A ;在65納米技術標準下,膜厚將降到200A。而且,除了SOI之外,Smart Cut 剝離和粘合技術還適用於其它更寬泛的工程基板。分別是:

● 應變SOI,在頂層的晶格中,矽晶的電子活動層被拉緊(主要是被拉伸),這樣使得電荷的流動速度更快。電路的性能至少能夠提高30%至40%(報告表明電子移動速度提高了80%之多)。預計技術領先的器件製造商會將應變SOI引入到45納米技術標準的套用中。

● 多層複合半導體基板,這些基板以第III-V 代材料為基礎,如GaAs、InP、GaN以及SiC等,將被用於開發高頻、高功率套用和光電器件等。

● GeOI (絕緣體上鍺)基板籍由在矽上引入大量的鍺,極大地改善了電子移動速度,為未來的高速邏輯套用提供了信心。這種基板將被引入到32納米技術標準的套用中。

隨著整個半導體行業的目標逐步轉向提高性能、降低功耗、設計先進的微電子套用,體矽晶圓已不再能夠滿足需求。毫無疑問,SOI和其它工程基板將成為半導體行業未來發展的中流砥柱性能至少能夠提高30%至40%(報告表明電子移動速度提高了80%之多)。預計技術領先的器件製造商會將應變SOI引入到45納米技術標準的套用中。

● 多層複合半導體基板,這些基板以第III-V 代材料為基礎,如GaAs、InP、GaN以及SiC等,將被用於開發高頻、高功率套用和光電器件等。

● GeOI (絕緣體上鍺)基板籍由在矽上引入大量的鍺,極大地改善了電子移動速度,為未來的高速邏輯套用提供了信心。這種基板將被引入到32納米技術標準的套用中。隨著整個半導體行業的目標逐步轉向提高性能、降低功耗、設計先進的微電子套用,體矽晶圓已不再能夠滿足需求。毫無疑問,SOI和其它工程基板將成為半導體行業未來發展的中流砥柱。