基本思路

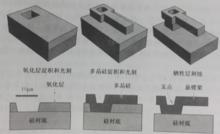

圖1-1 表面矽MEMS加工工藝流程圖

圖1-1 表面矽MEMS加工工藝流程圖表面矽MEMS加工技術的基本思路是:先在基片上澱積一層稱為犧牲層的材料,然後在犧牲層上面澱積一層結構層並加工成所需圖形。在結構加工成型後,通過選擇腐蝕的方法將犧牲層腐蝕掉,使結構材料懸空於基片之上,形成各種形狀的二維或三維結構。表面矽MEMS加工工藝成熟,與IC工藝兼容性好,可以在單個直徑為幾十毫米的單晶矽基片上批量生成數百個MEMS裝置。美國加州大學Berkeley分校的感測器與執行器研究中心(BSAC)首先完成了三層多晶矽表面MEMS工藝,確立了矽表面MEMS加工工藝體系。圖1-1是一套表面犧牲層加工工藝流程。首先在襯底上澱積犧牲層材料(氧化矽)並形成可動微結構與襯底之間的連線視窗,然後澱積作為微結構的材料並光刻出所需的圖形,最後利用濕法腐蝕去掉犧牲層,這樣就行成了既能夠活動又與襯底相連的微結構。

關鍵工藝技術

低應力薄膜技術

表面矽MEMS加工工藝主要是以不同方法在襯底表面加工不同的薄膜,並根據需要事先在薄膜下面已確定的區域中生長犧牲層。這些都需要制膜工藝來完成。制膜的方法有很多,如蒸鍍、濺射等物理氣相澱積法(PVD)、化學氣相澱積法(CVD)以及外延和氧化等。其中CVD是微電子加工技術中最常用的薄膜製作技術之一,它是在受控氣相條件下,通過氣體在加熱基板上反應或分解使其生成物澱積到基板上形成薄膜。CVD技術可以分為常壓( APCVD)、低壓(LPCVD)、電漿增強(PECVD)等不同技術。採用CVD所能製作的膜有多晶矽、單晶矽、非晶矽等半導體薄膜,氧化矽、氮化矽等絕緣體介質膜,以及高分子膜和金屬膜等。由於在表面矽MEMS加工技術中最常用到的是多晶矽、氧化矽、氮化矽薄膜,而它們通常採用LPCVD或PECVD來製作。

1、LPCVD制膜技術。

多晶矽、氧化矽、氮化矽薄膜都可以採用LPCVD製作。

LPCVD多晶矽是利用矽烷(SiH)熱分解形成的矽澱積在基片上而成。多晶矽薄膜有非摻雜多晶矽進而摻雜多晶矽兩種,後者是在澱積過程中添加氣態摻雜劑(如乙硼烷、砷烷或磷烷)。LPCVD多晶矽薄膜的特性,如結構、晶粒大小、表面粗糙度、應力大小等,是由LPCVD的溫度,壓力以及氣流量等條件決定的。典型的LPCVD多晶矽的澱積溫度是在550℃~700℃之間,在低於600℃的生長溫度條件下,得到的是非晶矽薄膜,而在630℃以上則能得到良好的多晶矽薄膜。在600℃之間生成的非晶矽薄膜的晶粒尺寸小、表面粗糙度小(<15Å),而在620℃以上生成的多晶矽薄膜的晶粒較大、表面較為粗糙(>50Å)。多晶矽的澱積速度隨溫度的升高而呈指數關係增加,一般約為幾納米/分到幾百納米/分。多晶矽薄膜的應力隨生長溫度和矽烷壓力的不同而有著較大的變化。為了獲得低應力的多晶矽薄膜,通常在LPCVD澱積多晶矽薄膜完成後,通過高溫退火(>900℃)處理來釋放應力。

LPCVD澱積氧化矽的方法有多種。一種是在低於500℃條件下,利用SiH和氧氣反應在基片上澱積形成氧化矽。由於是在低溫條件下製作,因而這種方法澱積的氧化物也被稱為低溫氧化物(LTO),它通常被用作鋁電極引線的鈍化層,為了防止鋁的退化,一般的澱積溫度控制在400℃以下。同摻雜多晶矽相似,採用這種方法製作的氧化矽也可以在澱積過程中通過添加磷化氫或乙硼烷等氣態摻雜劑形成摻雜的氧化矽如磷矽玻璃(PSG)或硼磷矽玻璃(BPSG)。LPCVD澱積氧化矽的另一種方法是在650℃~750℃的溫度範圍內,利用Si(OCH)熱分解形成四乙基原矽酸鹽(TEOS)。TEOS具有良好的一致性和台階覆蓋性,但由於澱積溫度較高,不能用作鋁電極引線的鈍化層。此外還有一種在約900℃條件下,通過SiClH和NO反應澱積氧化矽的方法,這種氧化矽具有良好的薄膜特性和一致性,但不適於製作多晶矽的絕緣層。

LPCVD澱積氧化矽是在700℃~900℃條件下,通過SiClH和NH反應形成。一般來說,LPCVD澱積製作的氮化矽薄膜呈現出很大的張應力(約1000MPa),但是通過調整澱積溫度(800℃~850℃)和反應氣體流量(即增大SiClH的流速,使生成的氮化矽薄膜中矽含量較多(富矽))可以製作出低應力(<100MPa)的氮化矽薄膜,這種低應力LPCVD氮化矽薄膜在MEMS領域已獲得了廣泛的套用。

2、PECVD制膜技術。

PECVD法是利用輝光放電的物理作用來激活化學氣相澱積反應。其澱積溫度一般在400℃以下,可以用來澱積氧化矽、氮化矽、PSG、BPSG、AlO等絕緣體及鈍化膜和非晶矽薄膜以及有機化合物和TiC、TiN等耐磨抗蝕膜。在表面矽MEMS工藝中,PECVD主要用來製作低應力氮化矽薄膜。PECVD氮化矽是在低於400℃條件下,利用SiH和NH(或N)反應形成。PECVD氮化矽的應力控制可以通過調整反應氣體流量和電漿的激活頻率來實現。

犧牲層技術

犧牲層技術是在矽基板上,先製作一定形狀的犧牲層材料,再用化學氣相澱積等方法形成製作微型部件的結構層。最後,以融解或刻蝕法去除犧牲層,使微型部件的可動部分與基板分離。理想的犧牲層材料必須滿足以下要求:膜的厚度必須控制在可接受的公差內,這是由於不均勻的沉積將導致機械部件表面粗糙或不平整;犧牲層在結構層部件釋放時,必須能夠被去除乾淨;犧牲層的腐蝕選擇率和腐蝕速率必須很高,以便在腐蝕犧牲層時,結構的其他部分不被明顯損傷。

在表面矽MEMS加工技術中,通常是以LPCVD法製作的多晶矽作為結構層而以LPCVD法或PECVD法製作的PSG或PBSG作為犧牲層材料。PSG或PBSG結構疏鬆,可以在氫氟酸(HF)水溶液中以較快的腐蝕速率被去除乾淨。而多晶矽在HF水溶液中的腐蝕速度非常慢,在經過長時間腐蝕PSG或PBSG後,多晶矽結構層不會發生明顯腐蝕。

在早期的MEMS器件中發現:在微機械結構釋放過程中,當用HF水溶液腐蝕犧牲層、釋放多晶矽微結構、乾燥時,矽片表面薄層水的表面張力使兩片親水、間隙在微米量級的矽片常常會黏合起來,這種黏合被稱為“釋放有關黏合”,直接影響著器件成品率。為了解決這個問題,國內外先後開發出了超臨界CO乾燥法、冷凝升華法和犧牲層乾法腐蝕法等方法,使矽片表面不生成水薄層來消除由於表面張力引起的黏合。近年來,出現了在表面塗覆自組裝單分子層薄膜、碳氟(CF)薄膜或類金剛石碳(DLS)薄膜等疏水性薄膜的解決“釋放有關黏合”的方案。值得指出,這種塗覆薄膜防止黏合的技術,不僅能夠解決“釋放有關黏合”,而且也能夠解決發生在封裝後器件中由於輸入信號過沖時發生的“使用中黏合”。

工藝集成

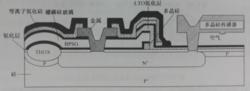

圖1-2 美國ADI公司的BiMEMS表面集成工藝

圖1-2 美國ADI公司的BiMEMS表面集成工藝 圖1-3 Sandia的MM/CMOS MEMS集成工藝

圖1-3 Sandia的MM/CMOS MEMS集成工藝表面矽MEMS工藝是典型的薄膜工藝,其技術特點與積體電路相近,通過與積體電路集成製作的可行性最大。正因為有如此鮮明的特點,表面犧牲層工藝從其誕生起發展方向就是集成化。典型的工藝包括美國ADI公司的BiMEMS集成工藝(圖1-2)和美國Sandia國家實驗室的MM/CMOS MEMS集成工藝(圖1-3)。BiMEMS工藝的特點是製作可動部件的表面MEMS工藝與製作處理電路的BiMOS工藝的混合完成。這一工藝的缺點是兩種工藝在同一加工線完成,需要專門的加工線,不能充分利用現有的IC Foundry線,因此成本較高,成品率受影響。為克服這一問題,美國Sandia國家實驗室的MM/CMOS集成MEMS技術首先在凹槽內製作可動部件,填充SiO後平坦化,然後再用標準CMOS工藝製作處理電路,大大改進了BiMEMS工藝的不足。然而,先製作可動部件將影響襯底片質量,大部分專業IC Foundry由於懼怕玷污設備而拒絕接受。因而第三種工藝方案套用而生,即美國密西根大學的Post-CMOS MEMS工藝,特點是先按標準IC Foundry製作處理電路,再製作可動部件,其成本和成品率都能得到保證。

工藝發展趨勢

1、 向多層多晶矽的標準表面工藝發展。

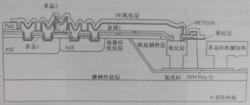

圖1-4 雙層結構表面矽MEMS集成工藝

圖1-4 雙層結構表面矽MEMS集成工藝由於機械結構的複雜性,僅採用單層結構往往不能製備出所需構件,多層化是表面矽MEMS工藝必然的發展趨勢。圖1-4所示為Wisconsin大學、三星公司和密西根大學共同發表的雙層結構集成化表面犧牲層工藝的剖面圖,代表了這一典型發展趨勢。美國的MUMPs是典型的民用標準表面工藝線,該工藝可以實現多達4層的犧牲層和多晶矽層,製造出複雜的MEMS器件,並定期發布更新的標準工藝檔案,接受來自世界各地的按照標準工藝檔案形成的MEMS設計。在一批工藝流水中包含數十種設計,通過這種方式提供廉價、迅速的MEMS表面加工服務。目前美國Sandia國家實驗室開發的5層多晶矽表面矽MEMS集成工藝代表了這一方向的最高水平,它主要為軍方的項目提供表面加工服務。

2、 向與CMOS集成的機電一體化技術發展。

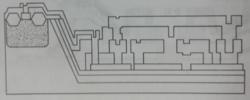

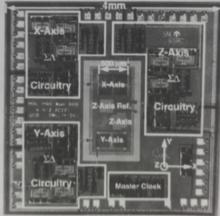

圖1-5AD的三軸單片集成式MEMS加速度計

圖1-5AD的三軸單片集成式MEMS加速度計相對體矽工藝,表面工藝由於保持了襯底的完整性,更容易與CMOS工藝兼容,美國的ADI公司推出的基於BiMOS工藝和表面加工技術的集成加速度計在汽車上獲得了廣泛套用,到2004年銷售超過了1億隻。實現CMOS工藝與多層多晶矽工藝的兼容目前還是一個挑戰,合理地安排工藝步驟、選擇合適的金屬化體系來保證成品率是突破該技術的關鍵問題。圖1-5是美國AD公司的三軸單片集成式MEMS加速度計的版圖照片,它將三個單軸的MEMS加速度計結構及其相應的讀出電路都集成在一個單片上。