概念

這樣就可以由設計人員自行編程而把一個數字系統“集成”在一片PLD上,而不必去請晶片製造廠商設計和製作專用的積體電路晶片了。

PLD與一般數字晶片不同的是:PLD內部的數字電路可以在出廠後才規劃決定,有些類型的PLD也允許在規劃決定後再次進行變更、改變,而一般數字晶片在出廠前就已經決定其內部電路,無法在出廠後再次改變,事實上一般的模擬晶片、混訊晶片也都一樣,都是在出廠後就無法再對其內部電路進行調修。

發展歷史

70年代:出現唯讀存儲器PROM (Programmable Read only Memory),可程式邏輯陣列器件PLA (Programmable Logic Array)

70年代末:AMD推出了可程式陣列邏輯PAL (Programmable Array Logic)

80年代:Lattice公司推出了通用陣列邏輯GAL ( Generic Array Logic)

80年代中:Xilinx公司推出了現場可程式門陣列FPGA (Field Programmable GateArray )。Altera公司推出了可擦除的可程式邏輯器件EPLD (Erase Programmable LogicDevice),集成度高,設計靈活,可多次反覆編程

90年代初:Lattice公司又推出了在系統可程式概念ISP及其在系統可程式大規模集成器件ispLSI)

現以Xilinx、Altera、Lattice為主要廠商,生產的FPGA單片可達上千萬門、速度可實現550MHz,採用65nm甚至更高的光刻技術。

分類

邏輯器件可分為兩大類 - 固定邏輯器件和可程式邏輯器件。 一如其名,固定邏輯器件中的電路是永久性的,它們完成一種或一組功能 - 一旦製造完成,就無法改變。 另一方面,可程式邏輯器件(CPLD)是能夠為客戶提供範圍廣泛的多種邏輯能力、特性、速度和電壓特性的標準成品部件 - 而且此類器件可在任何時間改變,從而完成許多種不同的功能。

對於固定邏輯器件,根據器件複雜性的不同,從設計、原型到最終生產所需要的時間可從數月至一年多不等。 而且,如果器件工作不合適,或者如果套用要求發生了變化,那么就必須開發全新的設計。 設計和驗證固定邏輯的前期工作需要大量的“非重發性工程成本”,或NRE。 NRE表示在固定邏輯器件最終從晶片製造廠製造出來以前客戶需要投入的所有成本,這些成本包括工程資源、昂貴的軟體設計工具、用來製造晶片不同金屬層的昂貴光刻掩模組,以及初始原型器件的生產成本。 這些NRE成本可能從數十萬美元至數百萬美元。

對於可程式邏輯器件,設計人員可利用價格低廉的軟體工具快速開發、仿真和測試其設計。 然後,可快速將設計編程到器件中,並立即在實際運行的電路中對設計進行測試。 原型中使用的PLD器件與正式生產最終設備(如網路路由器、ADSL數據機、DVD播放器、或汽車導航系統)時所使用的PLD完全相同。 這樣就沒有了NRE成本,最終的設計也比採用定製固定邏輯器件時完成得更快。

採用PLD的另一個關鍵優點是在設計階段中客戶可根據需要修改電路,直到對設計工作感到滿意為止。 這是因為PLD基於可重寫的存儲器技術--要改變設計,只需要簡單地對器件進行重新編程。 一旦設計完成,客戶可立即投入生產,只需要利用最終軟體設計檔案簡單地編程所需要數量的PLD就可以了。

可程式邏輯器件的兩種主要類型是現場可程式門陣列(FPGA)和複雜可程式邏輯器件(PLD)。 在這兩類可程式邏輯器件中,FPGA提供了最高的邏輯密度、最豐富的特性和最高的性能。 最新的FPGA器件,如Xilinx Virtex系列中的部分器件,可提供八百萬"系統門"(相對邏輯密度)。 這些先進的器件還提供諸如內建的硬連線處理器(如IBM Power PC)、大容量存儲器、時鐘管理系統等特性,並支持多種最新的超快速器件至器件(device-to-device)信號技術。 FPGA被套用於範圍廣泛的套用中,從數據處理和存儲,以及到儀器儀表、電信和數位訊號處理等。

與此相比,PLD提供的邏輯資源少得多 - 最高約1萬門。 但是,PLD提供了非常好的可預測性,因此對於關鍵的控制套用非常理想。 而且如Xilinx CoolRunner系列PLD器件需要的功耗極低。

對比

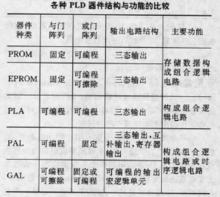

PLD有可程式唯讀存儲器(PROM)、可擦除可程式存儲器(EPROM)、可程式邏輯陣列(簡稱PLA)、可編陣列邏輯(簡稱PAL)和通用陣列邏輯(簡稱GAL)等幾種。它們的結構特點和功能列於表中。

PLA的總體結構與PROM類似,也由與門陣列、或門陣列和輸出緩衝器組成;它的與門陣列是可程式的。在產生同樣的組合邏輯函式時,使用PLA比使用PROM節省與門陣列和或門陣列中的單元數。

可程式邏輯器件

可程式邏輯器件有的PAL器件為暫存器輸出結構,所以用PAL不僅能構成組合邏輯電路,也能構成時序邏輯電路。GAL的輸出宏邏輯單元有不同的工作模式,並允許通過編程選定。這些工作模式包括了PAL的各種輸出結構。GAL更具通用性。PAL和GAL的編程工作比較複雜,需使用專門的開發工具(包括編程器和程式語言)進行。這些開發工具使用起來很方便。

特點

固定邏輯器件和PLD各有自己的優點。 例如,固定邏輯設計經常更適合大批量套用,因為它們可更為經濟地大批量生產。 對有些需要極高性能的套用,固定邏輯也可能是最佳的選擇。

然而,可程式邏輯器件提供了一些優於固定邏輯器件的重要優點,包括:PLD在設計過程中為客戶提供了更大的靈活性,因為對於PLD來說,設計反覆只需要簡單地改變編程檔案就可以了,而且設計改變的結果可立即在工作器件中看到。

PLD不需要漫長的前置時間來製造原型或正式產品 - PLD器件已經放在分銷商的貨架上並可隨時付運。 PLD不需要客戶支付高昂的NRE成本和購買昂貴的掩模組- PLD供應商在設計其可程式器件時已經支付了這些成本,並且可通過PLD產品線延續多年的生命期來分攤這些成本。

PLD允許客戶在需要時僅訂購所需要的數量,從而使客戶可控制庫存。 採用固定邏輯器件的客戶經常會面臨需要廢棄的過量庫存,而當對其產品的需求高漲時,他們又可能為器件供貨不足所苦,並且不得不面對生產延遲的現實。

PLD甚至在設備付運到客戶那兒以後還可以重新編程。 事實上,由於有了可程式邏輯器件,一些設備製造商正在嘗試為已經安裝在現場的產品增加新功能或者進行升級。 要實現這一點,只需要通過網際網路將新的編程檔案上載到PLD就可以在系統中創建出新的硬體邏輯。

發展前景

過去幾年時間裡,可程式邏輯供應商取得了巨大的技術進步,以致PLD被眾多設計人員視為是邏輯解決方案的當然之選。 能夠實現這一點的重要原因之一是象Xilinx這樣的PLD供應商是"無晶圓製造廠"企業,並不直接擁有晶片製造工廠,Xilinx將晶片製造工作外包給IBM Microelectronics 和 UMC這樣的主要業務就是製造晶片的合作夥伴。 這一策略使Xilinx可以集中精力設計新產品結構、軟體工具和IP核心,同時還可以利用最先進的半導體製造工藝技術。 先進的工藝技術在一系列關鍵領域為PLD提供了幫助:更快的性能、集成更多功能、降低功耗和成本等。 Xilinx採用先進的0.13um 低K銅金屬工藝生產可程式邏輯器件,這也是業界最好的工藝之一。

例如,僅僅數年前,最大規模的FPGA器件也僅僅為數萬系統門,工作在40 MHz。 過去的FPGA也相對較貴,當時最先進的FPGA器件大約要150美元。 然而,具有最先進特性的FPGA可提供百萬門的邏輯容量、工作在300 MHz,成本低至不到10美元,並且還提供了更高水平的集成特性,如處理器和存儲器。

同樣重要的是,PLD有越來越多的智慧財產權(IP)核心庫的支持 - 用戶可利用這些預定義和預測試的軟體模組在PLD內迅速實現系統功能。 IP核心包括從複雜數位訊號處理算法和存儲器控制器直到匯流排接口和成熟的軟體微處理器在內的一切。 此類IP核心為客戶節約了大量時間和費用 - 否則,用戶可能需要數月的時間才能實現這些功能,而且還會進一步延遲產品推向市場的時間。

其它相關

程式語言

有關之前所談到的“PAL”,若要以手工的方式來產生JEDEC檔實是過於複雜,所以多半改用電腦程式(也稱:電腦程式)來產生,這種程式(程式)稱為“邏輯編譯器,logic compiler”,它與程式開發撰寫時所用的軟體編譯器相類似,而要編譯之前的原始代碼(也稱:原始碼)也得用特定的程式語言(也稱:程式語言、程式語言)來撰寫,此稱之為hardware description language(硬體描述語言),簡稱:HDL。

而且,HDL並非僅有一種,而是有許多種,如ABEL、AHDL、Confluence、CUPL、HDCal、JHDL、Lava、Lola、MyHDL、PALASM、RHDL等都是,但最具知名也最普遍使用的是VHDL與Verilog。