複雜可程式邏輯器件(CPLD)

組成

CPLD主要由邏輯塊、可程式互連通道和I/O塊三部分構成。

規模

CPLD中的邏輯塊類似於一個小規模PLD,通常一個邏輯塊包含4~20個宏單元,每個宏單元一般由

複雜可程式邏輯器件CPLD

複雜可程式邏輯器件CPLD乘積項陣列、乘積項分配和可程式暫存器構成。每個宏單元有多種配置方式,各宏單元也可級聯使用, 因此可實現較複雜組合邏輯和時序邏輯功能。對集成度較高的CPLD,通常還提供了帶片內RAM/ROM的嵌入陣列塊。

可程式互連通道主要提供邏輯塊、宏單元、輸入/輸出引腳間的互連網路。輸入/輸出塊(I/O塊)提供內部邏輯到器件I/O引腳之間的接口。

邏輯規模較大的CPLD一般還內帶JTAG邊界掃描測試電路,可對已編程的高密度可程式邏輯器件做全面徹底的系統測試,此外也可通過JTAG接口進行在系統編程。

由於集成工藝、集成規模和製造廠家的不同,各種CPLD分區結構、邏輯單元等也有較大的差別。

可程式互連陣列結構

EPM7128S器件

(1)EPM7128S器件基本結構

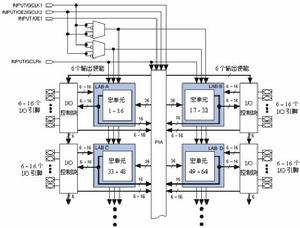

EPM7128S器件主要由邏輯陣列塊LAB、宏單元、I/O控制塊和可程式互連陣列PIA構成。

在多陣列矩陣結構中,每個宏單元有一個可程式的與陣列和一個固定的或陣列, 以及一個具有獨立可程式時鐘、時鐘使能、清除和置位功能的可配置觸發器。每16個宏單元組成一組,構成一個靈活的邏輯陣列模組LAB。多個LAB通過可程式互連陣列PIA和全局匯流排相連。每個LAB還與相應的I/O控制模組相連,以提供直接的輸入和輸出通道。

(2)EPM7128S宏單元結構

EPM7128S的每個宏單元能夠單獨配置為組合邏輯或時序邏輯工作方式。宏單元主要由邏輯陣列、乘積項選擇矩陣和可程式暫存器3部分組成。可程式暫存器根據邏輯需要,可以編程旁路,實現組合邏輯。如作為暫存器使用,則相應的可程式邏輯器件開發軟體將根據設計邏輯需要,選擇有效的暫存器工作方式,以使設計所用器件資源最少。

XCR3064XL器件

(1)XCR3064XL器件結構

XCR3064XL器件宏單元結構,由零功率互連陣列連線起來的功能塊及I/O單元構成,每個邏輯塊含16個宏單元。

全局互連結構CPLD

ispLSI1032器件結構

ispLSI1032器件主要由全局布線區GRP、通用邏輯塊GLB、輸入/輸出單元IOC、輸出布線區ORP和時鐘分配網路CDN構成。

2.通用邏輯塊GLB

通用邏輯塊GLB主要用於實現邏輯功能,GLB主要由與陣列、乘積項共享陣列、4輸出邏輯宏單元和控制邏輯電路組成。