基本RS

電路結構

RS觸發器

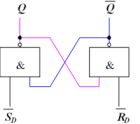

RS觸發器把兩個與非門或者或非門G1、G2的輸入、輸出端交叉連線,即可構成基本RS觸發器,其邏輯電路如右圖所示,為兩個與非門組成的RS觸發器。它有兩個輸入端R、S和兩個輸出端Q、Q非。

工作原理

RS觸發器

RS觸發器約束方程:SR=0

根據上述兩個式子得到它的四種輸入與輸出的關係:

1.當R端有效(1),S端無效時(0),則Q=1,Q非=0,觸發器置1;

2.當R端無效(0)、S端有效時(1),則Q=0,Q非=1,觸發器置0。

如上所述,當觸發器的兩個輸入端加入不同邏輯電平時,它的兩個輸出端Q和Q非有兩種互補的穩定狀態。一般規定觸發器Q端的狀態作為觸發器的狀態。通常稱觸發器處於某種狀態,實際是指它的Q端的狀態。Q=1、Q非=0時,稱觸發器處於1態,反之觸發器處於0態。S=0,R=1使觸發器置1,或稱置位。因置位的決定條件是S=0,故稱S 端為置1端。R=0,S=1時,使觸發器置0,或稱復位。

同理,稱R端為置0端或復位端。若觸發器原來為1態,欲使之變為0態,必須令R端的電平由1變0,S端的電平由0變1。這裡所加的輸入信號(低電平)稱為觸發信號,由它們導致的轉換過程稱為翻轉。由於這裡的觸發信號是電平,因此這種觸發器稱為電平控制觸發器。從功能方面看,它只能在S和R的作用下置0和置1,所以又稱為置0置1觸發器,或稱為置位復位觸發器。其邏輯符號如圖7.2.1(b)所示。由於置0或置1都是觸發信號低電平有效,因此,S端和R端都畫有小圓圈。

3.當RS端均無效時,觸發器狀態保持不變。

觸發器保持狀態時,輸入端都加非有效電平(高電平),需要觸發翻轉時,要求在某一輸入端加一負脈衝,例如在S端加負脈衝使觸發器置1,該脈衝信號回到高電平後,觸發器仍維持1狀態不變,相當於把S端某一時刻的電平信號存儲起來,這體現了觸發器具有記憶功能。

4.當RS端均有效時,觸發器狀態不確定。

在此條件下,兩個與非門的輸出端Q和Q非全為1,在兩個輸入信號都同時撤去(回到1)後,由於兩個與非門的延遲時間無法確定,觸發器的狀態不能確定是1還是0,因此稱這種情況為不定狀態,這種情況應當避免。從另外一個角度來說,正因為R端和S端完成置0、置1都是低電平有效,所以二者不能同時為0。

此外,還可以用或非門的輸入、輸出端交叉連線構成置0、置1觸發器,其邏輯圖和邏輯符號分別如圖7.2.2(a)和7.2.2(b)所示。這種觸發器的觸發信號是高電平有效,因此在邏輯符號的S端和R端沒有小圓圈。

抗抖作用

圖1

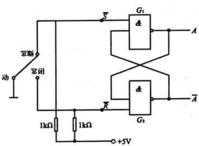

圖1RS觸發器一般用來抵抗開關的抖動。

為了消除開關的接觸抖動,可在機械開關與被驅動電路間接的接入一個基本RS觸發器,如圖1所示838電子。S為 =0, R=l,可得出A=l, A‘=0。當按壓按鍵時,S=l,R=0,可得出 A=0,A’=1,改變了輸出信號A的狀態。若由於機械開關的接觸抖動,則R的狀態會在0和1之間變化多次,若 R=l,由於A=0,因此G2門仍然是“有低出高”,不會影響輸出的狀態。同理,當鬆開按鍵時, S端出現的接觸抖動亦不會影響輸出的狀態。因此,圖1所示的電路,開關每按壓一次,A點的輸出信號僅發生一次變化。

單片機電路中的防抖現在一般都用程式防抖而不用觸發器這些硬體防抖了。

功能描述

1.狀態轉移真值表

用表格的形式描述觸發器在輸入信號作用下,觸發器的下一個穩定狀態(次態)Qn+1與觸發器的原穩定狀態(現態)Qn和輸入信號狀態之間的關係。

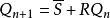

2.特徵方程

即以邏輯函式的形式來描述次態與現態及輸入信號之間的關係。由上述狀態轉移真值表,通過卡諾圖化簡可得到。

3.狀態轉移圖

即以圖形的方式描述觸發器的狀態變化對輸入信號的要求。圖7.2.4是基本RS觸發器的狀態轉移圖。圖中兩個圓圈代表觸發器的兩個狀態;箭頭表示在觸發器的輸入信號作用下狀態轉移的方向;箭頭旁邊由斜線“/”分開的代碼分別表示狀態轉移的條件和在此條件下產生的輸出狀態。 設觸發器的初始狀態為Q=0、Q=1,輸入信號波形如圖7.2.5所示,當SD的下降沿到達後,經過G1的傳輸延遲時間tpd,Q端變為高電平。這個高電平加到門G2的輸入端,再經過門G2的傳輸延遲時間tpd,使Q變為低電平。當Q的低電平反饋到G1的輸入端以後,即使SD=0的信號消失(即SD回到高電平),觸發器被置成Q=1狀態也將保持下去。可見,為保證觸發器可靠地翻轉,必須等到Q=0的狀態反饋到G1的輸入端以後,SD=0的信號才可以取消。因此,SD輸入的低電平信號寬度tw應滿足tw≥2tpd。同理,如果從RD端輸入置0信號,其寬度也必須大於、等於2tpd

2.傳輸延遲時間:

從輸入信號到達起,到觸發器輸出端新狀態穩定地建立起來為止,所經過的這段時間稱為觸發器的傳輸延遲時間。從上面的分析已經可以看出,輸出端從低電平變為高電平的傳輸延遲時間tPLH和從高電平變為低電平的傳輸延遲時間tPHL是不相等的,它們分別為: tPLH=tpd,tPHL=2tpd 若基本RS觸發器由或非門組成,則其傳輸延遲時間將為 tPHL=tpd,tPLH=2tpd 。綜上所述,對基本RS 觸發器歸納為以下幾點:

1.基本RS觸發器具有置位、復位和保持(記憶)的功能;

2.基本RS觸發器的觸發信號是低電平有效,屬於電平觸發方式;

3.基本RS觸發器存在約束條件(R+S=1),由於兩個與非門的延遲時間無法確定;當R=S=0時,將導致下一狀態的不確定。

4.當輸入信號發生變化時,輸出即刻就會發生相應的變化,即抗干擾性能較差。

同步RS 觸發器(時鐘脈衝控制的RS 觸發器)

前面介紹的基本RS觸發器的觸發翻轉過程直接由輸入信號控制 ,而實際上,常常要求系統中的各觸發器在規定的時刻按各自輸入信號所決定的狀態同步觸發翻轉,這個時刻可由外加的時鐘脈衝CP來決定。

電路結構:

如圖7.3.1所示在基本RS觸發器的基礎上增加G3、G4兩個與非門構成觸發引導電路,其輸出分別作為基本RS觸發器的R端和S端。

工作原理:

由圖7.3.1可知,G3和G4同時受CP信號控制,當CP為0時,G3和G4被封鎖, R、S不會影響觸發器的狀態;當CP為1時,G3和G4打開,將R、S端的信號傳送到基本RS觸發器的輸入端,觸發器觸發翻轉。結合基本RS觸發器的工作原理,我們可以得到以下結論。

1.當CP=0時 Q3=Q4=1,觸發器保持原來狀態不變。

2.當CP=1時若R=0 ,S=1; Q3=1,Q4=0,觸發器置1; 若R=1 ,S=0; Q3=0,Q4=1,觸發器置0; 若R=S=0; Q3=Q4=1,觸發器狀態保持不變; 若R=S=1; Q3=Q4=0,觸發器狀態不定;可見R端和S端都是高電平有效,所以R端和S端不能同時為1,其邏輯符號中的R端和S端也沒有小圓圈。

功能描述:

1.狀態轉移真值表

2.特徵方程

根據功能表及卡諾圖化簡,可得到如下表達式:

3.工作波形圖

工作波形圖即以波形的形式描述觸發器狀態與輸入信號及時鐘脈衝之間的關係,它是描述時序邏輯電路工作情況的一種基本方法。如圖7.3.2所示。圖中假設同步RS觸發器的初始狀態為0態。

同步RS觸發器的狀態轉移圖及激勵表請依照基本RS觸發器自行作出。

綜上所述,對同步RS觸發器歸納為以下幾點:

1.同步RS觸發器具有置位、復位和保持(記憶)功能; 2.同步RS觸發器的觸發信號是高電平有效,屬於電平觸發方式; 3.同步RS觸發器存在約束條件,即當R=S=1時將導致下一狀態的不確定; 4.觸發器的觸發翻轉被控制在一個時間間隔內,在此間隔以外的時間內,其狀態保持不變,抗干擾性有所增強。

硬體語言

//採用門級描述的RS觸發器

module RS_FF(R,S,Q,QB);

input R,S;

output Q,QB;

nand (Q,R,QB);

nand (QB,S,Q);

endmodule

////////////////////////////

//採用行為描述的RS觸發器

module RS_FF(R,S,Q,QB);

input R,S;

output Q,QB;

reg Q;

assign QB=~Q;

always@(Ror S)

case({R,S})

2'b01:Q<=1;

2'b10:Q<=0;

2'b11:Q<=1'bx;

endcase

endmodule

/////////////////////////////////

//verilog描述的同步RS觸發器

module SYRS_FF(R,S,CLK,Q,QB);

input R,S,CLK;

output Q,QB;

reg Q;

assign QB=~Q;

always @(posedge CLK)

case({R,S})

2'b01:Q<=1;

2'b10:Q<=0;

2'b11:Q<=1'bx;

endcase

endmodule