邊沿D 觸發器

負跳沿觸發的主從觸發器工作時,必須在正跳沿前加入輸入信號。如果在CP 高電平期間輸入端出現干擾信號,那么就有可能使觸發器的狀態出錯。而邊沿觸發器允許在CP 觸發沿來到前一瞬間加入輸入信號。這樣,輸入端受干擾的時間大大縮短,受干擾的可能性就降低了。邊沿D觸發器也稱為維持-阻塞邊沿D觸發器。

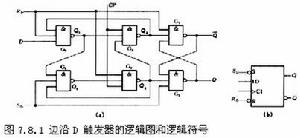

電路結構: 該觸發器由6個與非門組成,其中G1和G2構成基本RS觸發器。

D觸發器

D觸發器工作原理:

D觸發器

D觸發器1.CP=0時,與非門G3和G4封鎖,其輸出Q3=Q4=1,觸發器的狀態不變。同時,由於Q3至Q5和Q4至Q6的反饋信號將這兩個門打開,因此可接收輸入信號D,Q5=D,Q6=Q5=D。

2.當CP由0變1時觸發器翻轉。這時G3和G4打開,它們的輸入Q3和Q4的狀態由G5和G6的輸出狀態決定。Q3=Q5=D,Q4=Q6=D。由基本RS觸發器的邏輯功能可知,Q=D。

3.觸發器翻轉後,在CP=1時輸入信號被封鎖。這是因為G3和G4打開後,它們的輸出Q3和Q4的狀態是互補的,即必定有一個是0,若Q3為0,則經G3輸出至G5輸入的反饋線將G5封鎖,即封鎖了D通往基本RS 觸發器的路徑;該反饋線起到了使觸發器維持在0狀態和阻止觸發器變為1狀態的作用,故該反饋線稱為置0維持線,置1阻塞線。Q4為0時,將G3和G6封鎖,D端通往基本RS觸發器的路徑也被封鎖。Q4輸出端至G6反饋線起到使觸發器維持在1狀態的作用,稱作置1維持線;Q4輸出至G3輸入的反饋線起到阻止觸發器置0的作用,稱為置0阻塞線。因此,該觸發器常稱為維持-阻塞觸發器。總之,該觸發器是在CP正跳沿前接受輸入信號,正跳沿時觸發翻轉,正跳沿後輸入即被封鎖,三步都是在正跳沿後完成,所以有邊沿觸發器之稱。與主從觸發器相比,同工藝的邊沿觸發器有更強的抗干擾能力和更高的工作速度。功能描述

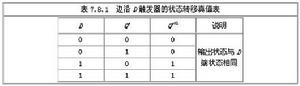

1.狀態轉移真值表

D觸發器

D觸發器2.特徵方程 Qn+1=D

3.狀態轉移圖

脈衝特性:

1.建立時間:由圖7.8.4維持阻塞觸發器的電路可見,由於CP信號是加到門G3和G4上的,因而在CP上升沿到達之前門G5和G6輸出

D觸發器

D觸發器2.保持時間:由圖7.8.4可知,為實現邊沿觸發,應保證CP=1期間門G6的輸出狀態不變,不受D端狀態變化的影響。為此,在D=0的情況下,當CP上升沿到達以後還要等門G4輸出的低電平返回到門G6的輸入端以後,D端的低電平才允許改變。因此輸入低電平信號的保持時間為tHL≥tpd。在 D=1的情況下,由於CP上升沿到達後G3的輸出將G4封鎖,所以不要求輸入信號繼續保持不變,故輸入高電平信號的保持時間tHH=0。

3.傳輸延遲時間:由圖7.8.3不難推算出,從CP上升沿到達時開始計算,輸出由高電平變為低電平的傳輸延遲時間tPHL和由低電平變為高電平的傳輸延遲時間tPLH分別是:tPHL=3tpd tPLH=2tpd

4.最高時鐘頻率:為保證由門G1~G4組成的同步RS觸發器能可靠地翻轉,CP高電平的持續時間應大於 tPHL,所以時鐘信號高電平的寬度tWH應大於tPHL。而為了在下一個CP上升沿到達之前確保門G5和G6新的輸出 電平得以穩定地建立,CP低電平的持續時間不應小於門G4的傳輸延遲時間和tset之和,即時鐘信號低電平的寬度tWL≥tset+tpd,因此得到:

最後說明一點,在實際集成觸發器中,每個門傳輸時間是不同的,並且作了不同形式的簡化,因此上面討論的結果只是一些定性的物理概念。其真實參數由實驗測定。

集成觸發器

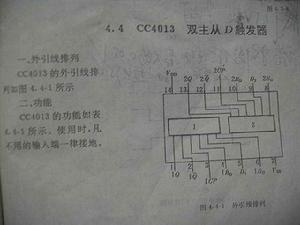

集成D觸發器的定型產品種類比較多,這裡介紹雙D觸發器74HC74,實際上,74型號的產品種類較多,比如還有7474、74H74等。

D觸發器

D觸發器通過圖7.8.5中的邏輯符號和D觸發器74HC74的邏輯功能表我們可以看出,HC74是帶有預置、清零輸入,上跳沿觸發的邊沿觸發器。

綜上所述,對邊沿D觸發器歸納為以下幾點:

1.邊沿D觸發器具有接收並記憶信號的功能,又稱為鎖存器; 2.邊沿D觸發器屬於脈衝觸發方式; 3.邊沿D觸發器不存在約束條件和一次變化現象,抗干擾性能好,工作速度快。