概念

MIS器件:由金屬(M)-絕緣體(I)-半導體(S)組成的體系稱為MIS結構,以這種結構形成的器件稱為MIS器件(MIS二極體)。

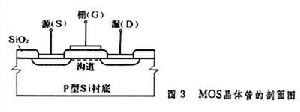

如果其中的絕緣體是SiO2,則相應地為MOS結構和MOS二極體。

(一)MIS器件的基本功能:

MIS器件的功能主要決定於其中絕緣體層的厚度:

(1)假若絕緣體層的厚度足夠大(對於絕緣體層是SiO2層的情況,大於5nm),則基本上不導電,這時即為MIS電容器;

(2)假若絕緣體層的厚度足夠薄(對於絕緣體層是SiO2層的情況,大約為1nm),則絕緣體基本上不起阻擋導電的作用(阻抗極小),這時即為schottky二極體;

(3)假若絕緣體層的厚度不是很薄、也不是很厚(對於絕緣體層是SiO2層的情況,大約為1nm~5nm),則這時載流子有較大的幾率通過隧道效應而穿過絕緣體層,這種結構的器件即稱為MIS隧道二極體。

(二)MIS隧道器件:

由於MIS隧道二極體的獨特性能,具有許多用途,現在已經發展成了一大族的器件(MIS隧道器件),如MIS太陽電池、MIS開關管、MIM隧道二極體、MIMIM隧道電晶體等。

詳解

以Al為柵電極時,稱鋁柵器件。以重摻雜多晶矽(Poly-Si)為柵電極時,稱矽柵器件。它是當前MOS器件的主流器件。矽柵工藝是利用重摻雜的多晶矽來代替鋁做為MOS管的柵電極,使MOS電路特性得到很大改善,它使VTP下降1.1V,也容易獲得合適的VTN值並能提高開關速度和集成度。

示意圖

示意圖矽柵工藝具有自對準作用,這是由於矽具有耐高溫的性質。柵電極,更確切的說是在柵電極下面的介質層,是限定源、漏擴散區邊界的擴散掩膜,使柵區與源、漏交迭的密勒電容大大減小,也使其它寄生電容減小,使器件的頻率特性得到提高。另外,在源、漏擴散之前進行柵氧化,也意味著可得到淺結。selfalignedpoly-siliconprocess自對準多晶矽工藝

鋁柵工藝為了保證柵金屬與漏極鋁引線之間有一定的間隔,要求漏擴散區面積要大些。而在矽柵工藝中覆蓋源漏極的鋁引線可重迭到柵區,這是因為有一絕緣層將柵區與源漏電極引線隔開,從而可使結面積減少30%~40%。

矽柵工藝還可提高集成度,這不僅是因為擴散自對準作用可使單元面積大為縮小,而且因為矽柵工藝可以使用“二層半布線”即一層鋁布線,一層重摻雜多晶矽布線,一層重摻雜的擴散層布線。由於在製作擴散層時,多晶矽要起掩膜作用,所以擴散層不能與多晶矽層交叉,故稱為兩層半布線.鋁柵工藝只有兩層布線:一層鋁布線,一層擴散層布線。矽柵工藝由於有兩層半布線,既可使晶片面積比鋁柵縮小50%又可增加布線靈活性。

當然,矽柵工藝較之鋁柵工藝複雜得多,需增加多晶矽澱積、等離子刻蝕工序,而且由於表面層次多,台階比較高,表面斷鋁,增加了光刻的困難,所以又發展了以Si3N4作掩膜的局部氧化LOCOS--Localoxidationonsilicon(又稱為MOSIC的局部氧化隔離工藝LocalOxidationIsolationforMOSIC),或稱等平面矽柵工藝。

擴散條連線由於其電容較大,漏電流也較大,所以儘量少用,一般是將相應管子的源或漏區加以延伸而成。擴散條也用於短連線,注意擴散條不能跨越多晶矽層,有時把這層連線稱為“半層布線”。因硼擴散薄層電阻為30~120Ω/□,比磷擴散的R□大得多,所以硼擴散連線引入的分布電阻更為可觀,擴散連線的寄生電阻將影響輸出電平是否合乎規範值,同時也因加大了充放電的串聯電阻而使工作速度下降。因此,在CMOS電路中,當使用硼擴散條做連線用時要考慮到這一點。

當在NMOS的柵上施加相對於源的正電壓VGS時,柵上的正電荷在P型襯底上感應出等量的負電荷,隨著VGS的增加,襯底中接近矽-二氧化矽界面的表面處的負電荷也越多。其變化過程如下:當VGS比較小時,柵上的正電荷還不能使矽-二氧化矽界面處積累可運動的電子電荷,這是因為襯底是P型的半導體材料,其中的多數載流子是正電荷空穴,柵上的正電荷首先是驅趕表面的空穴,使表面正電荷耗盡,形成帶固定負電荷的耗盡層。

這時,雖然有VDS的存在,但因為沒有可運動的電子,所以,並沒有明顯的源漏電流出現。增加VGS,耗盡層向襯底下部延伸,並有少量的電子被吸引到表面,形成可運動的電子電荷,隨著VGS的增加,表面積累的可運動電子數量越來越多。這時的襯底負電荷由兩部分組成:表面的電子電荷與耗盡層中的固定負電荷。如果不考慮二氧化矽層中的電荷影響,這兩部分負電荷的數量之和等於柵上的正電荷的數量。當電子積累達到一定水平時,表面處的半導體中的多數載流子變成了電子,即相對於原來的P型半導體,具有了N型半導體的導電性質,這種情況稱為表面反型。

根據電晶體理論,當NMOS電晶體表面達到強反型時所對應的VGS值,稱為NMOS電晶體的閾值電壓VTN(ThresholdvoltageforN-channeltransistor)。這時,器件的結構發生了變化,自左向右,從原先的n+-p-n+結構,變成了n+-n-n+結構,表面反型的區域被稱為溝道區。在VDS的作用下,N型源區的電子經過溝道區到達漏區,形成由漏流向源的漏源電流。顯然,VGS的數值越大,表面處的電子密度越大,相對的溝道電阻越小,在同樣的VDS的作用下,漏源電流越大。

當VGS大於VTN,且一定時,隨著VDS的增加,NMOS的溝道區的形狀將逐漸的發生變化。在VDS較小時,溝道區基本上是一個平行於表面的矩形,當VDS增大後,相對於源端的電壓VGS和VDS在漏端的差值VGD逐漸減小,並且因此導致漏端的溝道區變薄,當達到VDS=VGS-VTN時,在漏端形成了VGD=VGS-VDS=VTN的臨界狀態,這一點被稱為溝道夾斷點,器件的溝道區變成了楔形,最薄的點位於漏端,而源端仍維持原先的溝道厚度。器件處於VDS=VGS-VTN的工作點被稱為臨界飽和點。

在逐漸接近臨界狀態時,隨著VDS的增加,電流的變化偏離線性,NMOS電晶體的電流-電壓特性發生彎曲。在臨界飽和點之前的工作區域稱為非飽和區,顯然,線性區是非飽和區中VDS很小時的一段。繼續在一定的VGS條件下增加VDS(VDS>VGS-VTN),在漏端的導電溝道消失,只留下耗盡層,溝道夾斷點向源端趨近。由於耗盡層電阻遠大於溝道電阻,所以這種向源端的趨近實際上位移值∆L很小,漏源電壓中大於VGS-VTN的部分落在很小的一段由耗盡層構成的區域上,有效溝道區內的電阻基本上維持臨界時的數值。因此,再增加源漏電壓VDS,電流幾乎不增加,而是趨於飽和。

這時的工作區稱為飽和區,左圖顯示了器件處於這種狀態時的溝道情況,右圖是完整的NMOS電晶體電流—電壓特性曲線。圖中的虛線是非飽和區和飽和區的分界線,VGS<VTN的區域為截止區。

事實上,由於∆L的存在,實際的溝道長度L將變短,對於L比較大的器件,∆L/L比較小,對器件的性能影響不大,但是,對於短溝道器件,這個比值將變大,對器件的特性產生影響。器件的電流-電壓特性在飽和區將不再是水平直線的性狀,而是向上傾斜,也就是說,工作在飽和區的NMOS器件的電流將隨著VDS的增加而增加。這種在VDS作用下溝道長度的變化引起飽和區輸出電流變化的效應,被稱為溝道長度調製效應。衡量溝道長度調製的大小可以用厄萊(Early)電壓VA表示,它反映了飽和區輸出電流曲線上翹的程度。受到溝道長度調製效應影響的NMOS伏-安特性曲線如圖所示。

雙極性電晶體的輸出特性曲線形狀與MOS器件的輸出特性曲線相似,但線性區與飽和區恰好相反。MOS器件的輸出特性曲線的參變數是VGS,雙極性電晶體的輸出特性曲線的參變數是基極電流IB。

衡量溝道長度調製的大小可以用厄萊(Early)電壓VA表示,它反映了飽和區輸出電流曲線上翹的程度。