自對準技術

self-alignment technique

微電子技術中利用元件、器件結構特點實現光複印自動對準的技術。早期的 MOS積體電路採用的是鋁柵工藝,首先在矽單晶片上熱氧化生長一層二氧化矽膜,經第一次光刻,在二氧化矽膜上刻蝕出源和漏擴散視窗,用擴散法形成源和漏擴散區 (圖1aMOS積體電路鋁柵工藝),接著在矽片上形成新的二氧化矽層;再經過第二次光刻,刻蝕出柵區,生長柵氧化層;然後,經光刻刻出引線孔,完成蒸鋁和刻鋁等後工序;最後形成MOS電晶體。因為柵區必須在源和漏擴散區正中間,並需要稍覆蓋源區和漏區,第二次光刻以及形成鋁柵電極的那步光刻,都必須和第一次光刻的位置精確對準(圖1bMOS積體電路鋁柵工藝)。否則,柵區與源區或漏區就可能銜接不上,使溝道斷開(圖1cMOS積體電路鋁柵工藝),致使MOS電晶體無法工作。因此,設計這類電晶體時往往讓柵區寬度(柵氧化膜及其上的鋁柵電極兩者)比源和漏擴散區的間距要大一些,光刻時使柵區的兩端分別落在源和漏擴散區上並有一定餘量,由此便產生了較大的柵對源、漏的覆蓋電容,使電路的開關速度降低。

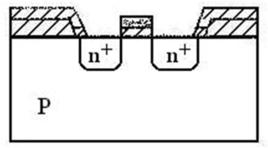

隨矽柵工藝的發展,已實現柵與源和漏的自對準。這種工藝是先在生長有柵氧化膜的矽單晶片上澱積一層多晶矽,然後在多晶矽上刻蝕出兩個擴散視窗,雜質經視窗熱擴散到矽單晶片內,形成源和漏擴散區(圖2MOS矽柵工藝自對準示意圖),同時形成導電的多晶矽柵電極,其位置自動與源和漏的位置對準。按照這種自對準工藝,柵與源和漏的覆蓋由雜質側向擴散完成,比鋁柵工藝的覆蓋電容要小很多。採用離子注入摻雜工藝的雜質側向擴散更小,用它代替矽柵工藝中的熱擴散工藝,能進一步減小柵對源和漏的覆蓋電容。此外,在鋁柵工藝中,即使鋁柵電極比溝道短,也可增加一步離子注入工藝填充柵區旁的未銜接部分,實現自對準(圖3MOS鋁柵工藝實現自對準的示意圖),藉以減小寄生電容,可提高MOS積體電路的開關速度和工作頻率,同時也減小器件尺寸而提高電路的集成度。

在雙極型電晶體及其積體電路的製造中,也多採用自對準工藝。例如,用微米級線寬的多晶矽發射極作掩模,再擴散雜質形成濃基區,以實現發射極與基區的自對準。又如超自對準工藝的主要工序是用通常方法完成基區摻雜後,在矽片上澱積一層未摻雜多晶矽,氧化掉不必要的部分。在整個晶片上澱積氮化矽膜層和二氧化矽膜層。除發射區和集電極接觸孔外,其他部位的二氧化矽膜全腐蝕掉。以二氧化矽膜作掩模,把硼注入到未摻雜多晶矽內,然後腐蝕掉氮化矽(稍微過腐蝕一點)。再採用選擇腐蝕法把未摻雜多晶矽腐蝕去,暴露的基區寬度小於1微米。採用熱氧化,同時形成P□區。去掉氮化矽,不用掩模進行硼注入,自對準形成P□基區。再在多晶矽發射極中摻入砷,擴散形成發射區。其他後續工序與通常的雙極型積體電路工藝相同。用這種方法製成的雙極型電晶體,實現了多晶矽發射極與P+基區的自對準,有較小的基區電阻和較小的發射極-基極結電容,多晶矽發射極和多晶矽基極間距小於1微米,提高了雙極型積體電路的速度,也提高了電路的集成度。用這種技術已製成存取時間為2.7納秒發射極耦合邏輯電路的1千位隨機存儲器。