電晶體-電晶體邏輯電路

正文

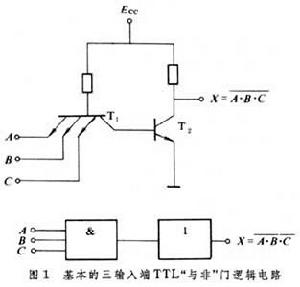

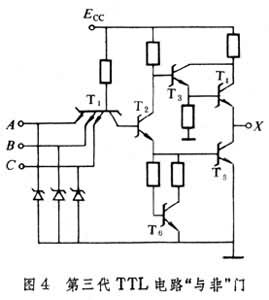

積體電路輸入級和輸出級全採用電晶體組成的單元門電路,簡稱TTL電路。它是從二極體-電晶體邏輯電路(DTL)發展而來的。將DTL電路輸入端的“與”門二極體組和電平位移二極體之一,改為多發射極電晶體,多發射極實現輸入級“與”邏輯,輸出級電晶體實現“非”邏輯,即成為TTL基本邏輯門電路的結構(圖1)。 電晶體-電晶體邏輯電路

電晶體-電晶體邏輯電路 電晶體-電晶體邏輯電路

電晶體-電晶體邏輯電路TTL電路輸入端採用多發射極電晶體,不再象DTL電路輸入端二極體組與電平位移二極體那樣彼此孤立。多發射極電晶體具有較大的正向電流放大係數和較小的反向電流放大係數。電路處於轉換過程中,當輸入端為低電平時,較大的正向電流放大係數能抽出較大的電流,使原來存儲的多餘載流子很快消失;當輸入端是高電平時,較小的反向電流放大係數,使多發射極電晶體的反向漏電流最小,不致影響前一級高電平輸出。採用多發射極電晶體時,在多發射極之間須避免出現交叉漏電流。

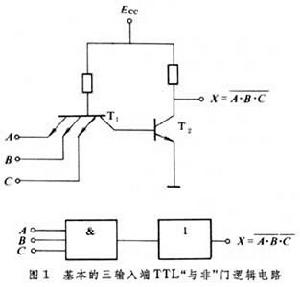

電路輸出級採用推拉輸出,有助於減小電路功耗和提高開關速度。輸出上推拉管 T4和二極體D代替原輸出管T5負載電阻,構成一個能自動調節阻值的負載,使電路只在轉換過程的瞬間輸出級才有功耗。

電晶體-電晶體邏輯電路

電晶體-電晶體邏輯電路 電晶體-電晶體邏輯電路

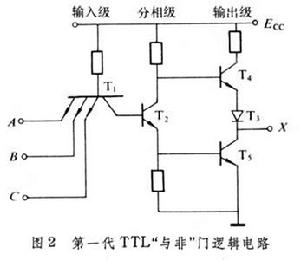

電晶體-電晶體邏輯電路飽和型電晶體分流器要求R3<R6(如R3=0.5R6),T6管即能進入飽和區。因為當“與非”門T5管截止時,電晶體分流器可為T5管提供一個低阻的抽出電流的分流迴路,有利於T5管截止,提高開關速度。

非飽和型電晶體分流器是指R6=0。這時,T6管工作線上性區域,不論T5管在通導過程中還是轉向截止,這種分流器對提高電路開關速度的能力都是有限的。

淺飽和型電晶體分流器要求R3>R6(在一般情況下,取R6=0.5R3),使電路處於飽和邊緣,從而獲得高速開關能力。因此,在高速開關電路中,一般採用淺飽和型電晶體分流器。

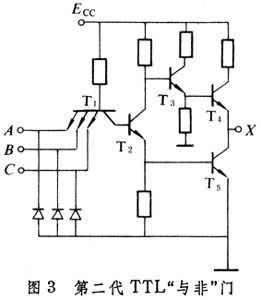

在早期探索提高 TTL邏輯電路“與非”門開關速度的過程中,只是採取兩方面的措施:①降低電路中的阻值,因為降低阻值可增加驅動電流。縮小電路所占的晶片面積,寄生電容也因之減小;②輸出級上推拉管和二極體改為射極跟隨器連線法,使TTL“與非”門邏輯電路開關速度成倍提高。但是在進一步探索提高電路速度時,發現電晶體多餘載流子的存儲效應是一個重要障礙。這些多餘載流子的產生,是由於過驅動電流導致電晶體進入飽和狀態,多餘的載流子又來不及複合消失,勢必存儲在電晶體區內。為了進一步提高開關速度,只有設法使電晶體處於臨界飽和狀態,避免對電晶體過驅動才有可能消除和避免多餘載流子的存儲效應。因此,60年代末至70年代初期,開始在TTL積體電路中採用肖特基勢壘二極體,將其並接在電路電晶體的基極和集電極上,終於把電路存儲時間大大縮短。TTL電路“與非”門開關速度進入超高速範圍,使帶有肖特基勢壘二極體的電晶體的開關時間可縮短到1納秒左右。

TTL電路按用途區分,還包括一些特殊用途的電路,如普通常用的基本門、功率門或驅動器、集電極開路門、抗輻照基本門和三態輸出基本門。

參考書目

汪希時編著:《電晶體-電晶體邏輯積體電路與數位技術》,科學出版社,北京,1982。