電阻-電晶體邏輯電路

正文

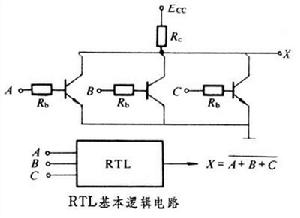

由電晶體和串接在電晶體基極上的電阻組成以實現“或非”邏輯操作的單元門電路,簡稱RTL電路。RTL電路的每一個邏輯輸入端各有一個電晶體,每一輸入級電晶體基極串接一個等值電阻,全部電晶體共發射極並聯接地,集電極直接耦合,有一個公共負載電阻為輸出端,實現“或非”邏輯操作。由圖 可知,去掉每個輸入端電阻Rb,RTL電路就變為直接耦合電晶體邏輯電路(DCTL),所以RTL電路有時也叫作補償 DCTL電路。DCTL電路存在嚴重的“搶電流”問題,因而無法實用,很快為RTL電路所取代。RTL電路是最早研製成功的一種有實用價值的積體電路。有N 個門的輸入端並接在DCTL電路輸出端,因為DCTL電路輸出端門的電晶體基極導通電壓,電流曲線並不能完全一致,並聯在一起,輸入電流易出現分配不均勻的現象。輸入電流小的負載門可能得不到足夠的基極驅動電流,達不到飽和,從而輸出端可能從應有的“0”態改變到“1”狀態,使系統出現差錯。負載輸入端並接越多,產生電流分配不勻的可能性越大。這種現象叫作“搶電流”。 電阻-電晶體邏輯電路

電阻-電晶體邏輯電路 -Ib特性的依賴性小一些。根據 Rb的阻值即可確定RTL電路的最大負載門數。

-Ib特性的依賴性小一些。根據 Rb的阻值即可確定RTL電路的最大負載門數。 RTL電路結構簡單,元件少。RTL電路的嚴重缺點是基極迴路有電阻存在,從而限制了電路的開關速度,抗干擾性能也差,使用時負載又不能過多。RTL電路是一種飽和型電路,只適用於低速線路,實際上已被淘汰。為了改善RTL邏輯電路的開關速度,在基極電阻上再並接一個電容,就構成了電阻-電容-電晶體邏輯電路(RCTL)。有了電容,不僅可以加快開關速度,而且還可以加大基極電阻,從而減小電路功耗。但是,大數值電阻和電容在積體電路製造工藝上要占去較大的晶片面積,而且取得同樣容差值的設計也比較困難。因此,RCTL電路實際上也沒有得到發展。

參考書目

汪希時編著:《電晶體-電晶體邏輯積體電路與數位技術》,科學出版社,北京,1982。