Intel

Intel技術原理詳解

32納米製程技術是基於45納米技術的改良版本,總體歸納起來組要有以下三點。

1.32納米製程技術的基礎是第二代高k+金屬柵極電晶體

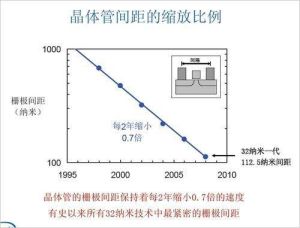

英特爾對第一代高k+金屬柵極電晶體進行了眾多改進。在45納米製程中,高k電介質的等效氧化層厚度為1.0納米。而在32納米製程中,由於在關鍵層上首次使用沉浸式光刻技術,所以此氧化層的厚度僅為0.9納米,而柵極長度則縮短為30納米。電晶體的柵極間距每兩年縮小0.7倍——32納米製程採用了業內最緊湊的柵極間距(第一代32nm技術將使112.5nm柵極間距)。32納米製程採用了與英特爾45納米製程一樣的置換金屬柵極工藝流程,這樣有利於英特爾充分利用現有的成功工藝。這些改進對於縮小積體電路(IC)尺寸、提高電晶體的性能至關重要。

採用高k+金屬柵極電晶體的32納米製程技術可以幫助設計人員同時最佳化電路的尺寸和性能。由於氧化層厚度減小,柵極長度縮短,電晶體的性能可以提高22%以上。這些電晶體的驅動電流和柵極長度創造了業內最佳紀錄。

英特爾的第一顆32納米SRAM晶片在2007年9月就已經完成,電晶體數量超過19億個,單元面積0.171平方微米,容量291Mb,運行速度4GHz,相對比而言,45nm時代處理器的單元面積是0.346平方微米(AMD的是0.370平方微米)。

2.32納米技術針對漏電電流做出了最佳化

與45納米製程相比,NMOS電晶體的漏電量減少5倍多,pmos電晶體的漏電量則減少10倍以上。換句話講,根據NMOS、PMOS電晶體泄漏電流和驅動電流的對比,32nm的能效相比45nm會有明顯提高──要么能在同樣的漏電率下提高電晶體速度(14-22%),要么能在同樣的速度下降低漏電率(5-10倍)。因此由於上述改進,電路的尺寸和性能均可得到顯著最佳化。

3.32納米採用了第四代應變矽技術

可將電晶體體積縮小大約30%,從而有利於提高電晶體的性能,同時也使得英特爾可以爭取更多的時間和機會進行更多技術創新。

測試晶片證明

2007年9月首次亮相的32納米SRAM測試晶片不僅證明了32納米製程的正確性,而且證明了摩爾定律的正確性。利用32納米技術,英特爾能夠將SRAM存儲單元的尺寸從45納米製程技術下的0.346平方微米縮小到的0.171平方微米。

回顧之前採用的製程技術,英特爾延續了每兩年將電晶體尺寸(例如,使電晶體密度翻倍的能力)縮小50%的發展趨勢。該測試晶片的尺寸和複雜程度也證明了這種製程技術的正確性。該測試晶片集成度高(超過19億個電晶體)、密度大(291Mbit)、速度快(4GHz運行),而且,作為一款出色的工具(測試晶片),它證實了提高產量的可行性、性能、可靠性,從而為生產32納米處理器產品做好充分準備。

產品

基於已為全球用戶高度認可的英特爾全新酷睿™ 微體系架構、業界領先的32納米製程工藝以及創新的智慧型計算理念,英特爾公司新一代智慧型伺服器處理器——英特爾® 至強處理器5600系列(研發代號為Westmere-EP)於2010年3月17日正式上市。該系列處理器主要用於雙路伺服器和工作站系統,可為分布於不同行業和專注於不同套用領域的用戶帶來更加出色的計算性能及能效,尤其適用於大規模數據中心、高性能計算、雲計算和其他數據密集型套用環境,可在這些環境中幫助用戶提高工作效率,同時解決他們在伺服器部署、套用及維護中面臨的問題和挑戰。