薄層電阻測量技術

正文

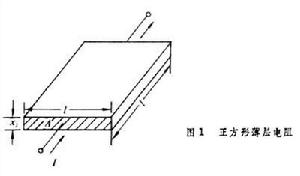

薄層電阻是指一塊正方形薄層沿其對邊平面方向的電阻,單位為Ω/□(圖1)。若正方形薄層的邊長為l,厚度為xj,截面積為A,平均電阻率為 ,薄層電阻Rs為

,薄層電阻Rs為

薄層電阻測量技術

薄層電阻測量技術 薄層電阻測量技術

薄層電阻測量技術

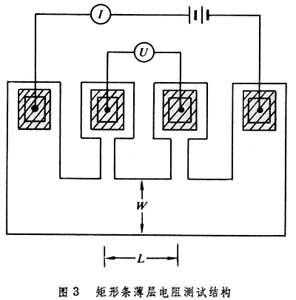

在矽平面工藝中,往往通過一些專門設計的測試圖形來檢測薄層電阻。這些圖形形成在晶片邊緣,或者專門的測試片上(與其他參數的測試圖形一起),它們和積體電路晶片同時經歷各項工藝步驟。通過這樣一些測試圖形測得的薄層電阻,更加準確地反映器件和電路中的實際情況。若在大圓矽片上作成布滿測試圖形的陣列,還可得到整個圓片上薄層電阻值分布的均勻性。

薄層電阻測量技術

薄層電阻測量技術

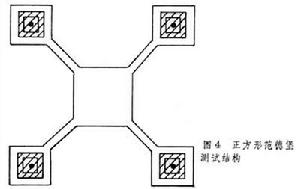

正方形范德堡測試結構中(圖4),正中是需要測量的正方形薄層。測量時,從任一邊的兩個歐姆接觸點通入電流I,從對邊的兩個歐姆接觸點測量電壓U。由於圖形的高度對稱,若在此局部範圍內薄層電阻的平面分布均勻,則薄層電阻值Rs為

薄層電阻測量技術

薄層電阻測量技術