發展概述

對於傳統的馮.諾依曼結構的計算機,是屬於標準串列機,大部分工作是在存儲器和ALU之間交換數據,而數據的流動速率限制了計算機的速度,這也就是通常所說的瓶頸效應,它很難完成實時高速的圖像處理工作。

隨著PCI匯流排的出現,這個問題得到了一定的解決,有人把數據傳輸的時間壓縮在13ms,剩下的27ms用來處理算法,但是,現在隨著處理的複雜性加大,算法也越來越複雜,這種處理是準實時的。因此,多處理器系統、並行處理結構計算機成為發展的必然趨勢。

並行處理是利用計算過程中的並發性事件進行有效的信息處理,並發性含有並行性、同時性和流水線三種含義。並行時間可在同一時間間隔內在多重資源中發生,同時性事件是在同一瞬間發生,而流水線事件可在重疊的時間段發生。這些並發性事件可以在計算機系統的各處理級獲得。最高級並行處理是通過多道、分時和多處理來實施多作業或多程式,該級需要研究並行處理的算法.,通過並行算法把有限的軟硬體資源有效的配置給求解大的計算問題的多個程式;次高級並行處理是實施同一程式內部的過程和任務,這涉及把一個程式分解為多個任務;第三級是利用多條指令的並發性,通過指令的並發性達到快速的並發作業。

並行處理不僅在計算機中得到套用,其處理思想也貫徹到硬體電路的各個方面。數字圖像處理系統在硬體結構方面也發生了重大變化,即已由基本的串列結構發展成並行處理結構,由單處理器發展成多處理器系統,或帶陣列處理器的高速處理系統。隨著並行結構理論、並行算法和語言、VLSI技術及CAD工具的發展,並行處理器陣列現已被廣泛套用於通信、生物醫學、工業檢測和軍事等各個方面,也成為滿足實時圖像處理超高強度運算能力要求的一個有效途徑。

圖像處理技術、壓縮編碼技術的不斷發展和完善,以及VLSI技術的迅猛發展使得用硬體電路實現實時圖像處理成為可能。隨著綜合業務數字網(ISDN)的不斷推廣以及多媒體技術的興起,圖像實時處理在各個領域得到了廣泛的套用。近年來不斷湧現的各種高性能的專用晶片,數位訊號處理器(DSP)以及超大規模可程式邏輯器件(FPGA/ASIC),使現代實時圖像處理系統的設計和以往相比已不可同日而語。過去的一個機箱,甚至一個機櫃的信號處理系統,現在完全可以集成在單個晶片上。可程式邏輯器件的出現,使得硬體設計人員可根據套用系統需要,通過軟體設計編程來實現大規模數字邏輯控制電路。

技術

技術要求

圖像處理系統接收的圖像數據由兩部線陣ccD攝像機周視掃描實時獲得。一部為有雷射照射的前景攝像機,獲得前景圖像;另一部為無雷射照射的背景攝像機,獲得背景圖像。前景圖像數據接口和背景圖像數據接口均包括8bit圖像灰度數據、時鐘信號、列同步信號以及列結尾信號。接口電平特性符合RS644(LVDS)接口電平要求。線陣CCD攝像機按列掃描,每列像素點為512個,這裡約定400列為一幅圖像,認為一幅圖像為512 X 400像素的灰度圖像。實時圖像處理系統以每秒鐘80幅圖像的速度接收圖像數據,之後,進行相關圖像處理,並將相關處理結果實時上報至上位機。

實時圖像處理系統的主要技術要求有:

(1)實時性要求,且圖像處理系統必須具有多目標處理能力。為滿足實時性要求,每幅圖像的處理(包括圖像數據傳輸、算法運算、上位機命令解析與通信等)耗時不能超過12.5ms。

(2)嵌入性要求,實時圖像處理系統為典型的定製嵌入式系統,在結構尺寸、輸入輸出接口、功耗上均有嚴格限制:圖像數據輸入接口定義、通過乙太網與上位機進行通信;系統220V交流輸入供電,整機功耗在25W以下。

(3)適應性要求,圖像處理系統需要完成高溫、低溫、濕熱、衝擊、振動等環境適應性試驗。

套用和需求

實現圖像處理技術的套用是多方面的,可以說,凡是在圖像處理技術套用的地方都可以套用實時圖像處理技術,原因在於實時圖像處理技術可以提高圖像處理的速度。但是,這要付出一定的代價,這種代價包括設備上和開發上的代價。在可用、不可用的地方,代價問題會成為考慮的重點,而在必須套用的地方,考慮的重點則是實時圖像處理系統的性能及可行性。從套用圖像處理技術的緊迫性來看,其套用領域主要集中在消費類產品、軍事、工業自動化以及公安的形式偵察上,在這些領域強有力的推動下,實時圖像處理技術得到了迅速的發展。對圖像處理系統和並行圖像處理技術最前沿技術得跟蹤和掌握,及針對圖像處理系統的走勢,無疑高速率、高質量的實時圖像顯示畫面將代表著未來十幾年,甚至幾十年的圖像處理系統的發展方向。

圖像並行處理技術是圖像處理中的一個重要方面,是提高圖像處理速度的最有效技術,其發展水平一直受到圖像界的關注,原因在於:一方面,圖像並行處理技術的發展難度很大,這種難度不僅在於圖像並行處理系統的硬體及系統結構本身,以及它對計算機技術和積體電路等技術的依賴關係,而且在於實際套用的複雜性和套用部門對系統價格的承受能力;另一方面,圖像並行處理技術的發展所產生的效益也是十分顯著的,它在處理速度上所獲得的加速比是令人振奮的,其實際套用系統也將產生很大的經濟效益和社會效益。

FPGA與實時圖像處理

實時圖像處理系統是指定時採集圖像、分析圖像以獲得數據,並用這些數據來控制一些行為的系統。所有的處理必須發生在事先定義的時間內(通常是圖像採集速率)。也就是說,整個圖像處理算法的執行必須在有限的時間內完成,這就意味著某些操作級的算法將被排除在實時處理之外。例如基於疊代或遞歸算法的操作,必須在事先確定的重複操作次數後可以得到滿意的收斂的情況下才能夠使用。

實時圖像處理系統的例子有很多,在機器視覺中,通常用圖像處理算法來實現路徑規劃和過程控制,在這些場合,時間點是非常重要的。自主車輛控制需要利用視覺或其他形式的感測器使車輛實現動態環境下的導航或避障。在視頻傳輸系統中,圖像的連續幀必須以正確的順序傳輸和顯示並且使跳動最小化,以避免在最終的視頻圖像上出現質量損失。在圖像採集和顯示的套用系統中,時間限制的數量級為幾十納秒,因此需要採用硬體完成。

FPGA通過為每個功能建立單獨的硬體來實現整個系統所需要的邏輯,具有硬體並行處理的特點,一方面具有較高的運行速度,另一方面又具有軟體可重新編程的靈活性。以大量像素表達為主的低級圖像處理階段可以充分利用圖像處理操作所固有的並行性,通過使用並行硬體代替順序循環操作,對諸多圖像處理算法進行加速。

當圖像數據從攝像頭或顯示器上以數據流的形式串列通過單一的功能模組時,可以很方便地映射為硬體實現,如果所有的操作都可以使用流處理,那么整個算法便能夠以高效的流水線的方式來實現。綜上所述,FPGA在實時圖像處理中具有得天獨厚的優勢。

系統設計

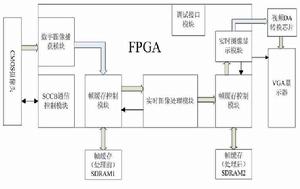

本系統由實時圖像採集模組、幀快取模組(處理前)、實時圖像處理模組、幀快取模組(處理後)、實時圖像顯示模組以及調試接口模組組成。處理流程如下:FPGA上電配置後,利用FPGA通信模組對CMOS攝像頭進行功能配置,並通過圖像捕獲模組獲取實時的數字圖像數據流,快取到幀快取模組(處理前);FPGA實時圖像處理模組讀取幀快取模組(處理前)中的圖像數據流並進行處理,處理完後存儲到幀快取模組(處理後);FPGA實時圖像顯示模組從幀快取模組(處理後)中讀取圖像數據,送到視頻DA轉換模組輸出模擬信號,並根據VGA協定送出相應的行同步和場同步信號,實現實時圖像處理後的顯示。

系統主要結構如圖所示。

實時圖像處理系統

實時圖像處理系統系統採用兩個幀快取模組,利用實時圖像處理接口將實時圖像處理功能與前端採集模組、終端顯示模組隔離開,並且每個幀快取模組只採用一塊幀快取,並沒有採用大家普遍使用的兩塊幀快取進行桌球操作來提高效率並保證圖像的完整性。本系統能夠使用一塊幀快取同時進行讀寫處理是基於實時圖像兩幅連續的圖像之間差異很小的特點,由於圖像連續高速刷新,所以人眼幾乎察覺不到不完整的畫面,實驗證明確實如此。這樣設計帶來的好處是結構更為簡單,幀快取模組的讀寫端不需要採用握手信號,圖像處理模組的處理速率也不對採集端和顯示端的速率產生依賴,減少了圖像處理模組與其他模組的禍合性,使得本系統更具有通用性的特點。