圖像採集及實時圖像採集

圖像信息是人類獲取的最重要的信息之一,圖像採集在數字圖像處理、圖像識別等領域套用十分廣泛。實時圖像的採集和處理在現代多媒體技術中占有重要的地位。日常生活中所見到的數位相機、可視電話、多媒體 IP 電話和電話會議等產品,實時圖像採集是其中的核心技術。圖像採集的速度、質量直接影響到產品的整體效果。

傳統圖像採集

目前,傳統的圖像採集是採用圖像採集卡或視霸卡將 CCD(Charge Coupled Device,電荷耦合器件)攝像機的模擬視頻信號經 A/D 後存儲,然後送計算機進行處理。這種方法使用較普遍,技術比較成熟,但是也存在一些問題。首先,CCD 攝像機的輸出已轉換為模擬的 NTSC 或 PAL 制式,並以SVideo 或混合視頻信號方式輸出,這樣採集卡的採樣點在輸出時序上很難與攝像機的象素點一一對應,造成數位化後的視頻圖像質量損失較大,圖像解析度也受到限制。其次,這種方法的硬體電路複雜、成本較高,不利於推廣和普及使用。

常用圖像感測器

常用的圖像感測器主要有 CCD 和CMOS(互補金屬氧化物半導體)兩種。目前市場上,CCD 仍占據主要地位,而隨著 CMOS 技術的發展,CMOS感測器也得到了廣泛的套用。 CCD 的優點是靈敏度高、象素小、讀取噪音低、動態範圍大,因此在固體成像領域占據主要地位。它的缺點是不能將圖像感測陣列和控制電路集成在同一晶片內,還需要外加脈衝驅動電路,信號放大,A/D 轉換等輔助電路,造成系統結構複雜,成本較高;而 CMOS 感測器則具有較小的幾何尺寸,解析度也逐漸接近 CCD 的水平,最重要的是 CMOS 感測器的製造技術與 CMOS工藝兼容,每個象素感測單元都有自己的緩衝放大器,可以非常方便的將 AD轉換器等輔助電路集成到晶片內部,其外圍電路簡單,功耗低,編程也很方便,很容易實現對幀頻、曝光時間、圖像尺寸等的控制,為視頻圖像採集提供了一種低成本高品質的解決方式。

隨機存儲器

在高速圖像採集和處理過程中,往往需要在片外使用隨機存儲器。常用的隨機存儲器主要有動態存儲器 DRAM 和靜態存儲器 SRAM 兩種。目前業界主流的SRAM 的存儲單元一般都是採用六電晶體的結構,而 DRAM 的存儲單元則一般是採用單電晶體加上一個無源的電容構成。由此,兩者的優點和缺點都比較明顯。SRAM 的訪問時間短,匯流排利用率高,靜態功耗相對較低,但是占用矽片的面積較大,容量小,價格較貴。它適用於存儲容量不大,性能要求較高的領域。而DRAM 的讀寫訪問過程比較複雜,訪問時間較長,匯流排利用率相對較低,而且由於電容器會不斷的漏電,需要周期性的去刷新,所以靜態功耗較大。其優點是存儲容量可以做的很大,價格便宜。

採樣控制

對圖像感測器的採樣控制,可以使用單片機、CPLD 或 FPGA等。在設計中,既要控制圖像感測器採樣,還有對 SRAM 的控制,圖像採集完成後,還有後續的濾波處理模組。單獨使用單片機或 CPLD 都不能獨立完成這樣的功能。可以使用單片機或 CPLD 實現控制功能,後續濾波模組使用 FPGA;也可以整體使用一個 FPGA 晶片完成所有功能,這樣做將使外圍電路設計最為簡單。

FPGA介紹

目前,隨著 VLSI 技術的發展,越來越多的算法可以用硬體來實現。同時,由於生產線的專業化,在同一環境下生成或傳輸的圖像,其受污染的噪聲類型有相似性和穩定性,這也使專用積體電路有很大的實用性。但是,由於圖像處理算法的複雜性、多樣性,一個系統只能採用一種結構,因而限制了其套用範圍。這是目前報導的圖像處理系統的共同特點。

針對圖像預處理階段運算結構的特點,FPGA 晶片是目標硬體的理想選擇之一。採用 FPGA 晶片,只需少數晶片和簡單的外圍電路,即可實現比較複雜的圖像預處理算法,而且只要改變 FPGA 晶片內部參數值就可以實現對不同尺寸、不同灰度級圖像的處理,具有一定的靈活性。目前,FPGA 已在圖像處理中得到廣泛的套用。

下圖為FPGA設計流程。

實時圖像採集

實時圖像採集 實時圖像採集系統

下面將針對利用FPGA實現的實時圖像採集系統做一簡單介紹。

實時圖像採集

實時圖像採集 在本設計中,在滿足設計要求,最主要的是圖像解析度和採樣速率的要求下,為了簡化電路結構,採用 CMOS 圖像感測器。具體選用美國 Omni Vision 公司生產的 130 萬象素的 CMOS 圖像感測器 OV9121。

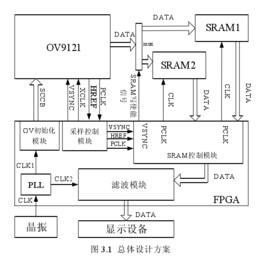

本設計的圖像採集部分,包括 OV9121 初始化模組、採樣控制模組和 SRAM控制模組。初始化模組主要是根據設計要求,設定 OV9121的工作模式;採樣控制模組負責提供 OV9121 採集圖像需要的控制信號;SRAM 控制模組主要負責快取OV9121 輸出的圖像數據,並將圖像數據送 FPGA 濾波模組處理,本模組使用了兩片相同規格的 SRAM。

OV9121 初始化模組

根據設計要求,通過改變OV9121內部暫存器的值,使OV9121工作在設定好的模式,包括工作模式、圖像的解析度、象素輸出頻率和幀頻等參數。

採樣控制模組

在實際設計中,有兩種方法可以得到需要的控制信號。一是採用鎖相環。在很多設計中,往往需要多個頻率和相位的時鐘,於是各家 FPGA 廠商便在其 FPGA 內部設計了一些時鐘管理元件,鎖相環是其中一個有代表性的電路[35]。Altera 公司的許多系列的 FPGA 內都有鎖相環,在開發環境 Quartus II 里對鎖相環的參數作出修改,可以改變初始時鐘信號的分頻係數或倍頻倍數,並可調整時鐘相位。第二種方法是自己編寫分頻程式。

SRAM 控制模組

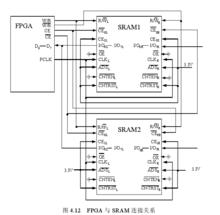

本設計採用兩片相同規格的 SRAM,在同一時間,只有一片 SRAM 接收圖像數據,也只有一片 SRAM 向 FPGA 輸出數據。SRAM 工作程式如下:首先 SRAM1 寫使能,OV9121 向 SRAM1 寫圖像數據,當向其寫完一幀圖像後,SRAM2 寫使能,OV9121 開始向 SRAM2 寫下一幀圖像,同時,SRAM1 寫禁止,讀使能,FPGA 開始讀取 SRAM1 中的圖像數據。然後,SRAM1 寫使能,開始向 SRAM1 寫圖像數據,同時 SRAM2 讀使能,從 SRAM2 讀數據,依次交替進行。這樣做,可以使 OV9121 輸出的圖像數據連續地存儲在片外存儲器中,同時,FPGA 也可以連續地從片外存儲器中讀取數據。同時,在同一時間,一個晶片只有讀或只有寫操作,可以避免對一個晶片同一地址的讀寫衝突。

實時圖像採集

實時圖像採集 套用

實時圖像採集有著廣泛的套用。在日常生活中,常用於數位相機、可視電話、多媒體 IP 電話和電話會議等產品;在工業生產中,圖像採集卡可用於材料分析、鍋爐火焰監測等;在生物醫學領域,圖像採集卡可以用於B超、CT、病理分析等;在金融領域,圖像採集卡可以用於票證處理,櫃員機自動檢測等;在航空航天領域,可以用於各種運動目標的自動制導、運動物體的經緯度測定以及夜間偵察等。