定義

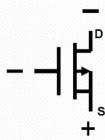

n溝道mos管符號

n溝道mos管符號雙極型電晶體把輸入端電流的微小變化放大後,在輸出端輸出一個大的電流變化。雙極型晶體管的增益就定義為輸出輸入電流之比(beta)。另一種電晶體,叫做場效應管(FET),把輸入電壓的變化轉化為輸出電流的變化。FET的增益等於它的transconductance,定義為輸出電流的變化和輸入電壓變化之比。市面上常有的一般為N溝道和P溝道,詳情參考右側圖片(N溝道耗盡型MOS管)。而P溝道常見的為低壓Mos管。

場效應管的名字也來源於它的輸入端(稱為gate)通過投影一個電場在一個絕緣層上來影響流過電晶體的電流。事實上沒有電流流過這個絕緣體,所以FET管的GATE電流非常小。最普通的FET用一薄層二氧化矽來作為GATE極下的絕緣體。這種電晶體稱為金屬氧化物半導體(MOS)電晶體,或,金屬氧化物半導體場效應管(MOSFET)。因為MOS管更小更省電,所以他們已經在很多套用場合取代了雙極型晶體管。

詳細介紹

p溝道mos管符號

p溝道mos管符號當MOS電容的GATE相對於BACKGATE正偏置時發生的情況。穿過GATEDIELECTRIC的電場加強了,有更多的電子從襯底被拉了上來。同時,空穴被排斥出表面。隨著GATE電壓的升高,會出現表面的電子比空穴多的情況。由於過剩的電子,矽表層看上去就像N型矽。摻雜極性的反轉被稱為inversion,反轉的矽層叫做channel。隨著GATE電壓的持續不斷升高,越來越多的電子在表面積累,channel變成了強反轉。Channel形成時的電壓被稱為閾值電壓Vt。當GATE和BACKGATE之間的電壓差小於閾值電壓時,不會形成channel。當電壓差超過閾值電壓時,channel就出現了。

MOS電容:(A)未偏置(VBG=0V),(B)反轉(VBG=3V),(C)積累(VBG=-3V)。正是當MOS電容的GATE相對於backgate是負電壓時的情況。電場反轉,往表面吸引空穴排斥電子。矽表層看上去更重的摻雜了,這個器件被認為是處於accumulation狀態了。

MOS電容的特性能被用來形成MOS管。Gate,電介質和backgate保持原樣。在GATE的兩邊是兩個額外的選擇性摻雜的區域。其中一個稱為source,另一個稱為drain。假設source和backgate都接地,drain接正電壓。只要GATE對BACKGATE的電壓仍舊小於閾值電壓,就不會形成channel。Drain和backgate之間的PN結反向偏置,所以只有很小的電流從drain流向backgate。如果GATE電壓超過了閾值電壓,在GATE電介質下就出現了channel。這個channel就像一薄層短接drain和source的N型矽。由電子組成的電流從source通過channel流到drain。總的來說,只有在gate對source電壓V超過閾值電壓Vt時,才會有drain電流。

在對稱的MOS管中,對source和drain的標註有一點任意性。定義上,載流子流出source,流入drain。因此Source和drain的身份就靠器件的偏置來決定了。有時電晶體上的偏置電壓是不定的,兩個引線端就會互相對換角色。這種情況下,電路設計師必須指定一個是drain另一個是source。

Source和drain不同摻雜不同幾何形狀的就是非對稱MOS管。製造非對稱電晶體有很多理由,但所有的最終結果都是一樣的。一個引線端被最佳化作為drain,另一個被最佳化作為source。如果drain和source對調,這個器件就不能正常工作了。

電晶體有N型channel所有它稱為N-channelMOS管,或NMOS。P-channelMOS(PMOS)管也存在,是一個由輕摻雜的N型BACKGATE和P型source和drain組成的PMOS管。如果這個電晶體的GATE相對於BACKGATE正向偏置,電子就被吸引到表面,空穴就被排斥出表面。矽的表面就積累,沒有channel形成。如果GATE相對於BACKGATE反向偏置,空穴被吸引到表面,channel形成了。因此PMOS管的閾值電壓是負值。由於NMOS管的閾值電壓是正的,PMOS的閾值電壓是負的,所以工程師們通常會去掉閾值電壓前面的符號。一個工程師可能說,“PMOSVt從0.6V上升到0.7V”,實際上PMOS的Vt是從-0.6V下降到-0.7V。

主要參數

1、開啟電壓VT

·開啟電壓(又稱閾值電壓):使得源極S和漏極D之間開始形成導電溝道所需的柵極電壓;

·標準的N溝道MOS管,VT約為3~6V;

·通過工藝上的改進,可以使MOS管的VT值降到2~3V。

2、直流輸入電阻RGS

·即在柵源極之間加的電壓與柵極電流之比

·這一特性有時以流過柵極的柵流表示

·MOS管的RGS可以很容易地超過1010Ω。

3、漏源擊穿電壓BVDS

·在VGS=0(增強型)的條件下,在增加漏源電壓過程中使ID開始劇增時的VDS稱為漏源擊穿電壓BVDS

·ID劇增的原因有下列兩個方面:

(1)漏極附近耗盡層的雪崩擊穿

(2)漏源極間的穿通擊穿

·有些MOS管中,其溝道長度較短,不斷增加VDS會使漏區的耗盡層一直擴展到源區,使溝道長度為零,即產生漏源間的穿通,穿通後,源區中的多數載流子,將直接受耗盡層電場的吸引,到達漏區,產生大的ID

4、柵源擊穿電壓BVGS

·在增加柵源電壓過程中,使柵極電流IG由零開始劇增時的VGS,稱為柵源擊穿電壓BVGS。

5、低頻跨導gm

·在VDS為某一固定數值的條件下,漏極電流的微變數和引起這個變化的柵源電壓微變數之比稱為跨導

·gm反映了柵源電壓對漏極電流的控制能力

·是表征MOS管放大能力的一個重要參數

·一般在十分之幾至幾mA/V的範圍內

6、導通電阻RON

·導通電阻RON說明了VDS對ID的影響,是漏極特性某一點切線的斜率的倒數

·在飽和區,ID幾乎不隨VDS改變,RON的數值很大,一般在幾十千歐到幾百千歐之間

·由於在數字電路中,MOS管導通時經常工作在VDS=0的狀態下,所以這時的導通電阻RON可用原點的RON來近似

·對一般的MOS管而言,RON的數值在幾百歐以內

7.極間電容

·三個電極之間都存在著極間電容:柵源電容CGS、柵漏電容CGD和漏源電容CDS

·CGS和CGD約為1~3pF

·CDS約在0.1~1pF之間

8.低頻噪聲係數NF

·噪聲是由管子內部載流子運動的不規則性所引起的

·由於它的存在,就使一個放大器即便在沒有信號輸人時,在輸出端也出現不規則的電壓或電流變化

·噪聲性能的大小通常用噪聲係數NF來表示,它的單位為分貝(dB)

·這個數值越小,代表管子所產生的噪聲越小

·低頻噪聲係數是在低頻範圍內測出的噪聲係數

·場效應管的噪聲係數約為幾個分貝,它比雙極性三極體的要小

發熱分析

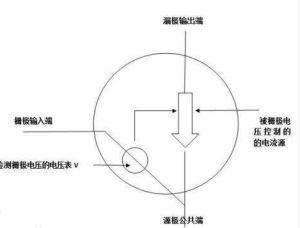

MOS管的工作原理

MOS管的工作原理做電源設計,或者做驅動方面的電路,難免要用到MOS管。MOS管有很多種類,也有很多作用。做電源或者驅動的使用,當然就是用它的開關作用。

無論N型或者P型MOS管,其工作原理本質是一樣的。MOS管是由加在輸入端柵極的電壓來控制輸出端漏極的電流。MOS管是壓控器件它通過加在柵極上的電壓控制器件的特性,不會發生像三極體做開關時的因基極電流引起的電荷存儲效應,因此在開關套用中,MOS管的開關速度應該比三極體快。

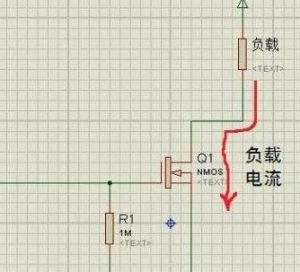

我們在開關電源中常用MOS管的漏極開路電路,如圖2漏極原封不動地接負載,叫開路漏極,開路漏極電路中不管負載接多高的電壓,都能夠接通和關斷負載電流。是理想的模擬開關器件。這就是MOS管做開關器件的原理。當然MOS管做開關使用的電路形式比較多了。

在開關電源套用方面,這種套用需要MOS管定期導通和關斷。比如,DC-DC電源中常用的基本降壓轉換器依賴兩個MOS管來執行開關功能,這些開關交替在電感里存儲能量,然後把能量釋放給負載。我們常選擇數百kHz乃至1MHz以上的頻率,因為頻率越高,磁性元件可以更小更輕。在正常工作期間,MOS管只相當於一個導體。因此,我們電路或者電源設計人員最關心的是MOS的最小傳導損耗。

NMOS管的開路漏極電路

NMOS管的開路漏極電路我們經常看MOS管的PDF參數,MOS管制造商採用RDS(ON)參數來定義導通阻抗,對開關套用來說,RDS(ON)也是最重要的器件特性。數據手冊定義RDS(ON)與柵極(或驅動)電壓VGS以及流經開關的電流有關,但對於充分的柵極驅動,RDS(ON)是一個相對靜態參數。一直處於導通的MOS管很容易發熱。另外,慢慢升高的結溫也會導致RDS(ON)的增加。MOS管數據手冊規定了熱阻抗參數,其定義為MOS管封裝的半導體結散熱能力。RθJC的最簡單的定義是結到管殼的熱阻抗。其發熱情況有:

1.電路設計的問題,就是讓MOS管工作線上性的工作狀態,而不是在開關狀態。這也是導致MOS管發熱的一個原因。如果N-MOS做開關,G級電壓要比電源高几V,才能完全導通,P-MOS則相反。沒有完全打開而壓降過大造成功率消耗,等效直流阻抗比較大,壓降增大,所以U*I也增大,損耗就意味著發熱。這是設計電路的最忌諱的錯誤。

2.頻率太高,主要是有時過分追求體積,導致頻率提高,MOS管上的損耗增大了,所以發熱也加大了。

3.沒有做好足夠的散熱設計,電流太高,MOS管標稱的電流值,一般需要良好的散熱才能達到。所以ID小於最大電流,也可能發熱嚴重,需要足夠的輔助散熱片。

4.MOS管的選型有誤,對功率判斷有誤,MOS管內阻沒有充分考慮,導致開關阻抗增大。

常見型號

型號電壓/電流封裝

2N700060V,0.115ATO-92

2N700260V,0.2ASOT-23

IRF510A100V,5.6ATO-220

IRF520A100V,9.2ATO-220

IRF530A100V,14ATO-220

IRF540A100V,28ATO-220

IRF610A200V,3.3ATO-220

IRF620A200V,5ATO-220

IRF630A200V,9ATO-220

IRF634A250V,8.1ATO-220

IRF640A200V,18ATO-220

IRF644A250V,14ATO-220

IRF650A200V,28ATO-220

IRF654A250V,21ATO-220

IRF720A400V,3.3ATO-220

IRF730A400V,5.5ATO-220

IRF740A400V,10ATO-220

IRF750A400V,15ATO-220

IRF820A500V,2.5ATO-220

IRF830A500V,4.5ATO-220

IRF840A500V,8ATO-220

IRFP150A100V,43ATO-3P

IRFP250A200V,32ATO-3P

IRFP450A500V,14ATO-3P

IRFR024A60V,15AD-PAK

IRFR120A100V,8.4AD-PAK

IRFR214A250V,2.2AD-PAK

IRFR220A200V,4.6AD-PAK

IRFR224A250V,3.8AD-PAK

IRFR310A400V,1.7AD-PAK

正確選擇的步驟

正確選擇MOS管是很重要的一個環節,MOS管選擇不好有可能影響到整個電路的效率和成本,了解不同的MOS管部件的細微差別及不同開關電路中的應力能夠幫助工程師避免諸多問題,下面我們來學習下MOS管的正確的選擇方法。

第一步:選用N溝道還是P溝道

為設計選擇正確器件的第一步是決定採用N溝道還是P溝道MOS管。在典型的功率套用中,當一個MOS管接地,而負載連線到幹線電壓上時,該MOS管就構成了低壓側開關。在低壓側開關中,應採用N溝道MOS管,這是出於對關閉或導通器件所需電壓的考慮。當MOS管連線到匯流排及負載接地時,就要用高壓側開關。通常會在這個拓撲中採用P溝道MOS管,這也是出於對電壓驅動的考慮。

要選擇適合套用的器件,必須確定驅動器件所需的電壓,以及在設計中最簡易執行的方法。下一步是確定所需的額定電壓,或者器件所能承受的最大電壓。額定電壓越大,器件的成本就越高。根據實踐經驗,額定電壓應當大於幹線電壓或匯流排電壓。這樣才能提供足夠的保護,使MOS管不會失效。就選擇MOS管而言,必須確定漏極至源極間可能承受的最大電壓,即最大VDS。知道MOS管能承受的最大電壓會隨溫度而變化這點十分重要。設計人員必須在整個工作溫度範圍內測試電壓的變化範圍。額定電壓必須有足夠的餘量覆蓋這個變化範圍,確保電路不會失效。設計工程師需要考慮的其他安全因素包括由開關電子設備(如電機或變壓器)誘發的電壓瞬變。不同套用的額定電壓也有所不同;通常,攜帶型設備為20V、FPGA電源為20~30V、85~220VAC套用為450~600V。

第二步:確定額定電流

第二步是選擇MOS管的額定電流。視電路結構而定,該額定電流應是負載在所有情況下能夠承受的最大電流。與電壓的情況相似,設計人員必須確保所選的MOS管能承受這個額定電流,即使在系統產生尖峰電流時。兩個考慮的電流情況是連續模式和脈衝尖峰。在連續導通模式下,MOS管處於穩態,此時電流連續通過器件。脈衝尖峰是指有大量電涌(或尖峰電流)流過器件。一旦確定了這些條件下的最大電流,只需直接選擇能承受這個最大電流的器件便可。

選好額定電流後,還必須計算導通損耗。在實際情況下,MOS管並不是理想的器件,因為在導電過程中會有電能損耗,這稱之為導通損耗。MOS管在“導通”時就像一個可變電阻,由器件的RDS(ON)所確定,並隨溫度而顯著變化。器件的功率耗損可由Iload2×RDS(ON)計算,由於導通電阻隨溫度變化,因此功率耗損也會隨之按比例變化。對MOS管施加的電壓VGS越高,RDS(ON)就會越小;反之RDS(ON)就會越高。對系統設計人員來說,這就是取決於系統電壓而需要折中權衡的地方。對攜帶型設計來說,採用較低的電壓比較容易(較為普遍),而對於工業設計,可採用較高的電壓。注意RDS(ON)電阻會隨著電流輕微上升。關於RDS(ON)電阻的各種電氣參數變化可在製造商提供的技術資料表中查到。

技術對器件的特性有著重大影響,因為有些技術在提高最大VDS時往往會使RDS(ON)增大。對於這樣的技術,如果打算降低VDS和RDS(ON),那么就得增加晶片尺寸,從而增加與之配套的封裝尺寸及相關的開發成本。業界現有好幾種試圖控制晶片尺寸增加的技術,其中最主要的是溝道和電荷平衡技術。

在溝道技術中,晶片中嵌入了一個深溝,通常是為低電壓預留的,用於降低導通電阻RDS(ON)。為了減少最大VDS對RDS(ON)的影響,開發過程中採用了外延生長柱/蝕刻柱工藝。例如,飛兆半導體開發了稱為SupeRFET的技術,針對RDS(ON)的降低而增加了額外的製造步驟。這種對RDS(ON)的關注十分重要,因為當標準MOSFET的擊穿電壓升高時,RDS(ON)會隨之呈指數級增加,並且導致晶片尺寸增大。SuperFET工藝將RDS(ON)與晶片尺寸間的指數關係變成了線性關係。這樣,SuperFET器件便可在小晶片尺寸,甚至在擊穿電壓達到600V的情況下,實現理想的低RDS(ON)。結果是晶片尺寸可減小達35%。而對於最終用戶來說,這意味著封裝尺寸的大幅減小。

第三步:確定熱要求

選擇MOS管的下一步是計算系統的散熱要求。設計人員必須考慮兩種不同的情況,即最壞情況和真實情況。建議採用針對最壞情況的計算結果,因為這個結果提供更大的安全餘量,能確保系統不會失效。在MOS管的資料表上還有一些需要注意的測量數據;比如封裝器件的半導體結與環境之間的熱阻,以及最大的結溫。

器件的結溫等於最大環境溫度加上熱阻與功率耗散的乘積(結溫=最大環境溫度+[熱阻×功率耗散])。根據這個方程可解出系統的最大功率耗散,即按定義相等於I2×RDS(ON)。由於設計人員已確定將要通過器件的最大電流,因此可以計算出不同溫度下的RDS(ON)。值得注意的是,在處理簡單熱模型時,設計人員還必須考慮半導體結/器件外殼及外殼/環境的熱容量;即要求印刷電路板和封裝不會立即升溫。

雪崩擊穿是指半導體器件上的反向電壓超過最大值,並形成強電場使器件內電流增加。該電流將耗散功率,使器件的溫度升高,而且有可能損壞器件。半導體公司都會對器件進行雪崩測試,計算其雪崩電壓,或對器件的穩健性進行測試。計算額定雪崩電壓有兩種方法;一是統計法,另一是熱計算。而熱計算因為較為實用而得到廣泛採用。除計算外,技術對雪崩效應也有很大影響。例如,晶片尺寸的增加會提高抗雪崩能力,最終提高器件的穩健性。對最終用戶而言,這意味著要在系統中採用更大的封裝件。

第四步:決定開關性能

選擇MOS管的最後一步是決定MOS管的開關性能。影響開關性能的參數有很多,但最重要的是柵極/漏極、柵極/源極及漏極/源極電容。這些電容會在器件中產生開關損耗,因為在每次開關時都要對它們充電。MOS管的開關速度因此被降低,器件效率也下降。為計算開關過程中器件的總損耗,設計人員必須計算開通過程中的損耗(Eon)和關閉過程中的損耗(Eoff)。MOSFET開關的總功率可用如下方程表達:Psw=(Eon+Eoff)×開關頻率。而柵極電荷(Qgd)對開關性能的影響最大。