基本含義

LDO低壓差線性穩壓器

LDO低壓差線性穩壓器LDO 是一種線性穩壓器,使用在其線性區域內運行的電晶體或場效應管(FET),從套用的輸入電壓中減去超額的電壓,產生經過調節的輸出電壓。所謂壓降電壓,是指穩壓器將輸出電壓維持在其額定值上下 100mV 之內所需的輸入電壓與輸出電壓差額的最小值。正輸出電壓的LDO(低壓降)穩壓器通常使用功率電晶體(也稱為傳遞設備)作為 PNP。這種電晶體允許飽和,所以穩壓器可以有一個非常低的壓降電壓,通常為 200mV 左右;與之相比,使用 NPN 複合電源電晶體的傳統線性穩壓器的壓降為 2V 左右。負輸出 LDO 使用 NPN 作為它的傳遞設備,其運行模式與正輸出 LDO 的 PNP設備類似。

更新的發展使用 MOS 功率電晶體,它能夠提供最低的壓降電壓。使用 功率MOS,通過穩壓器的唯一電壓壓降是電源設備負載電流的 ON 電阻造成的。如果負載較小,這種方式產生的壓降只有幾十毫伏。

DC-DC的意思是直流變(到)直流(不同直流電源值的轉換),只要符合這個定義都可以叫DC-DC轉換器,包括LDO。但是一般的說法是把直流變(到)直流由開關方式實現的器件叫DC-DC。

LDO是低壓降的意思,這有一段說明:低壓降(LDO)線性穩壓器的成本低,噪音低,靜態電流小,這些是它的突出優點。它需要的外接元件也很少,通常只需要一兩個旁路電容。新的LDO線性穩壓器可達到以下指標:輸出噪聲30μV,PSRR為60dB,靜態電流6μA(TI的TPS78001達到Iq=0.5uA),電壓降只有100mV(TI量產了號稱0.1mV的LDO)。 LDO線性穩壓器的性能之所以能夠達到這個水平,主要原因在於其中的調整管是用P溝道MOSFET,而普通的線性穩壓器是使用PNP電晶體。P溝道MOSFET是電壓驅動的,不需要電流,所以大大降低了器件本身消耗的電流;另一方面,採用PNP電晶體的電路中,為了防止PNP電晶體進入飽和狀態而降低輸出能力, 輸入和輸出之間的電壓降不可以太低;而P溝道MOSFET上的電壓降大致等於輸出電流與導通電阻的乘積。由於MOSFET的導通電阻很小,因而它上面的電壓降非常低。

如果輸入電壓和輸出電壓很接近,最好是選用LDO穩壓器,可達到很高的效率。所以,在把鋰離子電池電壓轉換為3V輸出電壓的套用中大多選用LDO穩壓器。雖說電池的能量最後有百分之十是沒有使用,LDO穩壓器仍然能夠保證電池的工作時間較長,同時噪音較低。

如果輸入電壓和輸出電壓不是很接近,就要考慮用開關型的DCDC了,因為從上面的原理可以知道,LDO的輸入電流基本上是等於輸出電流的,如果壓降太大,耗在LDO上能量太大,效率不高。

DC-DC轉換器包括升壓、降壓、升/降壓和反相等電路。DC-DC轉換器的優點是效率高、可以輸出大電流、靜態電流小。隨著集成度的提高,許多新型DC-DC轉換器僅需要幾隻外接電感器和濾波電容器。但是,這類電源控制器的輸出脈動和開關噪音較大、成本相對較高。

近幾年來,隨著半導體技術的發展,表面貼裝的電感器、電容器、以及高集成度的電源控制晶片的成本不斷降低,體積越來越小。由於出現了導通電阻很小的MOSFET可以輸出很大功率,因而不需要外部的大功率FET。例如對於3V的輸入電壓,利用晶片上的NFET可以得到5V/2A的輸出。其次,對於中小功率的套用,可以使用成本低小型封裝。另外,如果開關頻率提高到1MHz,還能夠降低成本、可以使用尺寸較小的電感器和電容器。有些新器件還增加許多新功能,如軟啟動、限流、PFM或者PWM方式選擇等。

總的來說,升壓是一定要選DCDC的,降壓,是選擇DCDC還是LDO,要在成本,效率,噪聲和性能上比較。

區別

LDO是一種微功耗的低壓差線性穩壓器,它通常具有極低的自有噪聲和較高的電源抑制比PSRR(Power Supply Rejection Ratio)。

LDO是新一代的積體電路穩壓器,它與三端穩壓器最大的不同點在於,LDO是一個自耗很低的微型片上系統(SoC)。它可用於電流主通道控制,晶片上集成了具有極低線上導通電阻的MOSFET,肖特基二極體、取樣電阻和分壓電阻等硬體電路,並具有過流保護、過溫保護、精密基準源、差分放大器、延遲器等功能。PG是新一代LDO,具各輸出狀態自檢、延遲安全供電功能,也可稱之為Power Good,即“電源好或電源穩定”。

結構

LDO低壓差線性穩壓器的結構主要包括啟動電路、恆流源偏置單元、使能電路、調整元件、基準源、誤差放大器、反饋電阻網路和保護電路等。基本工作原理是這樣的:系統加電,如果使能腳處於高電平時,電路開始啟動,恆流源電路給整個電路提供偏置,基準源電壓快速建立,輸出隨著輸入不斷上升,當輸出即將達到規定值時,由反饋網路得到的輸出反饋電壓也接近於基準電壓值,此時誤差放大器將輸出反饋電壓和基準電壓之間的誤差小信號進行放大,再經調整管放大到輸出,從而形成負反饋,保證了輸出電壓穩定在規定值上,同理如果輸入電壓變化或輸出電流變化,這個閉環迴路將使輸出電壓保持不變,即:Vout=(R1+R2)/R2 ×Vref

實際的低壓差線性穩壓器還具有如負載短路保護、過壓關斷、過熱關斷、反接保護等其它的功能。

工作原理

LDO低壓差線性穩壓器

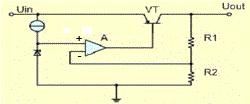

LDO低壓差線性穩壓器如右圖所示,該電路由串聯調整管VT、取樣電阻R1和R2、比較放大器A組成。

取樣電壓加在放大器A的反相輸入端,與加在同相輸入端的基準電壓Uref相比較,兩者的差值經放大器A放大後,控制串聯調整管的壓降,從而穩定輸出電壓。當輸出電壓Uout降低時,基準電壓與取樣電壓的差值增加,比較放大器輸出的驅動電流增加,串聯調整管壓降減小,從而使輸出電壓升高。相反,若輸出電壓Uout超過所需要的設定值,比較放大器輸出的前驅動電流減小,從而使輸出電壓降低。供電過程中,輸出電壓校正連續進行,調整時間只受比較放大器和輸出電晶體迴路反應速度的限制。

應當說明,實際的線性穩壓器還應當具有許多其它的功能,比如負載短路保護、過壓關斷、過熱關斷、反接保護等,而且串聯調整管也可以採用MOSFET。

生產廠家

TOREX,SII,ROHM,RICOH,Diodes,Prisemi,Ame,TI,NS,Maxim,LTC,Intersil,Fairchild,Micrel,Natlinear,MPS,AATI,ACE,ADI,ST等;

四大要素

壓差Dropout、噪音Noise、電源抑制比(PSRR)、靜態電流Iq,這是LDO的四大關鍵數據。

產品設計師按產品負載對電性能的要求結合四大要素來選擇LDO。

在手機上用的LDO要求儘可能小的噪音(紋波),在沒有RF的攜帶型產品需求靜態電流小的LDO。

工作條件

Vin >= Vdrop + Vout。

且一般需要兩個外接電容:Cin、Cout,一般採用鉭電容或MLCC。

注意:LDO是穩壓器。

套用

LDO的套用非常簡單,很多LDO僅需在輸入端及輸出端各接一顆電容即可穩定工作。在LDO的套用中需要考慮壓差、靜態電流、PSRR等重要參數。在以電池作為電源的系統中,應當選擇壓差儘量低的LDO,這樣可以使電池更長時間為系統供電,比如NCP600,NCP629等等。

靜態電流Iq是Iquiescent的縮寫,指晶片自身所消耗的電流。在一些低功耗套用中,應當儘量選擇Iq小的LDO。一些工程師在設計低功耗系統時,僅考慮MCU本身消耗的電流,而忽略電源晶片上所消耗的電流,使整個系統的待機功耗不能達標,曾經見過有的工程師在低功耗系統中選用78L05為MCU提供電源,查閱數據手冊可以得知78L05靜態電流為1mA,不適合低功耗套用,應該選擇NCP583等等。

在射頻、音頻、ADC轉換等套用系統中,PSRR(電源紋波抑制比)是一個很重要的參數,其體現了LDO的抗噪能力,PSRR值越高LDO輸出紋波越低。下面列出了LDO的一些重要特性及套用方向。

不同電壓輸出級別的套用領域

| 電壓輸出級別 | 套用領域 |

| 1.25V | ARM9,FPGA、DSP等 |

| 1.8V | SDRAM,DDR RAM等 |

| 2.5V | MCU,DDR RAM等 |

| 3.0V | MCU,Nor Flash,Nand Flash,其他各種接口器件等 |

300 mA的LDO穩壓器降壓穩壓器電路

300 mA的LDO穩壓器降壓穩壓器電路LDO特性及套用方向

| 特性 | 套用方向 |

| 超低紋波,高精度 | 數據採集 |

| 低壓差 | 電池供電 |

| 低靜態電流 | 低功耗場合,如手持儀表 |

| 電壓監控 | 嵌入系統電源管理 |

| 復位控制 | 工業控制 |

| 多通道輸出 | 需要多路供電的嵌入式系統 |

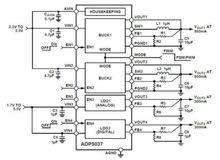

實例

降壓穩壓器的高開關頻率允許使用纖巧多層外部元件,並最大限度地減少了電路板空間。當MODE引腳設定為高,降壓穩壓器工作在強制PWM模式。當MODE引腳置低,降壓穩壓器工作在PWM模式下,當負載是圍繞面值。當負載電流低於預定的閾值時,穩壓器工作在省電模式(PSM提高輕負載效率)。