特性:

串列外圍晶片SPI兼容

支持SPI模式0(0,0)和模式3(1,1)

20MHZ時鐘頻率

位元組模式和256位元組頁寫模式編程

扇區特性:

2扇區,每扇區32K位元組(512K)

4扇區,每扇區32K位元組(1M)

每扇區128頁

產品認證模式

低壓工作

(VCC=2.7V 到3.6V)

扇區防寫

防寫( /W/P )針是寫禁止指令,保護硬體和軟體

自計時編程周期(典型值 60us/Byte)

自計時扇擦除周期(典型值1秒)

狀態暫存器單周期編程(擦除和編程)

高可靠性:可寫10000次

描述:

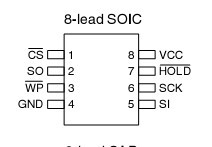

AT25F512/1024按65,536/131,072個字組織提供524288/1048576位元組的串列可程式FLASH模組,進行最佳化操作後在低功耗或低電壓的工業或商業場合具有明顯優勢。AT25F512/1024採用節省空間的8引腳SOIC封裝形式。

AT25F512/1024由 引腳使能,由3線串列接口串列輸入(SI )、串列輸出(SO)、串列時鐘(SCK)通訊。所有的寫入周期都是自計時的。塊防寫通過編程狀態暫存器實現,包括1/4、1/2/、1M/或全存儲組(512K),提供獨立的寫使能和寫禁止進行附加數據保護。由 引腳增加對硬體數據的保護,防止不恰當的寫入狀態暫存器。/H/O/L/D引腳用來暫停串列通訊而不重新設定串列序列。

片選 SI 串列輸入 SO串列輸出 GND 地 VCC電源 串列輸入懸掛 防寫

工作電壓: -40°C--+85°C

存儲溫度:-65°C--+150°C

引腳對地電壓: -1.0V---7.0V

最大工作電壓:6.25V

直流輸出電流:5.0MA

注意:超過工作範圍將導致器件永久損壞。這只是其中之一,任何超過規定所述工作條件的操作都將引起器件的損壞。暴露於工作極限時間過長會減小可靠性。

串列接口描述:主機:產生串列時鐘

從方式:因為串列時鐘總是讀入,所以AT25F512/1024工作於從方式。

MSB:首先傳送和接收

串列OP碼:片選端 變低後,首先接收一個位元組數據,定義接下來的操作。

無效串列OP碼:當收到一個無效的串列OP碼,數據不會移入AT25F512/1024,SO輸出保持高阻態,直到 再次降低,這將重新初始化串列通訊。

晶片選擇:AT25F512/1024在 低電平時被選擇,當晶片沒有被選擇時,SI引腳不會讀入數據,SO保持高阻態。

/H/O/L/D:/H/O/L/D和/C/S一起選擇AT25F512/1024。當串列傳輸正在進行時,/H/O/L/D可以暫停數據傳輸而主機不用重新設定串列通訊。要暫停串列傳輸,/H/O/L/D必須在CLK低電平時變低,要恢復傳輸,/H/O/L/D必須在CLK為低是變高

(/H/O/L/D變低時CLK依然觸發)SO為高阻態時輸入引腳SI被忽略。

防寫:AT25F512/1024有一個寫鎖定特性,通過防寫引腳WP被激活。被鎖定的部分為唯讀特性。防寫引腳在高電平是是正常的讀寫特性,/W/P變低電平且WPEN置一時,所有對狀態暫存器的寫操作被禁止。/W/P在/C/S為低電平時變低,將中斷一個寫入狀態暫存器的操作。WPEN為0時,/W/P被禁止,所以把AT25F512/1024裝進系統時可以把/W/P引腳和地相連。/W/P的所有功能在WPEN為高時被使能。

功能描述:AT25F512/1024可以和6800個微處理器進行SPI同步串列通訊。

AT25F512/1024是8位暫存器結構。表1給出了指令暫存器的功能和代碼。所有指令(地址、數據)都是高位在前,由高到低傳輸方式。以下是編程(擦除)的格式

下述命令:編程PROGRAM、塊擦除SECTOR ERASE、晶片擦除CHIP ERASE、寫暫存器WRSR

操作格式

| Wren | 0000 X110 | 設定寫使能 |

| WRDI | 0000 X100 | 重新設定寫使能 |

| RDSR | 0000 X101 | 讀狀態暫存器 |

| WRSR | 0000 X001 | 寫狀態暫存器 |

| READ | 0000 X011 | 從存儲區讀數 |

| PROGRAM | 0000 X010 | 編程存儲區 |

| SECTOR ERASE | 0101 X010 | 擦除存儲區一個塊 |

| CHIP ERASE | 0110 X010 | 擦除所有存儲區 |

| RDID | 0001 X101 | 讀生產商和產品ID號 |

寫禁止 (WRDI):為了保護器件不被不當的寫操作破壞,WRDI禁止所有的寫操作,改指令與Wp無關。

讀狀態暫存器 (RDSR):RDSR提供與狀態暫存器的入口,設備讀/忙狀態和寫使能由RDSR決定。簡單的說:塊保護位決定了被保護的程度。這些位由WRDI指令決定。在內部寫周期,除WRDI外所有的命令都被忽略。

狀態暫存器格式:

| BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

| WPEN | X | X | X | BP1 | BP2 | WEN |

| BIT0 | 為0時不是設備準備好了,為1時正在進行寫操作。 | |

| BIT1 | WEN | 為0時不是沒有寫使能,為1時寫使能。 |

| BIT2 | 見表4 | |

| BIT3 | 見表4 | |

| BIY4--BIT6 在設備不處於寫周期是為0 | ||

| BIT7 | 見表5 | |

| BIT0--BIT7 在寫周期時全為1 |

寫狀態暫存器((WRSR)寫狀態暫存器使用戶能選擇AT25F1024的保護級別。AT25F1024分為4個保護級別,最大部份(1/4)、最大1/2或者所有的存儲區都禁止寫。AT25F512分為2個部分,所有的存儲區都被保護。任何被保護的區域相應的只能讀。鎖定區域和對應的狀態暫存器見表4.

3個位:BP0, BP1, and WPEN是不可變區域,和普通存儲區有同樣的功能和特性。

表 4. 塊防寫位

| 級別 | 狀態暫存器位 | AT25F512 | AT25F1024 | |||

| BP1 | BP0 | 陣列地址鎖定 | 鎖定扇區 | 陣列地址鎖定 | 鎖定扇區 | |

| 0 | 0 | 0 | 無 | 無 | 無 | 無 |

| 1(1/4) | 0 | 1 | 018000 - 01FFFF | 扇區4 | ||

| 2(1/2) | 1 | 0 | 010000 - 01FFFF | 扇區3,4 | ||

| 3(全部) | 1 | 1 | 000000 - 00FFFF | 所有扇區(1 - 2) | 000000 - 01FFFF | 所有扇區1-4 |

注意:當WPEN為防寫時,只要WP為低電平,它就不能變回0.

表5:WPEN操作:

| WPEN | WEN | 保護塊 | 未保護塊 | 狀態暫存器 | |

| 0 | X | 0 | 保護 | 保護 | 保護 |

| 0 | X | 1 | 保護 | 寫使能 | 寫使能 |

| 1 | 低 | 0 | 保護 | 保護 | 保護 |

| 1 | 低 | 1 | 保護 | 寫使能 | 保護 |

| X | 高 | 0 | 保護 | 保護 | 保護 |

| X | 高 | 1 | 保護 | 寫使能 | 寫使能 |

編程(PROGRAM):對AT25F512/1024編程要操作兩個獨立的指令。首先:設備必須通過WREN寫使能,然後進行編程指令。同時,存儲區的地址必須被定位在塊防寫區外。在寫周期里,除了RDSR外,所有的指令都被忽略。編程指令需要一下次序:首先/C/S被拉低通過SI傳送編程指令,接著是被編程的地址和數據,編程指令在/C/S拉高后開始。/C/s必須在D0(LSB)數據位的CLK低電平時立即由低變高。

讀/忙狀態可以由RDSR指令決定。Bit 0 = 1時,編程周期持續,Bit 0 = 1結束。編程期間只有DRSR有效。

一個單獨的編程指令給一個未防寫的1-256位元組(頁)編程。開始位元組可以在頁的任何地方,。當等到頁的末尾時,地址會回卷到本頁的開始。如果數據少於一整頁,本頁的其他位元組不會改變。如果多餘256位元組,地址計數器會回卷到本頁開始。前面的數據會被更換。同樣的位元組不能在未進行塊擦除前被更換。AT25F512/1024在編程周期結束後返回到寫禁止狀態。注意:如果裝置沒有被寫使能,(WREN)設備將忽略寫指令並返回待機狀態,/C/S為高時需要重新設低以初始化串列通訊。

表6 地址鍵

| 地址 | AT25F512 | AT25F1024 |

| AN | A15- A0 | A16 - A0 |

| 0 | A16 | - |

| 位無關 | A23 - A17 | A23 - A17 |

塊擦除 (SECTOR ERASE):對一個位元組重新編程前,必須將包含這個位元組的塊擦除。對AT25F512/1024擦除可以使用兩個獨立的指令。首先:通過WREN指令使寫使能,然後進行快擦除指令SECTOR ERASE。

| 扇區地址 | AT25F512 | AT25F1024 |

| 000000 to 007FFF | 塊 1 | 塊 1 |

| 008000 to 00FFFF | 塊 2 | 塊 2 |

| 010000 to 017FFF | N/A | 塊 3 |

| 018000 to 01FFFF | N/A | 塊 4 |

晶片擦除 (CHIP ERASE):作為快擦除的替換,晶片擦除可以擦除任何一個沒有鎖定的存儲區。首先要由WREN使寫使能,然後可以執行晶片擦除指令。它是內部控制的,自動同步到結束。典型的晶片存儲周期為3.5秒。除了RDSR,此時所有的命令被忽略,晶片擦除結束後AT25F512/1024自動返回寫禁止狀態。