Schottky二極體保證了BJT不進入過飽和狀態

Schottky二極體保證了BJT不進入過飽和狀態(1)基本概念:

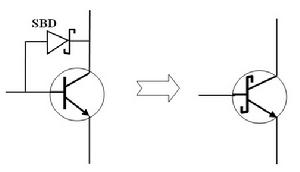

SCT是在n-p-n電晶體的基極與集電極之間加接有一個SBD(Schottky 勢壘二極體)的BJT(見圖示)。其優點就是使得當BJT進入飽和狀態時,其集電結電壓Vbc被箝位在SBD的導通電壓(≈0.45V)上,從而避免了BJT進入深飽和狀態,減小了超量少子存儲電荷,則可減短BJT開關過程中的存儲時間(可縮短1個數量級),導致積體電路中的信號傳輸延遲時間大大減短(延遲時間可降低到2~4ns,延遲時間與功耗的乘積大約可降低一半),結果可提高積體電路的工作速度。SCT是製作高速數字積體電路的基本器件。

(2)SCT工作的特點:對於TTL中的n-p-n-BJT,採用SCT來代替,可較好地解決開、關速度對基極電流Ib大小要求上的矛盾(快速導通要求Ib大,即要基區電荷存儲多;而快速關斷要求Ib小,即要電荷存儲少)。

1)當Vbc<0(即SCT處在正向放大態或截止態)時,SBD反偏而可以忽略其影響。

2)當Vbc>0(即SCT處在反向放大態或飽和態)時:①如果Vbc低於SBD的導通電壓,則SBD不對電晶體的Ib起分流作用;②如果Vbc高於SBD的導通電壓,則SBD將對電晶體的Ib起分流作用,並且Vbc被箝位在0.45V,則阻止了BJT進入深飽和,可提高其工作速度。

在傳輸延遲時間與功耗的乘積一定時,採用SCT可設計兩種TTL電路:a)保持功耗不變,使傳輸延遲時間減短——高速TTL(STTL);b)保持傳輸延遲時間不變,使功耗降低——中速低功耗TTL(LSTTL)。

(4)SCT的缺點:① SBD的接入使得BJT的飽和壓降升高;② 使得BJT的反向漏電流增大;③ 使工藝要求提高(對於Si的表面處理和金屬化工藝要求很高,而且重複性和可靠 性較差)等。