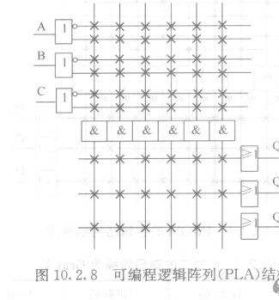

原理

PLA如此的邏輯閘布局能用來規劃大量的邏輯函式,這些邏輯函式必須先以積項(有時是多個積項)的原始形式進行齊一化。在PLA的套用中,有一種是用來控制資料路徑,在指令集內事先定義好邏輯狀態,並用此來產生下一個邏輯狀態(透過條件分支)。

舉例來說,如果目前機器(指整個邏輯系統)處於二號狀態,如果接下來的執行指令中含有一個立即值(偵測到立即值的欄位)時,機器就從第二狀態轉成四號狀態,並且也可以進一步定義進入第四狀態後的接續動作。因此PLA等於扮演(晶片)系統內含的邏輯狀態圖(statediagram)角色。