發展歷程

隨著計算機工業的發展,作為計算機最常用輸入設備的鍵盤也日新月異。1981年IBM推出了IBM PC/XT鍵盤及其接口標準。該標準定義了83鍵,採用5腳DIN連線器和簡單的串列協定。實際上,第一套鍵盤掃描碼集並沒有主機到鍵盤的命令。為此,1984年IBM推出了IBM AT鍵盤接口標準。該標準定義了84~101鍵,採用5腳DIN連線器和雙向串列通訊協定,此協定依照第二套鍵盤掃描碼集設有8個主機到鍵盤的命令。到了1987年,IBM又推出了PS/2鍵盤接口標準。該標準仍舊定義了84~101鍵,但是採用6腳mini-DIN連線器,該連線器在封裝上更小巧,仍然用雙向串列通訊協定並且提供有可選擇的第三套鍵盤掃描碼集,同時支持17個主機到鍵盤的命令。市面上的鍵盤都和PS/2及AT鍵盤兼容,只是功能不同而已。

接口特性

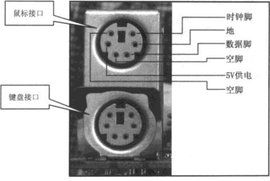

物理連線

一般,具有五腳連線器的鍵盤稱之為AT鍵盤,而具有六腳mini-DIN連線器的鍵盤則稱之為PS/2鍵盤。其實這兩種連線器都只有四個腳有意義。它們分別是Clock(時鐘腳)、Data(數據腳)、+5V(電源腳)和Ground(電源地)。在PS/2鍵盤與PC機的物理連線上只要保證這四根線一一對應就可以了。PS/2鍵盤靠PC的PS/2連線埠提供+5V電源,另外兩個腳Clock(時鐘腳)和Data(數據腳)都是集電極開路的,所以必須接大阻值的上拉電阻。它們平時保持高電平,有輸出時才被拉到低電平,之後自動上浮到高電平。比較常用的連線器如圖1所示。

電氣特性

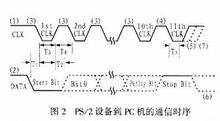

PS/2通訊協定是一種雙向同步串列通訊協定。通訊的兩端通過Clock(時鐘腳)同步,並通過Data(數據腳)交換數據。任何一方如果想抑制另外一方通訊時,只需要把Clock(時鐘腳)拉到低電平。如果是PC機和PS/2鍵盤間的通訊,則PC機必須做主機,也就是說,PC機可以抑制PS/2鍵盤傳送數據,而PS/2鍵盤則不會抑制PC機傳送數據。一般兩設備間傳輸數據的最大時鐘頻率是33kHz,大多數PS/2設備工作在10~20kHz。推薦值在15kHz左右,也就是說,Clock(時鐘腳)高、低電平的持續時間都為40μs。每一數據幀包含11~12個位,具體含義如表1所列。

| 1個起始位 | 總是邏輯0 |

| 8個數據位 | (LSB)低位在前 |

| 1個奇偶校驗位 | 奇校驗 |

| 1個停止位 | 總是邏輯1 |

| 1個應答位 | 僅用在主機對設備的通訊中 |

表中,如果數據位中1的個數為偶數,校驗位就為1;如果數據位中1的個數為奇數,校驗位就為0;總之,數據位中1的個數加上校驗位中1的個數總為奇數,因此總進行奇校驗。

通訊

PS/2設備的Clock(時鐘腳)和Data?數據腳都是集電極開路的,平時都是高電平。當PS/2設備等待傳送數據時,它首先檢查Clock(時鐘腳)以確認其是否為高電平。如果是低電平,則認為是PC機抑制了通訊,此時它必須緩衝需要傳送的數據直到重新獲得匯流排的控制權(一般PS/2鍵盤有16個位元組的緩衝區,而PS/2滑鼠只有一個緩衝區僅存儲最後一個要傳送的數據)。如果Clock(時鐘腳)為高電平,PS/2設備便開始將數據傳送到PC機。一般都是由PS/2設備產生時鐘信號。傳送時一般都是按照數據幀格式順序傳送。其中數據位在Clock(時鐘腳)為高電平時準備好,在Clock(時鐘腳)的下降沿被PC機讀入。PS/2設備到PC機的通訊時序如圖2所示。

PS/2接口

PS/2接口當時鐘頻率為15kHz時,從Clock(時鐘腳)的上升沿到數據位轉變時間至少要5μs。數據變化到Clock(時鐘腳)下降沿的時間至少也有5 μs,但不能大於25 μs,這是由PS/2通訊協定的時序規定的。如果時鐘頻率是其它值,參數的內容應稍作調整。

上述討論中傳輸的數據是指對特定鍵盤的編碼或者對特定命令的編碼。一般採用第二套掃描碼集所規定的碼值來編碼。其中鍵盤碼分為通碼(Make)和斷碼(Break)。通碼是按鍵接通時所傳送的編碼,用兩位十六進制數來表示,斷碼通常是按鍵斷開時所傳送的編碼,用四位十六進制數來表示。

編程過程

PS/2設備主要用於產生同步時鐘信號和讀寫數據。

傳送位元組

從PS/2向PC機傳送一個位元組可按照下面的步驟進行:

(1)檢測時鐘線電平,如果時鐘線為低,則延時50μs;

(2)檢測判斷時鐘信號是否為高,為高,則向下執行,為低,則轉到(1);

(3)檢測數據線是否為高,如果為高則繼續執行,如果為低,則放棄傳送(此時PC機在向PS/2設備傳送數據,所以PS/2設備要轉移到接收程式處接收數據);

(4)延時20μs(如果此時正在傳送起始位,則應延時40μs);

(5)輸出起始位(0)到數據線上。這裡要注意的是:在送出每一位後都要檢測時鐘線,以確保PC機沒有抑制PS/2設備,如果有則中止傳送;

(6)輸出8個數據位到數據線上;

(7)輸出校驗位;

(8)輸出停止位(1);

(9)延時30μs(如果在傳送停止位時釋放時鐘信號則應延時50μs);

通過以下步驟可傳送單個位:

(1)準備數據位(將需要傳送的數據位放到數據線上);

(2)延時20μs;

(3)把時鐘線拉低;

(4)延時40μs;

(5)釋放時鐘線;

(6)延時20μs。

接收位元組

由於PS/2設備能提供串列同步時鐘,因此,如果PC機傳送數據,則PC機要先把時鐘線和數據線置為請求傳送的狀態。PC機通過下拉時鐘線大於100μs來抑制通訊,並且通過下拉數據線發出請求傳送數據的信號,然後釋放時鐘。當PS/2設備檢測到需要接收的數據時,它會產生時鐘信號並記錄下面8個數據位和一個停止位。主機此時在時鐘線變為低時準備數據到數據線,並在時鐘上升沿鎖存數據。而PS/2設備則要配合PC機才能讀到準確的數據。具體連線步驟如下:

(1)等待時鐘線為高電平。

(2)判斷數據線是否為低,為高則錯誤退出,否則繼續執行。

(3)讀地址線上的數據內容,共8個bit,每讀完一個位,都應檢測時鐘線是否被PC機拉低,如果被拉低則要中止接收。

(4)讀地址線上的校驗位內容,1個bit。

(5)讀停止位。

(6)如果數據線上為0(即還是低電平),PS/2設備繼續產生時鐘,直到接收到1且產生出錯信號為止(因為停止位是1,如果PS/2設備沒有讀到停止位,則表明此次傳輸出錯)。

(7)輸出應答位。

(8) 檢測奇偶校驗位,如果校驗失敗,則產生錯誤信號以表明此次傳輸出現錯誤。

(9)延時45 μs,以便PC機進行下一次傳輸。

讀數據線的步驟如下:

(1)延時20μs;

(2)把時鐘線拉低;

(3)延時40μs;

(4)釋放時鐘線;

(5)延時20μs;

(6)讀數據線。

下面的步驟可用於發出應答位;

(1)延時15μs;

(2)把數據線拉低;

(3)延時5μs;

(4)把時鐘線拉低;

(5)延時40μs;

(6)釋放時鐘線;

(7)延時5μs;

(8)釋放數據線。