計算機中的數字電路設計

闡述了計算機數字電路中的組合邏輯電路的常用設計方法和時序邏輯電路的常用設計方法。

組合邏輯和時序邏輯電路的了解

所謂組合邏輯電路是指任何時刻輸出信號的穩態值僅決定於該時刻各個輸入信號取值組合的電路,而輸入信號作用所處的電路狀態對輸出信號沒有影響。例如計算機中的編碼器、解碼器、比較器、半加器、全加器、多路選擇器、唯讀存儲器等都屬於組合邏輯電路。所謂時序邏輯電路是指在數字電路中,凡是任一時刻的穩態輸出不僅取決於該時刻的輸入,而且還和電路原來狀態有關。例如計算機的計數器、暫存器、順序脈衝發生器等均屬於時序邏輯電路。

組合邏輯電路的設計方法

電路的設計過程:

1、假設兩個相加數為 Ai、 Bi,兩二進制數相加的和為 Si,相加後向高位的進位為 Ci。

2、對應於Ai、 Bi分別取不同的組合, Si、 Ci得到不同的值。

3、根據真值寫出邏輯表達式:因為只有當 Ai、 Bi的取值組合為01或10時, Si取值才為1。

歸納起來,數字電路中組合邏輯電路的設計可以分為以下幾個步驟:

第一步,分析輸入量和輸出量之間的關係;

第二步,根據分析的結果,列出真值表;

第三步,根據真值表寫出邏輯表達式;

第四步,根據邏輯表達式,畫出邏輯圖。

時序邏輯電路的設計方法

用D觸發器實現一個路口的交通燈自動控制器。要求 :

1.分析設計要求,建立原始狀態圖和狀態表;

2.求出最簡激勵函式和輸出涵數;

3.系統要有自啟動功能。

假設:

1) Z1是由左向右行駛車輛的交通燈信號, Z1=1表示綠燈亮, Z1=0表示紅燈亮;

2) Z2是由右向左行駛車輛的交通燈信號, Z2=1表示綠燈亮,Z2=0表示紅燈亮

3) Z3是人行橫道交通燈信號, Z3=1表示綠燈亮, Z3=0表示紅燈亮;

4)在人行橫道旁有一個人工控制的按鈕 X,當行人要求穿過人行橫道時,須按下按鈕 X(即 X=1)。

5)控制器的時鐘信號每一分鐘為一個周期。

設計條件:

a)在無行人穿過人行橫道時,控制器處於車輛通過狀態,控制器控制從左向右和從右向左行駛的車輛交替通過1分鐘,人行橫道始終保持紅燈亮。

b)當有行人要求穿過人行橫道時,控制器從車輛通過狀態轉到行人通過狀態,在此狀態下人行橫道的綠燈亮1分鐘,紅燈再亮1分鐘,在此過程中,道路左右兩側始終保持紅燈亮。此後,控制器轉入車輛通過狀態。

c)控制器僅在處於車輛通過狀態時,才回響人工控制按鈕的信號。

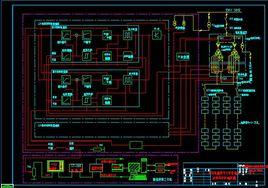

某設備數字計算機系統電路板測試技術

設計了一種數字計算機系統電路板測試儀,提出了一種基於故障診斷的電路板測試方法。

組合電路的測試生成算法

組合電路的測試生成算法有布爾差分法、D算法、PDEM算法以及FAN算法等。布爾差分法要大量處理文字元號的計算,在計算機上運行有一定的困難。與布爾差分法相比,D算法雖然很容易用計算機來實現,但是其運行過程中存在大量的返回操作,使得計算時間過長。PODEM算法吸收了窮舉法的優點,對D算法進行了有益的改進,提高了運算的速度,但是它不能夠及早發現不存在解的情況,無效的選擇和返回的次數還是很多。針對各種算法所存在的不足,FAN算法採取以下措施,無論是在計算速度上還是減少無效選擇和返回次數上都有了很大的提高和改進,具有較強的實用性。

( 1) FAN算法的蘊含操作同時作前後向蘊含,在算法的每一步儘可能多地確定已唯一隱含的信號值;

( 2) 故障值分配給由故障唯一隱含的地方;

( 3) D前沿中只有一個元件時,可以選擇一條唯一確定的敏化通路;

( 4) 反向蘊涵只要到主導線即可停止,而不必要再向後作蘊含,主導線的值可以推遲到最後去確認。主導線上的值只要做一次確認即可實現。

時序電路的測試生成算法

時序電路由於內部有存儲元件,它的輸出不僅決定於當前的輸入信號,而且決定於存儲元件的狀態,因此對於它進行故障檢測或故障診斷比組合電路要困難得多。由於組合電路的測試生成不僅在理論上比較成熟,而且有具體的方法和程式可供使用,因此時序電路測試生成的基本思路是:將時序電路先轉換成組合電路,然後套用組合電路的測試生成方法進行測試生成。但是時序電路與組合電路之間也存在一些差異:時序電路的初態問題、時序電路測試生成的時限問題以及時序電路中的故障模型和故障傳輸問題等。

對於時序電路當中的同步時序電路,其測試生成算法是將時序電路轉換成組合電路後按照組合電路的測試方法進行測試,其測試生成算法與組合電路相同。對於異步時序電路採用改進的九值算法進行測試向量的生成。九值算法比一般的擴展D算法在作D驅趕時要減少很多次無用的計算,同時它充分考慮了故障在重複陣列模型中的重複影響作用,從而可減少計算機的工作量,而且有可能對用一般D算法無法產生測試的故障產生測試矢量。