在一些正處於研究階段的套用中,外延能達到製造未來高性能IC的要求。例如用來獲得低的接觸電阻的抬高的源漏結構(S/D)。通過在器件的源端、漏端和柵區域澱積外延矽可以形成抬髙的源漏結構。這能有效地增加源漏的表面積因此降低薄層電阻(類似於相同材料下直徑大的導線比直徑小的導線電阻小)。

在外延澱積過程中,可能發生不希望的摻雜不均勻現象。因為輕摻雜外延層通常生長在重摻雜襯底上,外延層會發生自摻雜現象。這種現象發生在摻雜雜質從襯底蒸發,或者是由於澱積過程中氯對矽片表面的腐蝕而自發進行。這些雜質進人氣流並導致不希望的外延摻雜。作為外延層生長,來自矽片的雜質很少,氣流中的雜質達到一個恆定的水平。另外的不規則摻雜形式是襯底作為摻雜雜質源擴散到外延層,這稱為外擴散。自摻雜和外擴散都能影響雜質在襯底和外延層之間形成過渡,導致雜質分布不如預想的那樣陡。

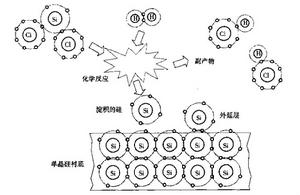

圖1 矽片上外延生長矽

圖1 矽片上外延生長矽如果膜和襯底的材料相同(例如矽襯底上長矽膜),這樣的膜生長稱為同質外延。膜材料與底材料不一致的情況(例如矽襯底上長氧化鋁)較少,稱為異質外延。