真值表及符號

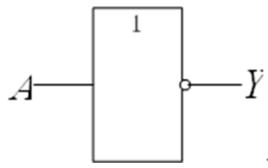

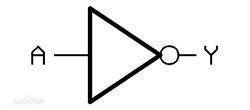

能實現非邏輯功能的電路稱為非門電路,又稱反相器,簡稱非門。下列包括“非”門的2種符號。

ANSI/IEEE Std 91-1984

ANSI/IEEE Std 91-1984 IEC 60617-12

IEC 60617-12圖形符號:

形狀特徵型符號(ANSI/IEEE Std 91-1984)、IEC矩形國標符號(IEC 60617-12)。

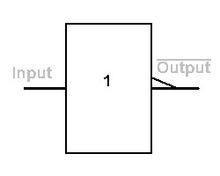

軟體中符號:NOT/7404

真值表:

| A | Y |

| 1 | 0 |

| 0 | 1 |

具體實現

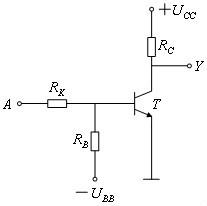

設計一:利用三極體進行非門的實現

“非”門電路

“非”門電路 “非”門電路

“非”門電路 “非”門電路

“非”門電路電晶體“非”門電路不同於放大電路,管子的工作狀態或從截止轉為飽和,或從飽和轉為截止。“非”門電路只有一個輸入端A,當A為“1”(設其電位為3V)時,電晶體飽和,其集電極,即輸出端Y為“0”(其電位在零伏附近);當A為“0”時,電晶體截止,輸出端Y為“1”(其電位近似等於)。所以“非”門電路也稱為反相器。加負電源是為了使電晶體可靠截止。

“非”門電路

“非”門電路 “非”門電路

“非”門電路 “非”門電路

“非”門電路 “非”門電路

“非”門電路 “非”門電路

“非”門電路 “非”門電路

“非”門電路 “非”門電路

“非”門電路圖中,是“非”門的門電阻,其作用是通過它向輸出端提供電壓。T飽和,上產生很大的壓降,使集電極電位幾乎與發射極的電位相等;截止時,通過加到集電極上,使集電極電壓等於。是輸入電阻,通過它給T加正向偏置電流,即輸入信號。是反偏電阻,通過它給T加反向偏置電流。這兩個電阻配合得當,才可以使輸入“1”時T飽和導通,輸入“0”時T可靠截止。

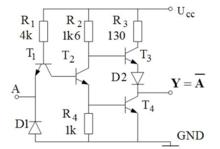

設計二:TTL非門電路的實現

“非”門電路

“非”門電路這裡T1不是當成三極體使用的,而是具有一個正極、兩個負極的特殊二極體。因為一般三極體發射結有電流時,就產生大很多倍的電流流進管子。這裡T1“發射結”有電流時,集電極根本無電流。"發射結”有電流時,集電極產生電流流出管子。

從4kΩ電阻到T的“集電結”,到T的發射結,再到1kΩ電阻,實際是兩隻電阻、兩隻PN結組成的串聯分壓電路,在這個迴路中,越往下電位就越低。所以T的基極電位總是高於集電極0.7V的。PN結正向壓降0.7V,兩隻PN結正向壓降1.4V,那么兩隻電阻壓降為(5-1.4)V=3.6V,4kΩ電阻壓降為[4/(4+1)]×3.6V≈2.9V,故T1集電極電壓為5-2.9-0.7=1.4V。

A端輸入3.6V以上高電平電壓時,T集電極1.4V電壓低於發射極電壓,4kΩ電阻電流經T集點結流向T發射結,使T飽和,T飽和,電路輸出低電平。

“非”門電路

“非”門電路A端輸入1V以下低電平電壓時,T發射極電壓低於集電極1.4V電壓,4kΩ電阻電流經T發射結流向低電平輸入端A,T得不到電流而截止,T截止,經R使T飽和導通,電路輸出高電平,實現非邏輯關係。

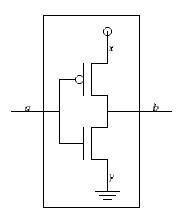

設計三:利用CMOS邏輯進行非門的實現

“非”門電路

“非”門電路兩管的柵極相連作為輸入端,兩管的漏極相連作為輸出端。TN的源極接地,TP的源極接電源。為了保證電路正常工作,VDD需要大於TN管開啟電壓VTN和TP管開啟電壓VTP的絕對值的和,即UDD > UTN + |UTP|。當Ui=0V時,TN截止,TP導通,Uo≈UDD為高電平;當Ui=UDD時,TN導通,TP截止,Uo≈0V為低電平。因此實現了非邏輯功能。

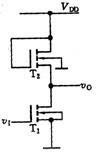

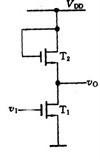

設計四:利用NMOS邏輯進行非門的實現

NMOS邏輯門電路是全部由N溝道MOSFET構成。由於各種器件具有較小的幾何尺寸,適合於製造大規模積體電路。此外,由於NMOS積體電路的結構簡單,易於使用CAD技術進行設計。與CMOS電路相似,NMOS電路中不使用難於製造的電阻。NMOS反相器是整個NMOS邏輯門電路的基本構件,它的工作管常用增強型器件,而負載管可以是增強型也可以是耗盡型。現以增強型器件作為負載管的NMOS反相器為例來說明它的工作原理。

(a)實際電路

(a)實際電路 (b)簡化畫法

(b)簡化畫法圖(a)表示NMOS反相器的原理電路,其中為工作管,為負載管,二者均屬增強型器件。若和在同一工藝過程中製成,它們必將具有相同的開啟電壓VT。圖(b)是它的簡化畫法。負載管的柵極與漏極同接電源,因而總是工作在它的恆流區,處於導通狀態。

當輸入為高電壓(超過管子的開啟電壓VT)時,導通,輸出為低電壓。輸出低電壓的值由、兩管導通時所呈現的電阻值之比決定。通常的跨導gm1遠大於管的跨導gm2,以保證輸出低電壓值在 1V左右。當輸入電壓為低電壓(低於管子的開啟電壓VT)時,截止,輸出為高電壓。由於管總是處於導通狀態,因此輸出高電壓值約為(VDD-VT)。通常gm1在100~200μS之間,而gm2約為5~15μS。導通時的等效電阻Rds1約為3~10kΩ,而的Rds2約在100~200kΩ之間。負載管導通電阻是隨工作電流而變化的非線性電阻。

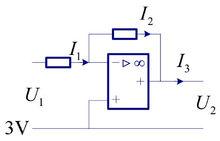

設計五:利用理想運算放大器進行非門的實現

“非”門電路

“非”門電路 “非”門電路

“非”門電路由“虛斷”概念,可知 ,而又由“虛短”可知運放器輸入端電壓為零。設兩個電阻的阻值相等,則可以得到方程:

“非”門電路

“非”門電路於是可得,當左端輸入為+6V 時,右端輸出為 0V;當左端輸入為 0V時,右端輸出為+6V。於是達到了非門的作用。

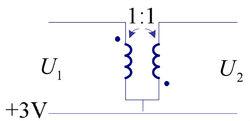

設計六:利用變壓器進行非門的實現

“非”門電路

“非”門電路利用理想變壓器的特性,可以發現,於是,當左端輸入電壓為+6V,右端的輸出電壓為 0V;當左端輸入電壓為 0V,右端的輸出電壓為+6V。由此達到了非門的作用。

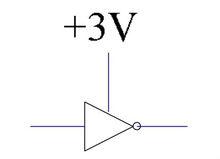

由上述設計可以發現,將非門利用連線埠電路取代的話,為下圖所示:

“非”門電路

“非”門電路積體電路

非門是基本的邏輯門,因此在TTL和CMOS積體電路中都是可以使用的。標準的積體電路有74X04和CD4049。74X04TTL晶片有14個引腳,4049CMOS晶片有16個引腳,兩種晶片都各有2個引腳用於電源供電/基準電壓,12個引腳用於6個反相器的輸入和輸出(4049有2個引腳懸空)。

在數字電路中最具代表性的CMOS非門積體電路是CD4069

“非”門電路

“非”門電路 “非”門電路

“非”門電路