定義

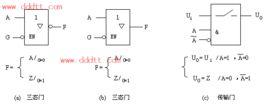

用以實現基本邏輯運算和複合邏輯運算的單元電路稱為門電路。常用的門電路在邏輯功能上有與門、或門、非門、與非門、或非門、與或非門、異或門等幾種。

性質

門電路輸入

“門”是這樣的一種電路:它規定各個輸入信號之間滿足某種邏輯關係時,才有信號輸出,通常有下列三種門電路:與門、或門、非門(反相器)。從邏輯關係看,門電路的輸入端或輸出端只有兩種狀態,無信號以“0”表示,有信號以“1”表示。也可以這樣規定:低電平為“0”,高電平為“1”,稱為正邏輯。反之,如果規定高電平為“0”,低電平為“1”稱為 負邏輯,然而,高與低是相對的,所以在實際電路中要先說明採用什麼邏輯,才有實際意義,例如,負與門對“1”來說,具有“與”的關係,但對“0”來說,卻有“或”的關係,即負與門也就是正或門;同理,負或門對“1”來說,具有“或”的關係,但對“0”來說具有“與”的關係,即負或門也就是正與門。

基本邏輯電路

凡是對脈衝通路上的脈衝起著開關作用的電子線路就叫做門電路,是基本的邏輯電路。門電路可以有一個或多個輸入端,但只有一個輸出端。門電路的各輸入端所加的脈衝信號只有滿足一定的條件時,“門”才打開,即才有脈衝信號輸出。從邏輯學上講,輸入端滿足一定的條件是“原因”,有信號輸出是“結果”,門電路的作用是實現某種因果關係──邏輯關係。所以門電路是一種邏輯電路。基本的邏輯關係有三種:與邏輯、或邏輯、非邏輯。與此相對應,基本的門電路有與門、或門、非門。

積體電路

分立元件組成

門電路可用分立元件組成,也可做成積體電路,但目前實際套用的都是積體電路。由於單一品種的與非門可以構成各種複雜的數字邏輯電路,而器件品種單一,給備件、調試都會帶來很大方便,所以積體電路工業產品中並沒有與門、或門,而供應與非門。

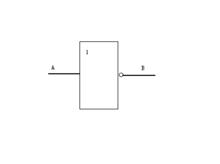

非門:利用內部結構,使輸入的電平變成相反的電平,高電平(1)變低電平(0),低電平(0)變高電

門電路

門電路平(1)。

| A | B |

| 0 | 1 |

| 1 | 0 |

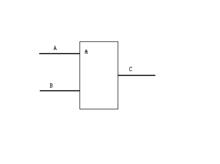

與門:利用內部結構,使輸入兩個高電平(1),輸出高電平(1),不滿足有兩個高電平(1)則輸出低電平(0)。

門電路

門電路| A | B | C |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

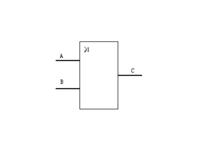

門電路

門電路或門:利用內部結構,使輸入至少一個輸入高電平(1),輸出高電平(1),不滿足有兩個低電(0)輸出高電平(1)

| A | B | C |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

門電路真值表

與門電路真值表:

A B 結果

0 0 0

0 1 0

1 0 0

1 1 1

或門電路真值表:

A B 結果

0 0 0

0 1 1

1 0 1

1 1 1

非門電路真值表:

A 結果

0 1

1 0

積體電路原理

門電路

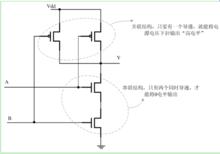

門電路目前實際套用的門電路都是積體電路。在積體電路設計過程中,將複雜的邏輯函式轉換為具體的數字電路時,不管是手工設計還是EDA工具自動設計,通常要用到七種基本邏輯(與、或、非、與非、或非、同或、異或)的圖形表示,在電路術語中這些邏輯操作符號被稱作門,對應的具體電路就叫做門電路,包括某個基本邏輯或者多個基本邏輯組合的複雜邏輯。比如實現取反功能的反相器,就叫做非門;實現“先與後反”功能的就是與非門,如下圖所示。與非門由兩個N管和兩個P管組成:P管並聯,一端接電源;N管串聯,一端接地。根據CMOS結構互補的思想,每個N管都會和一個P管組成一對,它們的柵極連在一起,作為與非門的輸入;輸出則在“串-並”結構的中間。當輸入端A、B中只要有一個為0時,下面接地的通路斷開,而上面接電源的通路導通,就輸出高電平1;而只有A、B同時為1時,才會使接地的兩個串聯NMOS管都導通,從而輸出低電平0。而這正是與非門的邏輯:只有兩個輸入都為1時,輸出為0;否則結果為1。

門電路

門電路上述7種基本邏輯對應的門即為:與門、或門、非門、與非門、或非門、異或門、同或門。另外還有一個常用的基本門電路叫傳輸門,可以模擬“開關”的動作,當然也是由MOS-FET組成的,利用了其柵電壓控制MOS管導通的原理;當CP為1,A的數據可以傳到B端,當CP為0時,其內部電晶體截止,可以把電路中的通路臨時關斷。它們的邏輯符號如右圖所示。

門電路幾乎可以組成數字電路裡面任何一種複雜的功能電路,包括類似於加法、乘法的運算電路,或者暫存器等具有存儲功能的電路,以及各種自由的控制邏輯電路,都是由基本的門電路組合而成的。

電路結構類型

門電路輸出端的電路結構有三種型式:有源負載推拉式(或互補式)輸出、集電極(或漏極)開路輸出和三態輸出。

推拉式輸出的門電路一般用於完成邏輯運算。集電極開路的門電路(OC門)在實現一定邏輯功能的同時,還能實現電平變換或驅動較高電壓、較大電流的負載:可以把兩個門的輸出端直接並聯,實現邏輯與的功能(稱“線與”聯接)。三態輸出門廣泛套用於和系統匯流排的聯接以及實現信號雙向傳輸等方面。