結構組成

CD4013由兩個相同的、相互獨立的數據型觸發器構成。每個觸發器有獨立的數據、置位、復位、時鐘輸入和Q及Q輸出。此器件可用作移位暫存器,且通過將Q輸出連線到數據輸入,可用作計數器和觸發器。在時鐘上升沿觸發時,加在D輸入端的邏輯電平傳送到Q輸出端。置位和復位與時鐘無關,而分別由置位或復位線上的高電平完成。

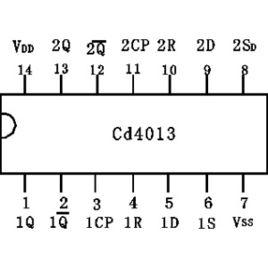

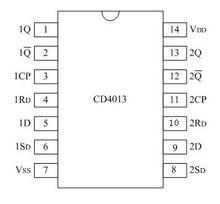

電路引腳圖

1D、2D:數據輸入端

cd4013

cd40131CP、2CP:時鐘輸入端1Q、2Q:原碼輸出端1 /Q、2 /Q:反碼輸出端

1SD、2SD:直接置位端

1RD、2RD:直接復位端

VDD:電源正

VSS:地

電路真值表

CD4013有兩個D觸發器,一個D觸發器有6個端子:2個輸出,4個控制。4個控制分別是R、S、CP、D。

1)R和S不能同時為高電平。

2)當R為1、S為0時,輸出Q一定為0,因此R可稱為復位端。

3)當S為1、R為0時,輸出Q一定為1。

4)當R、S均為0時,Q在CP端有脈衝上升沿到來時動作,具體是Q=D,即若D為1則Q也為1,若D為0則Q也為0。

| RD(復位端) | SD(置位端) | Q(輸出端) |

| 1 | 0 | 0 |

| 0 | 1 | 1 |

| 0 | 0 | D |

| 1 | 1 | x |

工作原理

設電路初始狀態均在復位狀態,Q1、Q2端均為低電平。當fi信號輸入時,由於輸入端異或門的作用(附表是異或門邏輯功能表),其輸出還受到觸發器IC2的Q2端的反饋控制(非門F2是增加的一級延遲門,A點波形與Q2相同)。在第1個fi時鐘脈衝的上升沿作用下,觸發器IC1、IC2均翻轉。由於Q2端的反饋作用使得異或門輸出一個很窄的正脈衝,寬度由兩級D觸發器和反相門的延時決定。當第1個fi脈衝下跳時,異或門輸出又立即上跳,使IC1觸發器再次翻轉,而IC2觸發器狀態不變。這樣在第1個輸入時鐘的半個周期內促使IC1觸發器的時鐘脈衝端CL1有一個完整周期的輸入,但在以後的一個輸入時鐘的作用下,由於IC2觸發器的Q2端為高電平,IC1觸發器的時鐘輸入跟隨fi信號(反相或同相)。本來IC1觸發器輸入兩個完整的輸入脈衝便可輸出一個完整周期的脈衝,現在由於異或門及IC2觸發器Q2端的反饋控制作用,在第1個fi脈衝的作用下得到一個周期的脈衝輸出,所以實現了每輸入一個半時鐘脈衝,在IC1觸發器的Q1端取得一個完整周期的輸出。

分頻電路

圖3是5/2分頻電路。IC1、IC2、IC3三級D觸發器級聯為8分頻電路,電容C起濾波作用,輸出信號fo從IC2的Q2端輸出。電路中有Q1、Q3兩個反饋控制。從圖4工作波形可知,Q1的反饋信號中每兩個反饋信號中就有一個受到Q3反饋波形的影響,所以在A點僅能形成幾百毫微秒寬的脈衝。由於電容C的作用,Q1的反饋信號(即一窄脈衝)被濾除掉,如圖4波形A的虛線所示。最後在Q2端輸出fo信號。fo每變化一個周期,對應於輸入信號fi的兩個半周期,即fo的頻率為fi的2/5。

圖5是7/2分頻電路。該電路與圖3相似,區別在於電路中一個反饋信號在圖3中是從Q1端引出的,而圖5是從Q2端引出的,fo信號從Q2端輸出。電路有Q2、Q3兩級反饋,由於Q2反饋信號受Q3反饋的影響,在A點僅能形成幾百毫微秒寬的窄脈衝,此窄脈衝被電容C濾除掉,因此Q2反饋不起作用,電路實際上只有一個Q3反饋,因而使得fo輸出信號每變化一個周期,對應於fi輸入信號的三個半周期,即fo的頻率為fi的2/7。其工作波形如圖6所示。

上面介紹的N/2分頻電路僅限於N≤7,當N≥7時,可根據分頻N值的大小,相應增加二分頻級數,並恰當引接反饋信號走線,便可得到N≥7的分頻電路。下面僅介紹一例9/2分頻電路,如圖7所示。圖8是其工作波形。

IC1~IC4四級D觸發器組成16分頻電路,fo信號從Q3輸出,電路有Q1、Q4兩級反饋。其工作原理與上述有關分頻電路相似,波形圖上A點虛線脈衝表示為電容C濾除掉的Q1反饋信號。從圖8中可知,只要fi輸入四個半周期的時鐘信號,就輸出一個周期信號fo,即fo的頻率為fi的2/9。

特性

從以上幾個N/2分頻電路可得到如下幾個特性:

1.電路工作原理是,在第n個周期,末級兩分頻器的輸出為高電平時,輸入時鐘脈衝的上升沿使分頻電路工作;在第n+1個周期,末級兩分頻器的輸出為低電平時,輸入時鐘脈衝的下降沿使分頻電路工作。

2.電路採用的是異步觸發形式,各觸發器的初始狀態不會影響到分頻的功能。如果要求初始狀態為“0”狀態,可以將D觸發器的復位端R引出,接至復位控制電路。

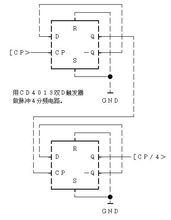

3.輸入信號fi的最高工作頻率fimax除受到CMOS元件fM的限制外,還受到D觸發器、反饋門翻轉延遲和電容C濾波頻率特性的影響,所以應儘可能提高fi的值。一般情況下,最高工作頻率fimax在幾百千赫以下。用CD4013雙D觸發器做的脈衝4分頻器

CD4013組成的4分頻電路

CD4013組成的4分頻電路