產品介紹

PicoBlaze

PicoBlazePicoBlaze是8位微處理器,在Xilinx公司的Virtex、Spartan-II系列以上FPGA與CoolRunner-II系列以上的CPLD器件設計中以IP核的方式提供,使用是免費的。

PicoBlaze起初命名為KCPSM,是Constant(K) Coded Programmable State Machine的簡稱,意為常量編碼可程式狀態機。KCPSM還有個別稱叫Ken Chapman's PSM ,Ken Chapman是Xilinx的微控制器設計者之一。

PicoBlaze是由VHDL語言在早期開發的小型8位軟處理器核心包,其彙編器是簡單的DOS執行檔KCPSM2.exe或KCPSM3.exe,用彙編語言編寫的程式經過編譯後放入FPGA的塊RAM存儲器區。在XC3S500E的FPGA中,只用到了96個Silice,也就是只占用到5%的邏輯資源。PicoBlaze執行一條命令需要2個時鐘周期,在Spartan3E Starter Kit板上以50MHz時鐘為例,PicoBlaze也能達到25MIPS的性能。

處理器版本

KCPSM

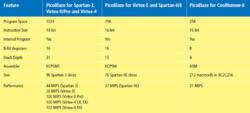

PicoBlaze各版本詳細對比

PicoBlaze各版本詳細對比其支持類型有Virtex, Virtex-E, Spartan-II and Spartan-IIE FPGAs

KCPSM2

其支持類型有Virtex-II, Virtex-II Pro FPGAs

KCPSM3

其支持類型有Spartan-3, Virtex-4, Virtex-II, Virtex-II Pro, Virtex-5, Spartan™-6, Virtex™-6 FPGAs

各版本的詳細對比請點擊右上角展開大圖。

套用框架

Picoblaze提供49個不同指令,16個暫存器(CPLD為8個),256 個直接或間接的可設定地址的連線埠,1 個可禁止的、速率為35MIPS 的中斷。它的性能超過了傳統獨立元器件組成的微處理器,而且成本低,使得PicoBlaze 在數據處理和控制算法領域有著廣泛的套用前景。由於可程式部分也完成嵌入,PicoBlaze 可與子程式和外圍設備結合起來完成特殊的設計。

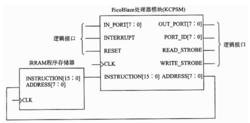

PicoBlaze IP Core套用框架

PicoBlaze IP Core套用框架各連線埠解釋見下表:

| 連線埠 | 功能 | I/O |

| address | 10位地址線 | output |

| instruction | 18位指令輸入 | input |

| port_id | I/O地址控制 | output |

| write_strobe | 寫控制 | output |

| read_strobe | 讀控制 | output |

| interrupt_ack | 中斷回響 | output |

| out_port | 8位輸出接口 | output |

| in_port | 8位輸入接口 | input |

| interrupt | 中斷輸入 | input |

| reset | 復位 | input |

| clk | 時鐘輸入 | input |

| instruction | 18位指令輸出 | output |

處理器架構

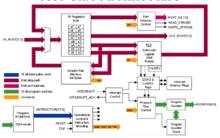

PicoBlaze處理器架構

PicoBlaze處理器架構PicoBlaze 8 位微處理器內部結構如圖所示。PicoBlaze 處理器IP Core 由全局暫存器、計算邏輯單元(ALU)、程式流控制標誌和復位邏輯、輸入/輸出(I/O)、中斷控制器等幾大部分構成。

全局暫存器

16 個8 位全局暫存器,s0~sf。暫存器的操作是非常靈活的;沒有為特殊任務保留暫存器,任何暫存器的優先權都是一樣的。

算術邏輯單元(ALU)

提供了8 位處理器需要的所有簡單操作。執行所有的操作都是用任意一個暫存器提供的運算元完成。若操作需兩個運算元,則有另一暫存器指定或在指令中嵌入一8 位常量值。在不增加程式大小的前提下,指不定期任意常量值,增強了簡單的指令特性。更明白地說,ADD1 與INCREMENT 指令是等價的。若操作超過8 位,則有一選項(增加或減少)可供選擇。二進制操作碼(LOAD、AND、OR、XOR)可操作和測試二進制數,還包括SHIFT 和ROTATE 指令集合。

程式流控制標誌

ALU 操作後的結果影響ZERO 和CARRY 兩個標記。用有條件的或無條件的程式流控制指令決定程式執行的順序。JUMP 指令指定在程式空間內的絕對地址。CALL指令將程式定位到用一段代碼寫的子程式的絕對地址,同時將返回地址壓棧。嵌套CALL 指令使用的棧為15 層,對於程式大小足夠了。

復位邏輯

復位信號強迫程式回到初始狀態,即程式從地址00 開始執行,中斷被禁止,狀態標記和堆疊也同時復位,但暫存器中內容不受影響。

輸入/輸出(I/O)

PicoBlaze 提供256 個輸入連線埠和256 個輸出連線埠。由連線埠匯流排提供一個8 位地址值與一個READ 或WRITE 選通脈衝信號,一起指定訪問連線埠。這個連線埠地址值或為一確定值或由任意一暫存器中內容指定。當訪問一由分散式或塊狀RAM 組成的記憶體時,最好用直接定址。當進行輸入操作時,輸入連線埠上的值被輸出一個READ_STROBE 輸出脈衝時,即表示進行了一次輸入操作。

中斷控制器

PicoBlaze 提供一中斷輸入信號。只要用一些簡單的組合邏輯,多個信號就可進行組合併被套用於這一中斷。程式中可定義此中斷是否被禁止,默認值是中斷被禁止。一被激活的中斷信號使程式執行“CALL FF”指令(FF 即256,程式存儲器的最後一個位置),然後設計者為此定義的放在此處的一段程式被執行。一般在此地址放一JUMP 指令,跳轉到中斷服務程式。中斷進程禁止其它中斷,RETURNI 指令保證在中斷程式結束後,標記和控制指令回到原先的狀態。

指令集

下面列舉了所有代表十六進制的PicoBlaze 操作碼的指令,其中:

①“X”和“Y”代表暫存器,“s”,範圍為0~F;

②“kk”代表常量,“aa”代表地址,“pp”代表連線埠地址,範圍均為00~FF。

程式控制

JUMP aaa

JUMP Z,aaa

JUMP NZ,aaa

JUMP C, aaa

JUMP NC,aaa

CALL

CALL Z,aaa

CALL NZ,aaa

CALL C, aaa

CALL NC,aaa

RETURN

RETURN Z

RETURN NZ

RETURN C

RETURN NC

輸入輸出

INPUT sX,pp

INPUT sX,(sY)

OUTPUT sX,pp

OUTPUT sX,(sY)

邏輯運算

LOAD sXX,kk

AND sXX,kk

OR sXX,kk

XOR sXX,kk

LOAD sXX,sYY

AND sXX,sYY

OR sXX,sYY

XOR sXX,sYY

算術運算

ADD sXX,kk

ADDCY sXX,kk

SUB sXX,kk

SUBCY sXX,kk

ADD sXX,sYY

ADDCY sXX,sYY

SUB sXX,sYY

SUBCY sXX,sYY

移位與反轉

SR0 sXX

SR1 sXX

SRX sXX

SRA sXX

RR sXX

SL0 sXX

SL1 sXX

SLX sXX

SLA sXX

RL sXX

中斷指令

RETURNI ENABLE

RETURNI DISABLE

ENABLE INTERRUPT

DISABLE INTERRUPT

具體細節請參看PicoBlaze的數據手冊。

例化代碼

VHDL版

address : out std_logic_vector(9 downto 0);

instruction : in std_logic_vector(17 downto 0);

port_id : out std_logic_vector(7 downto 0);

write_strobe : out std_logic;

out_port : out std_logic_vector(7 downto 0);

read_strobe : out std_logic;

in_port : in std_logic_vector(7 downto 0);

interrupt : in std_logic;

interrupt_ack : out std_logic;

reset : in std_logic;

clk : in std_logic

Verilog版

output [9:0] address;

input [17:0] instruction;

output [7:0] port_id;

output write_strobe;

output read_strobe;

output interrupt_ack;

output [7:0] out_port;

input [7:0] in_port;

input interrupt;

input reset;

input clk;

output [17:0] instruction;