功能特點

![DDR[記憶體名稱]](/img/9/83b/nBnauM3XwUTM2MTMwITO5ETM2UTM1QDN5MjM5ADMwAjMwUzLykzL2YzLt92YucmbvRWdo5Cd0FmL0E2LvoDc0RHa.jpg) DDR[記憶體名稱]

DDR[記憶體名稱]記憶體又可以叫做主存。是CPU能直接定址的存儲空間,由半導體器件製成。記憶體的特點是訪問數據的速率快。記憶體是電腦中的主要部件,它是相對於外存而言的。我們平常使用的程式,如Windows作業系統、打字軟體、遊戲軟體等,一般都是安裝在硬碟等外存上的,但僅此是不能使用其功能的,必須把它們調入記憶體中運行,才能真正使用其功能,我們平時輸入一段文字,或玩一個遊戲,其實都是在記憶體中進行的。就好比在一個書房裡,存放書籍的書架和書櫃相當於電腦的外存,而我們工作的辦公桌就是記憶體。通常我們把要永久保存的、大量的數據存儲在外存上,而把一些臨時的或少量的數據和程式放在記憶體上,當然記憶體的好壞會直接影響電腦的運行速度。

工作原理

SDRAM在一個時鐘周期內只傳輸一次數據,它是在時鐘的上升期進行數據傳輸;而DDR記憶體則是一個時鐘周期內傳輸兩次數據,它能夠在時鐘的上升期和下降期各傳輸一次數據,因此稱為雙倍速率同步動態隨機存儲器。DDR記憶體可以在與SDRAM相同的匯流排頻率下達到更高的數據傳輸率。

性能特點

與SDRAM相比:DDR運用了更先進的同步電路,使指定地址、數據的輸送和輸出主要步驟既獨立執行,又保持與CPU完全同步;DDR使用了DLL(Delay Locked Loop,延時鎖定迴路提供一個數據濾波信號)技術,當數據有效時,存儲控制器可使用這個數據濾波信號來精確定位數據,每16次輸出一次,並重新同步來自不同存儲器模組的數據。DDR本質上不需要提高時鐘頻率就能加倍提高SDRAM的速度,它允許在時鐘脈衝的上升沿和下降沿讀出數據,因而其速度是標準SDRAM的兩倍。

從外形體積上DDR與SDRAM相比差別並不大,他們具有同樣的尺寸和同樣的針腳距離。但DDR為184針腳,比SDRAM多出了16個針腳,主要包含了新的控制、時鐘、電源和接地等信號。DDR記憶體採用的是支持2.5V電壓的SSTL2標準,而不是SDRAM使用的3.3V電壓的LVTTL標準。

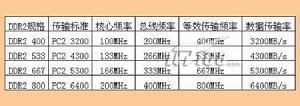

記憶體頻率

DDR記憶體的頻率可以用工作頻率和等效頻率兩種方式表示,工作頻率是記憶體顆粒實際的工作頻率,但是由於DDR記憶體可以在脈衝的上升和下降沿都傳輸數據,因此傳輸數據的等效頻率是工作頻率的兩倍。

什麼是DDR1

有時候大家將老的存儲技術 DDR 稱為 DDR1 ,使之與 DDR2 加以區分。儘管一般是使用 “DDR” ,但 DDR1 與 DDR 的含義相同。

DDR1規格

DDR2.2G

DDR2.2GDDR-200: DDR-SDRAM 記憶晶片在100 MHz下運行 DDR-266: DDR-SDRAM記憶晶片在133 MHz下運行 DDR-333: DDR-SDRAM 記憶晶片在166 MHz下運行 DDR-400: DDR-SDRAM 記憶晶片在200 MHz下運行(JEDEC制定的DDR最高規格) DDR-500: DDR-SDRAM 記憶晶片在250 MHz下運行(非JEDEC制定的DDR規格) DDR-600: DDR-SDRAM 記憶晶片在300 MHz下運行(非JEDEC制定的DDR規格) DDR-700: DDR-SDRAM 記憶晶片在350 MHz下運行(非JEDEC制定的DDR規格)

什麼是 DDR2

DDR2 是 DDR SDRAM 記憶體的第二代產品。它在 DDR 記憶體技術的基礎上加以改進,從而其傳輸速度更快(可達 667MHZ ),耗電量更低,散熱性能更優良 .

DDR2記憶體的頻率

DDR2記憶體的頻率DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設備工程聯合委員會)進行開發的新生代記憶體技術標準,它與上一代DDR記憶體技術標準最大的不同就是,雖然同是採用了在時鐘的上升/下降延同時進行數據傳輸的基本方式,但DDR2記憶體卻擁有兩倍於上一代DDR記憶體預讀取能力(即:4bit數據預讀取)。換句話說,DDR2記憶體每個時鐘能夠以4倍外部匯流排的速度讀/寫數據,並且能夠以內部控制匯流排4倍的速度運行。

DDR3與DDR2的比較

DDR3與DDR2幾個主要的不同之處 :

1.突髮長度(Burst Length,BL)

DDR3

DDR3由於DDR3的預取為8bit,所以突發傳輸周期(Burst Length,BL)也固定為8,而對於DDR2和早期的DDR架構系統,BL=4也是常用的,DDR3為此增加了一個4bit Burst Chop(突發突變)模式,即由一個BL=4的讀取操作加上一個BL=4的寫入操作來合成一個BL=8的數據突發傳輸,屆時可通過A12地址線來控制這一突發模式。而且需要指出的是,任何突發中斷操作都將在DDR3記憶體中予以禁止,且不予支持,取而代之的是更靈活的突發傳輸控制(如4bit順序突發)。

2.定址時序(Timing)

就像DDR2從DDR轉變而來後延遲周期數增加一樣,DDR3的CL周期也將比DDR2有所提高。DDR2的CL範圍一般在2~5之間,而DDR3則在5~11之間,且附加延遲(AL)的設計也有所變化。DDR2時AL的範圍是0~4,而DDR3時AL有三種選項,分別是0、CL-1和CL-2。另外,DDR3還新增加了一個時序參數——寫入延遲(CWD),這一參數將根據具體的工作頻率而定。

其中DDR2 的頻率對照表如右圖所示。

表4.記憶體同步時外頻頻率跟記憶體型號的關係

表4.記憶體同步時外頻頻率跟記憶體型號的關係另外記憶體同步時外頻頻率跟記憶體型號的關係圖:

3.DDR3新增的重置(Reset)功能

重置是DDR3新增的一項重要功能,並為此專門準備了一個引腳。DRAM業界很早以前就要求增加這一功能,如今終於在DDR3上實現了。這一引腳將使DDR3的初始化處理變得簡單。當Reset命令有效時,DDR3記憶體將停止所有操作,並切換至最少量活動狀態,以節約電力。

在Reset期間,DDR3記憶體將關閉內在的大部分功能,所有數據接收與傳送器都將關閉,所有內部的程式裝置將復位,DLL(延遲鎖相環路)與時鐘電路將停止工作,而且不理睬數據匯流排上的任何動靜。這樣一來,將使DDR3達到最節省電力的目的。

4.DDR3新增ZQ校準功能

ZQ也是一個新增的腳,在這個引腳上接有一個240歐姆的低公差參考電阻。這個引腳通過一個命令集,通過片上校準引擎(On-Die Calibration Engine,ODCE)來自動校驗數據輸出驅動器導通電阻與ODT的終結電阻值。當系統發出這一指令後,將用相應的時鐘周期(在加電與初始化之後用512個時鐘周期,在退出自刷新操作後用256個時鐘周期、在其他情況下用64個時鐘周期)對導通電阻和ODT電阻進行重新校準。

參考電壓分成兩個

在DDR3系統中,對於記憶體系統工作非常重要的參考電壓信號VREF將分為兩個信號,即為命令與地址信號服務的VREFCA和為數據匯流排服務的VREFDQ,這將有效地提高系統數據匯流排的信噪等級。

點對點連線(Point-to-Point,P2P)

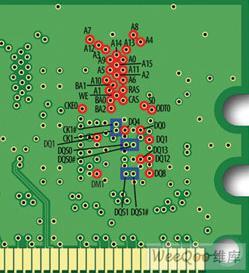

DDR3雙列直插記憶體模組“背面”的測試點

DDR3雙列直插記憶體模組“背面”的測試點這是為了提高系統性能而進行的重要改動,也是DDR3與DDR2的一個關鍵區別。在DDR3系統中,一個記憶體控制器只與一個記憶體通道打交道,而且這個記憶體通道只能有一個插槽,因此,記憶體控制器與DDR3記憶體模組之間是點對點(P2P)的關係(單物理Bank的模組),或者是點對雙點(Point-to-two-Point,P22P)的關係(雙物理Bank的模組),從而大大地減輕了地址/命令/控制與數據匯流排的負載。而在記憶體模組方面,與DDR2的類別相類似,也有標準DIMM(台式PC)、SO-DIMM/Micro-DIMM(筆記本電腦)、FB-DIMM2(伺服器)之分,其中第二代FB-DIMM將採用規格更高的AMB2(高級記憶體緩衝器)。

面向64位構架的DDR3顯然在頻率和速度上擁有更多的優勢,此外,由於DDR3所採用的根據溫度自動自刷新、局部自刷新等其它一些功能,在功耗方面DDR3也要出色得多,因此,它可能首先受到移動設備的歡迎,就像最先迎接DDR2記憶體的不是台式機而是伺服器一樣。在CPU外頻提升最迅速的PC台式機領域,DDR3未來也是一片光明。Intel預計在第二季所推出的新晶片-熊湖(Bear Lake),其將支持DDR3規格,而AMD也預計同時在K9平台上支持DDR2及DDR3兩種規格。

DDR4

據介紹美國JEDEC將會在不久之後啟動DDR4記憶體峰會,而這也標誌著DDR4標準制定工作的展開。一般認為這樣的會議召開之後新產品將會在3年左右的時間內上市,而這也意味著我們將可能在2011年的時候使用上DDR4記憶體,最快也有可能會提前到2010年。

JEDEC表示在7月份於美國召開的存儲器大會MEMCON07SanJose上時就考慮過DDR4記憶體要儘可能得繼承DDR3記憶體的規格。使用Single-endedSignaling( 傳統SE信號)信號方式則表示64-bit存儲模組技術將會得到繼承。不過據說在召開此次的DDR4峰會時,DDR4 記憶體不僅僅只有Single-endedSignaling方式,大會同時也推出了基於微分信號存儲器標準的DDR4記憶體。

DDR4規格

因此DDR4記憶體將會擁有兩種規格。其中使用Single-endedSignaling信號的DDR4記憶體其傳輸速率已經被確認為1.6~3.2Gbps,而基於差分信號技術的DDR4記憶體其傳輸速率則將可以達到6.4Gbps。由於通過一個DRAM實現兩種接口基本上是不可能的,因此DDR4記憶體將會同時存在基於傳統SE信號和微分信號的兩種規格產品。

根據多位半導體業界相關人員的介紹,DDR4記憶體將會是Single-endedSignaling( 傳統SE信號)方式DifferentialSignaling( 差分信號技術 )方式並存。其中AMD公司的PhilHester先生也對此表示了確認。預計這兩個標準將會推出不同的晶片產品,因此在DDR4記憶體時代我們將會看到兩個互不兼容的記憶體產品。

DDR5

新一代的顯存會有較低的能量消耗量,且數據傳輸為每秒6 Gbps

直至目前為止,我們只看到極少數的繪圖卡使用gddr4顯存,但三星已發布下一代的gddr5記憶體,並聲稱它的樣本已經發向了主要的圖形處理器公司。

當然,三星並不是第一家提供gddr5的樣品的公司。海力士Hynix和奇夢達雙方也宣布了類似的零件,但三星的記憶已經進了一步提供了數據傳輸速率6gb/sec ,超過標準5gb/sec 。因此,三星大膽聲稱它的產品為“世界上速度最快的記憶體”並且說,它的產品“能夠傳輸移動影像及相關數據,在24千兆位元組每秒。”

除了增加頻寬, gddr5記憶體也比較低功耗,三星公司聲稱其記憶體運作,只是1.5v 。

三星是採樣512MB的gddr5晶片( 16 MB × 32 ) , mueez 迪恩,三星繪圖記憶體的市場行銷主管,他說:“該記憶體將使種圖形硬體的表現將推動軟體開發商提供了一個新台階眼膨化遊戲。不過,我們可能要等待一段時間, gddr5成為普遍”。三星公司估計,該記憶體將成為在頂級產品細分市場中的的標準。

DDR存儲器電氣特性驗證

幾乎每一個電子設備,從智慧型手機到伺服器,都使用了某種形式的RAM存儲器。儘管快閃記憶體NAND繼續流行(由於各式各樣的消費電子產品的流行),由於SDRAM為相對較低的每比特成本提供了速度和存儲很好的結合,SDRAM仍然是大多數計算機以及基於計算機產品的主流存儲器技術。DDR是雙數據速率的SDRAM記憶體,已經成為今天存儲器技術的選擇。DDR技術不斷發展,不斷提高速度和容量,同時降低成本,減小功率和存儲設備的物理尺寸。

隨著時鐘速率和數據傳輸速率不斷增加和性能的提高,設計工程師必須保證系統的性能指標,或確保系統內部存儲器和存儲器控制設備的互操作性,存儲器子系統的模擬信號完整性已成為設計工程師越來越多重點考慮的問題。許多性能問題,甚至在協定層發現的問題,也可以追溯到信號完整性問題上。因此,存儲器的模擬信號完整性驗證已經成為很多電子設計驗證關鍵的一步。

JEDEC(電子工程設計發展聯合協會)已經明確規定存儲設備詳細測試要求,需要對抖動、定時和電氣信號質量進行驗證。測試參數:如時鐘抖動、建立和保持時間、信號的過沖、信號的下沖、過渡電壓等列入了JEDEC為存儲器技術制定的測試規範。但執行規範里的這些測試是一個很大的挑戰,因為進行這些測試很可能是一個複雜而又耗時的任務。擁有正確的工具和技術,可以減少測試時間,並確保最準確的測試結果。在本套用文章中,我們將討論針對存儲器測試的解決方案,這個方案能夠幫助工程師戰勝挑戰和簡化驗證過程。

信號的獲取和探測

存儲器驗證的第一個難點問題是如何探測並採集必要的信號。JEDEC標準規定的測試應在存儲器元件的BGA(球柵陣列結構的PCB)上。而FBGA封裝組件包括一個焊球連線陣列(這是出於實際目的),無法進入連線,如何進行存儲器的探測呢?

一種解決方案是在PCB布線過程中設計測試點,或探測存儲器元件板的背面的過孔。雖然這些測試點沒有嚴格在“存儲器元件附近”,PCB走線長度一般都比較短,對信號衰減的影響很小。當使用這種方法探測時,信號完整性通常是相當不錯的,可以進行電氣特性的驗證。

對於這種類型套用,可以使用手持探頭,但是在多個探頭前端和測試點同時保持良好的電接觸非常困難。

圖2

圖2考慮到有些JEDEC的測量要求三個或更多的測試點,加上其他信號如晶片選擇信號、RAS和CAS可能需要確定存儲器狀態,許多工程師常常選擇使用焊接式探頭進行連線。

泰克公司開發了一種專為這種類型的套用設計的探測解決方案。P7500系列探頭有4~20GHz的頻寬,是存儲器驗證套用的選擇。圖2說明了幾個可用的P7500系列探頭前端之一,這種探頭非常適合存儲器驗證的套用。這些微波同軸”前端在需要多個探測前端進行焊接情況時提供了有效的解決方案,同時提供優秀的信號保真度和4GHz頻寬,足已滿足存儲器DDR3@1600MT/s的測試需求。

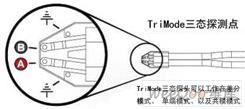

圖3

圖3P7500系列探頭針對存儲器測試套用的另一個優點是泰克專有的TriMode(三態)功能。這種獨特的功能允許探頭不但可以測試+和-差分信號,又可以測試單端信號。使用探頭前端的三個焊接連線,用戶就可以使用探頭上控制按鈕或在示波器選單來對差分和單端探測模式之間進行切換。使用焊接探頭的+連線到單端數據或地址線,使用焊接探頭的-連線到另一相鄰線。然後用戶可以使用一個探頭,通過兩個單端測量模式之間切換,很容易地測量其中任何兩個信號。

然而,很多情況下通過背面過孔探測信號可能不是一種好的選擇。使用嵌入式存儲器設計,存儲器元件背面可能沒有可用的板上空間。甚至很多標準的DIMM,在板的兩面都有存儲器元件,以增加存儲密度。這種情況下,測試工程師怎樣才能探測到測試點呢?

圖4

圖4幸運的是,即使這樣情況,也有探測解決方案。泰克公司與Nexus科技公司合作開發了所有標準DDR3和DDR2存儲器設備轉接板內插板組件。這些轉接板內插板使用插槽代替存儲器元件連線到被測設備。在轉接板有探測的測試點,然後對齊到插槽上的位置。存儲器元件再插到轉接板上。圖4是這種“連線”的示意圖。

記憶體雙通道

很多人經常將DDR/DDR2/DDR3和記憶體的雙通道、三通道技術相混淆,事實上這是兩組毫無關係的概念,DDR/X是一種記憶體的設計技術,而多通道記憶體技術是一種在主機板上實現的並行記憶體訪問技術,與使用的記憶體類型沒有關係。兩個通道甚至可以使用不同速率或訪問時序的記憶體。