1.記憶體管理

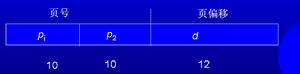

(1) 記憶體地址邏輯地址:CPU所生成的地址。CPU產生的邏輯地址被分為 :p (頁號) 它包含每個頁在物理記憶體中的基址,用來作為頁表的索引;d (頁偏移),同基址相結合,用來確定送入記憶體設備的物理記憶體地址。

物理地址:記憶體單元所看到的地址。邏輯地址空間為2m,且頁大小為2n,那么邏輯地址的高m-n位表示頁號,低n位表示頁偏移。

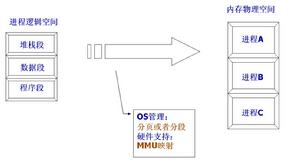

邏輯地址空間:由程式所生成的所有邏輯地址的集合。

物理地址空間:與邏輯地址相對應的記憶體中所有物理地址的集合,用戶程式看不見真正的物理地址。

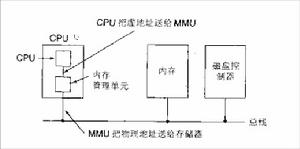

註:用戶只生成邏輯地址,且認為進程的地址空間為0到max。物理地址範圍從R+0到R+max,R為基地址,地址映射-將程式地址空間中使用的邏輯地址變換成記憶體中的物理地址的過程。由記憶體管理單元(MMU)來完成。

地址轉化

地址轉化 MMU的工作原理

MMU的工作原理2. 頁表

(1)分頁技術的簡介用固定大小的頁(Page)來描述邏輯地址空間,用相同大小的頁框(Frame)來描述物理記憶體空間,由作業系統實現從邏輯頁到物理頁框的頁面映射,同時負責對所有頁的管理和進程運行的控制.

(2)頁表的作用實現從頁號到物理塊號的地址映射。

邏輯地址轉換成物理地址的過程是:用頁號p去檢索頁表,從頁表中得到該頁的物理塊號,把它裝入物理地址暫存器中。同時,將頁內地址d直接送人物理地址暫存器的塊內地址欄位中。這樣,物理地址暫存器中的內容就是由二者拼接成的實際訪問記憶體的地址,從而完成了從邏輯地址到物理地址的轉換。

一個32位邏輯地址空間的計算機系統,頁大小為4KB,那么頁表有一百萬條目。假設每個條目占4B,則需要4MB物理地址空間來存儲頁表本身。利用多級頁表,可以減少頁表所占用的空間。

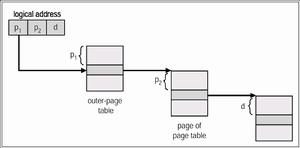

一個邏輯地址(32位系統,頁大小 4K) 可以被分為 :一個20位的頁號 +一個12位的偏移。如果對頁表進行再分頁,那么頁號分解為:一個10位的頁號 +一個10位的偏移。因此,一個邏輯地址表示如下 :p1 是用來訪問外部頁表的索引, p2 是外部頁表的頁偏移。

二級頁表的頁表項

二級頁表的頁表項 兩級頁表的地址轉化

兩級頁表的地址轉化3. 具有TLB(翻譯後備緩衝器)的頁表結構

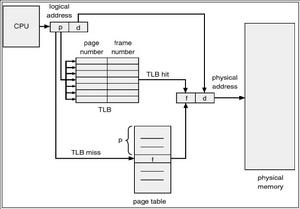

翻譯後備緩衝器TLB(translation lookaside buffer)是小、專用、快速的硬體緩衝,只包括頁表中的一小部分條目。如果頁號在TLB中,得到幀號,訪問記憶體;否則從記憶體中的頁表中得到幀號,將其存入TLB,訪問記憶體。

帶TLB的地址轉化

帶TLB的地址轉化