簡介

邏輯接口是相對於物理接口的而言的,而物理接口就是通常所說的硬體接口,比如usb口,而邏輯接口就是程式中預留的接口。邏輯接口指能夠實現數據交換功能但物理上不存在,需要通過配置建立的接口,包括Dialer(撥號)接口、子接口、LoopBack接口、NULL接口、備份中心邏輯通道以及虛擬模板接口等。

路由器邏輯接口

Dialer接口

Dialer接口即撥號接口。Dialer口下建立撥號規則,物理口引用一個(輪詢DCC,最常用)或多個(共享DCC,極少使用)Dialer口的規則,配置方便,維護簡單.

MFR接口

MFR(MultilinkFrameRelay)接口是多鏈路幀中繼接口,多個物理接口可以同一個MFR接口捆綁起來,從而形成一個擁有大頻寬的MFR接口.當將幀中繼物理接口捆綁進MFR接口之後,其上配置的網路層參數和幀中繼鏈路層參數將不再起作用.在MFR接口上可以配置IP位址等網路層參數和DLCI等幀中繼參數,捆綁在MFR接口內的物理接口都將使用此MFR接口的參數.

LoopBack接口

TCP/IP協定規定,127.0.0.0網段的地址屬於環回地址。包含這類地址的接口屬於環回接口。在華為系列路由器上,定義了接口LoopBack為環回接口,可以用來接收所有傳送給本機的數據包。這類接口上的地址是不可以配置的並且也不通過路由協定對外發布的。

有些套用(比如配置SNA的Localpeer)需要在不影響物理接口配置的情況下,配置一個帶有指定IP位址的本地接口,並且出於節約IP位址的需要,需要配置32位掩碼的IP位址,並且需要將這個接口上的地址通過路由協定發布出去。Loopback接口就是為了滿足這種需要而設計的.

主要用途如下:

1、做管理IP位址

2、做OSPF協定的routerid

3、SNA,啞終端中用來捆綁源地址

4、BGP中作為建立TCP鄰居的源地址

5、測試

NULL接口

Null接口是一種純軟體性質的邏輯接口,任何送到該接口的網路數據報文都會被丟棄,主要用於配置黑洞路由子接口

VRP中提出了子接口的概念,所謂子接口就是在一個物理接口上配置出來的多個邏輯上的虛接口,這些虛接口共用物理接口的物理層參數,又可以分別配置各自的鏈路層和網路層參數.因這樣的多個虛接口可以對應一個物理接口,故常被稱為“子接口”。

備份中心邏輯通道

備份中心不公提供各接口之間的互相備份,也允許將X.25幀中繼等類型的一條虛電路作為備份中心的主接口或備份接口。

為了配置方便,用戶可以對上述虛電路指定相應的邏輯通道,並在邏輯通道中配置備份中心的工作參數.

常用單端邏輯接口電平標準

單端接口具有易於設計和使用的優點,在低於300MHz的場合,單端接口被廣泛使用。

TTL和CMOS

TTL即Transistor—TransistorLogic,三極體結構,5V供電;CMOS即Com—plementaryMetalOxideSemiconduc—tor,是電壓型器件,相對TTL有更大的噪聲容限,輸入阻抗大,5V供電。以前常用的74xx和4000系列器件採用的就分別是TTL和CM0S電平邏輯,目前已較少使用。

LVTTL和LVCMOS

隨著技術和工藝的發展以及設備低功耗等要求,供電電壓越來越低,LVTTL和LVCOMS分別在TTL和CMOS的基礎上發展起來。LVTTL和LVCMOS常用的供電電壓有3.3V、2.5V、1.8V。LVTTLL和LVCMOS驅動和接收器通常是簡單的對稱上下拉結構,只要滿足V和V的高低電平標準和驅動電流範圍,二者就可以相互轉化。圖1(a、b)為LVTTL的輸入電路

和輸出緩中器結構,表1和表2分別為LVTTL和LVCMOS的輸入、輸出電壓和電流規範。

SSTL

SSTL即StubSeriesTerminatedLogic標準,分為SSTL_3、SSTL_2、SSTL_18三種,對應不同的供電電壓,它與LVTTL和LVCMOS的不同在於SSTL是傳輸線終端匹配的,因此SSTL具有輸器,一般有V=1.8V和V=1.5V兩種標準。HSTL和SSTL對參考電平要求均比較高(1%精度)。

常用差分邏輯接口電平標準

差分信號較單端信號能夠以低電壓擺幅提供更大的電壓增益和頻寬,同時還可以去除共模和偶次諧波的干擾,從而提供更高的數據傳輸率。其缺點是差分信號增加了信號管腳,在PCB布線時應考慮阻抗、間距、長度等的匹配。隨著高速實時性數據傳輸的要求越來越高,差分信號套用越來越廣,下面介紹三種最常見的差分邏輯接口標準。

CML

CML電平是所有高速數據接口中最簡單的一種。其輸入和輸出都是匹配好的,減少了外圍器件,適合於更高頻段工作。

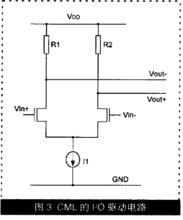

CML的輸入、輸出緩衝電路

CML的輸入、輸出緩衝電路CML的輸入、輸出緩衝電路如圖,R1和R2是為了限制電流,通常數值相等,為50Ω。由圖可以看出,該電路是差分對形式。該差分對的集電極電阻為50Q,輸出信號的高低電平切換是靠共發射極差分對的開關控制的。差分對的發射極到地的恆流源典型值為16mAf圖3中的電流源I1),假定CML的輸出負載為一個50Q上拉電阻,則單端CML輸出信號的擺幅為Vcc~Vcc一0.4V,改變l1的數值則改變了電壓的擺幅。

CML到CML之間的連線分兩種情況:當收發兩端的器件使用相同的電源時,CML到CML可以採用直流耦合方式,不用加任何器件;當收發兩端器件採用不同電源時,一般要考慮交流耦合,中間加耦合電容(注意這時選用的耦合電容要足夠大,以避免在較長連0或連1情況出現時,接收端差分電壓變小)。CML也有不足,即由於自身驅動能力有限,CML更適於晶片間較短距離的連線,而且不同用戶間CML接口實現方式差異較大,所以現有器件提供CML接口的數目還不是非常多。

ECL、PECL和LVPECL

ECL(EmitterCoupledLogic)即射極耦合邏輯,是帶有射隨輸出結構的典型輸入、輸出接口電路,ECL電路的最大特點是其基本門電路工作在非飽和狀態,正因為如此,ECL電路的最大優點是具有相當高的速度,平均延遲時間可達ns數量級甚至更少。

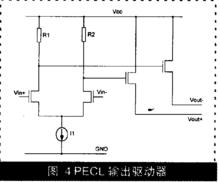

PCEL輸出驅動器

PCEL輸出驅動器傳統的ECL以Vcc為零電壓,V為-5.2V電源,Vo=Vcc-0.9V=-0.9V,VOL=Vcc-1.7V=-1.7V,所以ECL電路的邏輯擺幅較小(僅約0.8V)。當電路從一種狀態過渡到另一種狀態時,對寄生電容的充放電時間將減少,這也是ECL電路具有高開關速度的重要原因。另外,ECL電路是由一個差分對管和一對射隨器組成的,如圖4所示,所以輸入阻抗大,輸出阻抗小,驅動能力強,信號檢測能力高,差分輸出,抗共模干擾能力強;但是由於單元門的開關管對是輪流導通的,對整個電路來講沒有“截止”狀態,所以電路的功耗較大。

PECL(PositiveEmitterCoupledLogic)將ECL電路中的負電源改用正電源(+5V),可將Vcc接到正電源而V接到零點。如果採用+3.3V供電,則稱為LVPECL。由圖可以看出,PECL是開路輸出,所以需用下拉電阻到地。不過同CML一樣,LVPECL輸出高低電平的擺幅因製造商不同而不同,它不僅與外部電阻有關,與邏輯門的VDD也有關。

LVDS

即低電壓差分信號,的驅動器由驅動差分線對的電流源組成,如圖所示,電流通常為3.5mA。接收器具有很高的輸入阻抗,因此驅動器輸出的大部分電流都流過的100Ω匹配電阻,並在接收器的輸入端產生大350mV約的電壓。當驅動器翻轉時,它改變流經電阻的電流方向,因此產生有效的邏輯“1”和邏輯“0”狀態。