電路特點

組合電路在邏輯功能上的共同特點:從組合電路的邏輯功能不難想到,既然其輸出與電路的歷史狀況無關,那么電路中就不能包含記憶(存儲)單元。這是組合電路在電路結構上的共同特點。

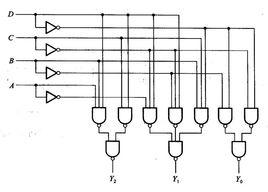

對於組合邏輯電路,其邏輯函式如下:

組合邏輯電路

組合邏輯電路 組合邏輯電路

組合邏輯電路 組合邏輯電路

組合邏輯電路其中,為輸入變數,為輸出變數。

電路設計

對於一個邏輯表達公式或邏輯電路,其真值表可以是惟一的,但其對應的邏輯電路或邏輯表達式可能有多種實現形式,所以,一個特定的邏輯問題,其對應的真值表是惟一的,但實現它的邏輯電路是多種多樣的。在實際設計工作中,如果由於某些原因無法獲得某些門電路,可以通過變換邏輯表達式變電路,從而能使用其他器件來代替該器件。同時,為了使邏輯電路的設計更簡潔,通過各方法對邏輯表達式進行化簡是必要的。組合電路可用一組邏輯表達式來描述。設計組合電路直就是實現邏輯表達式。要求在滿足邏輯功能和技術要求基礎上,力求使電路簡單、經濟、可靠、實現組合邏輯函式的途徑是多種多樣的,可採用基本門電路,也可採用中、大規模積體電路。其一般設計步驟為:分析設計要求,列真值表;然後,進行邏輯和必要變換,得出所需要的最簡邏輯表達式;畫邏輯圖。

電路分析

在asic設計和pld設計中組合邏輯電路設計的最簡化是很重要的,在設計時常要求用最少的邏輯門或導線實現。在asic設計和pld設計中需要處理大量的約束項,值為1或0的項卻是有限的,提出組合邏輯電路設計的一種新方法。

與邏輯表示只有在決定事物結果的全部條件具備時,結果才發生。輸出變數為1的某個組合的所有因子的與表示輸出變數為1的這個組合出現、所有輸出變數為0的組合均不出現,因而可以表示輸出變數為1的這個組合。 組合邏輯電路的分析分以下幾個步驟:

(1)有給定的邏輯電路圖,寫出輸出端的邏輯表達式;

(2)列出真值表;

(3)通過真值表概括出邏輯功能,看原電路是不是最理想,若不是,則對其進行改進。

常見組合電路

編碼器

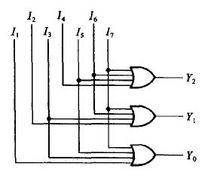

3位二進制編碼器

3位二進制編碼器在數字系統中,為了區分一系列不同的事物,將其中的每個事物用一個二值代碼表示,這就是編碼的含意。在二值邏輯電路中,信號都是以高、低電平的形式給出的。因此,編碼器(Encoder)的邏輯功能就是將輸人的每一個高、低電平信號編成一個對應的二進制代碼。

目前經常使用的編碼器有普通編碼器和優先編碼器兩類。在普通編碼器中,任何時刻只允許輸人一個編碼信號,否則輸出將發生混亂。

在優先編碼器(priorityencoder)電路中,允許同時輸人兩個以上的編碼信

號。不過在設計優先編碼器時已經將所有的輸人信號按優先順序排了隊,當幾個輸人信號同時出現時,只對其中優先權最高的一個進行編碼。

解碼器

解碼器(Decoder)的邏輯功能是將每個輸人的二進制代碼譯成對應的輸出高、低電平信號或另外一個代碼。因此,解碼是編碼的反操作。常用的解碼器電路有二進制解碼器、二一十進制解碼器和顯示解碼器三類。

數據選擇器

數據選擇器 它就是從多個輸入端中選擇一路輸出,它相當於一個多路開關。常用的有二選一,四選一,八選一和十六選一,若需更多則由上述擴展。

加法器

實現多位二進制數相加的電路稱為加法器。根據進位方式不同,有串列進位加法器和超前進位加法器兩種。