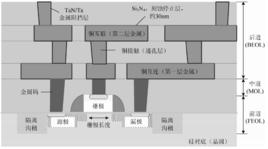

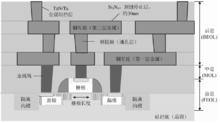

目前大多選用 Cu 作為導電金屬,因此後道又被稱為 Cu 互聯(interconnect)。這些銅線負責把襯底上的電晶體按設計的要求連線起來,實現特定的功能。圖1是一個邏輯器件的剖面示意圖。新的集成技術在晶圓襯底上也添加了很多新型功能材料,例如:後道(BEOL)的低介電常數(εr < 2.4)絕緣材料,它是多孔的能有效降低後道金屬線之間的電容 。由於對Low-K材料的要求不斷提高,僅僅進行單工程開發評估是不夠的。為了達到總體最最佳化,還需要進行綜合評估,以解決多步驟的問題 。

後道工序

後道工序圖1 一個邏輯器件的剖面示意圖