基本信息

定義

在各單元不按規定順序執行完指令後還必須由相應電路再將運算結果重新按原來程式指定的指令順序排列後才能返回程式。這種將各條指令不按順序拆散後執行的運行方式就叫亂序執行(也有叫錯序執行)技術。

解釋

這樣將根據個電路單元的狀態和各指令能否提前執行的具體情況分析後,將能提前執行的指令立即傳送給相應電路單元執行,在這期間不按規定順序執行指令,然後由重新排列單元將各執行單元結果按指令順序重新排列。採用亂序執行技術的目的是為了使CPU內部電路滿負荷運轉並相應提高了CPU的運行程式的速度。分枝技術:(branch)指令進行運算時需要等待結果,一般無條件分枝只需要按指令順序執行,而條件分枝必須根據處理後的結果,再決定是否按原先順序進行。

目的

採用亂序執行技術的目的是為了使CPU內部電路滿負荷運轉並相應提高了CPU的運行程式的速度。

這好比請A、B、C三個名人為晚會題寫橫幅“春節聯歡晚會”六個大字,每人各寫兩個字。如果這時在一張大紙上按順序由A寫好"春節"後再交給B寫"聯歡",然後再由C寫"晚會",那么這樣在A寫的時候,B和C必須等待,而在B寫的時候C仍然要等待而A已經沒事了。

但如果採用三個人分別用三張紙同時寫的做法, 那么B和C都不必須等待就可以同時各寫各的了,甚至C和B還可以比A先寫好也沒關係(就象亂序執行),但當他們都寫完後就必須重新在橫幅上(自然可以由別人做,就象CPU中亂序執行後的重新排列單元)按"春節聯歡晚會"的順序排好才能掛出去。

工作原理

在按序執行中,一旦遇到指令依賴的情況,流水線就會停滯,如果採用亂序執行,就可以跳到下一個非依賴指令並發布它。這樣,執行單元就可以總是處於工作狀態,把時間浪費減到最少。亂序執行可以允許在發布指令3前發布指令4~8,而且這些指令的執行結果可以在指令3引出後立即引出(按序引出對X86 CPU來說是必需的),實際解碼率又會增加25%。不過PⅡ和K6從亂序執行中得到的好處有限,因為如果CPU遇到指令依賴情況,它必須找到更多的非依賴指令進行發布。

WinChip的性能表現看到一個帶有大容量一級Cache的按序執行CPU能夠同亂序執行CPU競爭,在時鐘周期方面,Cache未命中的代價是非常高昂的。帶有大容量一級Cache的按序執行CPU性能,比只有較小容量Cache亂序執行CPU的性能要強。

而Rise的工程師在這方面犯了錯誤,MP6的一級Cache只有16KB,因此Cache未命中的發生頻率比其他CPU高,以致於它很難“餵飽”它的3條流水線。這是很可惜的事,因為一個按序執行CPU不是太複雜,因此可以做得更小。如果Rise CPU具有較大的一級Cache和高時鐘頻率,那么,對於像K6-2那樣的亂序執行CPU來說,Rise CPU是一個兇狠的對手,它具有更好的浮點性能(雙FPU流水線),而且成本也更便宜。集成256KB二級Cache的mP6-Ⅱ或許將糾正這個錯誤,但它要達到令人滿意的時鐘頻率。

由於K7採用大容量緩衝,因此它能及時發布足夠多的非依賴性指令。大容量一級Cache、大容量緩衝和亂序執行,使K7的兩條FPU流水線比Rise mP6的兩條流水線更容易“餵飽”,效率更高。

歷史

從有序技術到亂序技術

直到大約1993年前,大多數CPU一次只能處理一條指令。那時,如果採用流水線設計,譬如摩托羅拉68040或者英特爾80486,那么可以同時在不同執行階段處理不同的指令。

到了1991年和1992年,出現了MIPS R4000、Alpha 21064和奔騰這些處理器,它們屬於面向通用市場的第一批“超標量”處理器:每個CPU周期可以處理(讀取、執行及退出)兩條指令。

後來,1995年出現了Alpha 21264,就有了每個周期能處理四條指令的第一個CPU,時鐘頻率達到300MHz,這個速度在當時十分驚人。Alpha21664在微處理器論壇上一亮相,就引來了台下觀眾的一片讚嘆,其中包括英特爾和IBM的設計者,更不用說Sun SPARC的設計者了。遺憾的是,Alpha最後沒有成功。

不管怎樣,這些廠商當時都採用了有條不紊的有序執行技術(In Order):程式指令在執行時,按順序讀取、執行及引退操作碼,每次執行兩條或者四條指令。

不同指令需要不同的執行資源,而且程式流程往往是這樣:執行需要等資源被釋放出來,或者指令依賴性(dependency)得到解決,才能繼續執行下一條指令。更糟的是,每出現新一代CPU,就需要重新編譯代碼,針對新CPU進行最佳化,不然讀/寫指令之間很可能會出現太多氣泡(bubble)即空閒時間,導致性能提升幅度不大,與競爭產品相比優勢也不大。

這時候,亂序執行(out of order execution)出場了。CPU硬體本身在讀取指令後重新安排指令的執行順序,根據現有資源情況,提供更多的執行單元、重新命名暫存器、處理好指令依賴性等等。所以,Pentium Pro和Alpha 21264之後的幾乎所有新款CPU都是採用無序執行技術。

在多數情況下,亂序執行可以加快晶片的運行速度,有時候加速明顯。21264的速度就是21164的將近兩倍,而Pentium Pro的速度也比奔騰快了一大截。經過重大改進的最新MIPS架構R10000也採用了亂序執行。

從安騰到Power6

亂序執行一直發展良好,直到後來英特爾推出了一種全新的技術。意義重大的安騰處理器擁有真正獨一無二的引擎,並使用了重要的顯式並行指令計算(EPIC)技術。先不說安騰處理器的超過100種的指令格式組合、龐大的慢速暫存器組等,它實際上重新採用了有序執行技術。所以,編譯器不得不完成所有工作,以確保執行單元始終處於忙碌狀態。除了浮點處理密集型套用外,要做到這一點並非易事,只要看看安騰系統的基準測試結果就會明白。

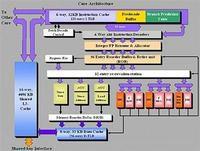

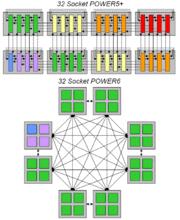

POWER5+ and POWER6

POWER5+ and POWER6在後續的發展中,安騰架構的這一做法從來沒有變過。相反,Sun一度改用了富士通公司使用無序技術的SPARC64,而不是它自己的使用有序技術的UltraSPARC IV。其他的重要架構如x86則繼續採用無序技術,使用了Core 2和K10等新引擎,並進一步改進了這種方案,以便充分利用每MHz。

如果出於某種原因需要AIX,那么Power的重要性就不言而喻了。Power4和Power5都是高速、但複雜的採用亂序技術的RISC處理器,它結合了四路超標量執行機制和非常高的系統頻寬。不過,Power6卻回到了有序技術時代。原因何在?

一個答案就是,如果Power6的同步多執行緒效果好,那么對單一執行緒浪費執行資源就不用太擔心:在這種情況下,只要同步運行兩個執行緒就行。另外,為了進一步大幅提升性能,頻率提高一倍、二級高速快取增加一倍、縮短算術邏輯單元(ALU)的延遲等方面恐怕更關鍵。即使那樣,浮點處理部件還會保留有一定的亂序執行功能——這是在通用處理器的浮點運算部分首次引入十進制浮點處理單元(FPU)。“同步雙執行緒執行、負荷預測機制以及增強的數據和指令預取功能,提升了有序執行超標量核心的性能。”IBM是這么評價其新晶片的。

Power5+的五路無序執行被Power6的七路有序執行所取代,但即使如此,也有幾個地方需要注意:Power5+一個執行緒每個周期最多只有五條指令,而Power6一個執行緒增加了二條指令,這對計算型執行緒和記憶體搜尋型執行緒組合來說更有優勢。Power5+更關注內部資源,而Power6在大部分時候等待記憶體,所以每個周期兩次操作完全夠了。那么性能方面有什麼提升呢?看一下基準測試specfp2006,頻率為2.2GHz的Power5+在這方面能達到14.9,當然是在經過改動的Power5機器上實現的;而頻率為4.7GHz的Power6能達到22.3,時鐘頻率提高了一倍多,性能提升卻不到一半。

所以,Power6的7.9億個電晶體分布在尺寸比較大的341平方毫米上,超過了Barcelona/Agena的283平方毫米,僅比尺寸龐大的安騰小了一點,它確實大幅提升了性能,儘管沒有了亂序技術。雖然高速快取和記憶體頻寬隨著時鐘頻率的提高都水漲船高,但是仍然可以說,在時鐘頻率相同情況下,重新使用有序技術會在處理單執行緒任務時導致性能下降30%左右。

為此,不得不等待更新的Power6系統以及下一版本AIX在編譯器方面的進展,以減少這種性能損耗。不過對Power6來說,採用有序技術確實明顯提升了處理器的性能。安騰同樣採用了有序技術,但是至少到現在還沒有看到明顯的成效。x86恐怕再也不會出現有序技術。

不過,處理器技術的發展一日千里,Power6設計者不會坐井觀天。英特爾公司的3.6GHz的Harpertown”Penryn“和AMD公司3GHz Barcelona處理器就會陸續面世,都會對IBM Power6構成重大挑戰。IBM必須牢記: 對採用有序技術的這類處理器而言,隨著每一代後續CPU的問世,在編譯器方面需要做的工作更多。同時,並不是每個人都會有時間重新編譯自己的應用程式。

亂序執行技術與順序執行技術

簡介

未來主流的計算市場(台式機、伺服器和筆記本電腦)需要的是有限多核架構,更加強調核的單執行緒性能,而很多核架構(數十甚至上百個核心)則將套用於流計算、HPC和SoC等特殊計算環境。這也將成為未來英特爾處理器的一個分水嶺,於是就有了所謂“大核”和“小核”處理器之分。前者以目前的酷睿架構為發展基準,追求更好的單執行緒性能; 後者則以凌動(Atom)核心為基礎,在設計上強調更高的並行度和更低的功耗。

在指令執行方面,“大核”採用的是亂序執行(out-of-order execution)模式,而“小核”則採用順序執行(In-order execution)模式。與順序執行相對應的亂序執行,是指CPU允許將多條指令不按程式規定的順序分開發送給各相應電路單元處理的技術。

對比

與順序執行技術相比,亂序執行能夠更有效地提高IPC,即提高每個時鐘頻率能夠執行的指令數量。一般來說在同樣一個主頻周期當中,無序核執行指令數量要比有序核執行的數量更多,因而亂序執行架構的處理器單核的計算能力比較強。但亂序執行模式的處理器在電路設計上比較複雜,核的功耗也比較高,在手機和某些嵌入式套用需要絕對低功耗的場合較難達到其設計要求,因此凌動處理器很自然地就採用了順序執行模式。

未來,很多核處理器和有限多核處理器將並行發展,以共同滿足日益分化和複雜的計算環境的需求。而評價一款處理器好壞的標準也會更加複雜,可能既不是通過主頻甚至也不是IPC,而要根據其套用特性來具體判斷。

亂序執行技術與龍芯2F晶片

套用

龍芯處理器在工業控制、PC、筆記本、軍工方面已經有非常成熟的套用,其實在某種意義上說,國產晶片已經進入了主流市場。據王成江先生透露,有很多政府以及軍隊都在長期使用龍芯平台。

對比

曙光千兆防火牆採用的是龍芯2F晶片,它是64位的通用RISC處理器,採用90nm的CMOS工藝製造,完全兼容MIPS 64標準。龍芯2F是基於龍芯2E處理器的改進版本,於2007年研製成功。龍芯2F集成了高性能龍芯2號CPU核,四發射動態超標量結構,9-10 級超流水線,支持暫存器重命名、動態調度、轉移預測等亂序執行技術;龍芯2F在龍芯2E的基礎上提高了I/O性能和記憶體訪問頻寬,集成記憶體控制器,提升了數據吞吐的速度,為網路安全產品提供了比較好的平台。

亂序執行技術與英特爾E8400處理器

簡介

45納米英特爾酷睿2雙核處理器E8400可為嵌入式套用提供長達7年的生命周期支持。這款處理器同時還支持英特爾可信執行技術(Intel Trusted Execution Technology),以幫助客戶部署安全的嵌入式解決方案。

增強的多媒體性能

該款45納米處理器中引入了超級亂序執行引擎,能夠增強專為圖形和多媒體處理最佳化的英特爾SIMD流指令擴展(SSE)算法。超級亂序執行引擎能夠降低延遲,並在加快現有SSE指令運行速度的同時,顯著提升最新SSE4指令集的表現。開發人員可充分利用SSE4多媒體指令集,提升互動式客戶端或數字簽名等終端嵌入式套用內在的視頻編輯和編碼功能。

英特爾可信執行技術

英特爾可信執行技術是英特爾酷睿2雙核處理器E8400中的一項硬體延展技術,它將硬體數據安全性引入了嵌入式市場,使得雙核處理器成為了防務、政府、中型網路安全設備和零售套用的理想選擇。這項安全技術旨在保護虛擬化計算環境中的數據免遭軟體攻擊、病毒入侵及其它類型威脅。

亂序執行技術與Intel的Nehalem架構晶片

建立

Nehalem還是基本建立在酷睿微架構(Core Microarchitecture)的骨架上,外加增添了SMT、3層Cache、TLB和分支預測的等級化、IMC、QPI和支持DDR3、新增加SSE4.2指令等技術。比起從Pentium 4的NetBurst架構到酷睿微架構的較大變化來說,從酷睿微架到Nehalem架構的基本核心部分的變化則要小一些,因為Nehalem還是4指令寬度的解碼/重命名/撤銷。

原因

Nehalem的亂序引擎顯著的擴大了,除了性能原因,還有就是為了提供SMT,因為SMT需要資源共享。

和酷睿 2一樣,Nehalem的暫存器重命名表(register alias table,RAT)指明每一個結構暫存器(architectural register)要么進入重排序緩衝(Re-Order Buffer,ROB),要么是進入撤銷暫存器檔案(Retirement Register File,RRF,或翻譯為引退暫存器檔案),並且保持有絕大多數最近的推測值狀態(speculative state)。而RRF則保持有絕大多數最近的非推測狀態(non-speculative state)。RAT可以每周期重命名4個微操作,給每一個微操作在ROB中一個目的地暫存器(destination register)。被重命名的指令就讀取它們的源運算元並被傳送到通用架構的保留站(unified Reservation Station,RS,可以被各種指令類型使用)。

Nehalem的ROB(重排序緩衝)從96項增加到128項,RS(保留站)從32項增加到36項,它們都由兩個執行緒所共享,但是使用不同的策略。ROB是靜態分配給2個執行緒,使得2個執行緒在指令流里都可以預測得一樣遠。而RS則是競爭共享,基於各執行緒的需求。這是因為許多時候一個執行緒可能會中止,從記憶體等待運算元,而使用到很少的RS項。這樣就不如讓另一個更活躍的執行緒儘可能多地使用RS項。在RS中的指令當其所有運算元都準備好時,就被分配到執行單元去。

Nehalem的執行單元與酷睿 2相比,基本沒有大的改變,而且並不受SMT的影響,除了使用率更高之外。

亂序執行技術與威盛凌瓏(VIA Nano)處理器

簡介

威盛凌瓏(VIA Nano)處理器是威盛 x86 平台系列第一款 64 位的超標量亂序執行處理器,旨在激活傳統台式和筆記本 PC 市場,為廣為需求計算技術、娛樂和網路連線套用提供了真正優質性能。

威盛 C7系列處理器採用市場領先的節能科技,威盛凌瓏(VIA Nano)處理器系列在同一功耗範圍,把性能提高到原來的四倍,從而進一步提升了其每瓦性能值的領導地位。而與C7系列處理器相同的針腳兼容保證了OEM 和主機板商能更平順地實現二者的轉換,另外,也讓現有系統和主機板升級更易行。

威盛凌瓏(VIA Nano) 處理器系列

處理器名稱

型號

主頻

威盛 V4 前端匯流排

封裝

處理器製程

閒置功耗

VIA Nano

L2100

1.8GHz

800MHz

NanoBGA2

65nm

500mW

VIA Nano

L2200

1.6GHz

800MHz

NanoBGA2

65nm

100mW

VIA Nano

U2300

1.3+GHz

800MHz

NanoBGA2

65nm

100mW

VIA Nano

U2500

1.2GHz

800MHz

NanoBGA2

65nm

100mW

VIA Nano

U2400

1.0GHz

800MHz

NanoBGA2

65nm

100mW

關鍵架構性能

尺寸

威盛凌瓏(VIA Nano)處理器採用富士通先進的65納米處理器技術,實現了高性能和低功耗完美的融合。它進一步鞏固了威盛在處理器小型化的領導地位,通過超密集設計,實現了x86平台新一代更小型化設計和套用。

封裝尺寸:威盛凌瓏(VIA Nano)BGA2 封裝(21mm x 21mm)

核心尺寸:7.650mm x 8.275mm (63.3平方毫米)

64 位的超標量亂序執行的微體系結構

威盛凌瓏(VIA Nano)處理器支持完整 64 位指令集,具備宏融合 (Macro-Fusion),微融合 (micro-fusion)功能,和精密複雜的分支預測。進一步降低了處理器功耗,提升了其效能。

高性能計算和媒體處理

威盛凌瓏(VIA Nano)處理器支持高速、低功耗威盛V4 前端匯流排,最低為800 MHz,支持新的SSE指令、2個64KB L1 高速快取和1MB獨立L2 高速快取,具有 16路信道連線性能,實現了多媒體性能的一大飛躍。

特別值得一提的是,威盛凌瓏(VIA Nano)處理器在高性能浮點運算方面有了非常顯著的提升,使用了全新的浮點加法運算法則,大大降低了 x86處理器中的浮點延遲時間(the lowest floating-point add latency),同樣,浮點乘法器也擁有了最低的浮點延遲時間。

換句話說,這意味著威盛凌瓏(VIA Nano)處理器提供了出色的流暢播放藍光碟和其它高清視頻格式的性能,它能解碼的媒體流速度可以達到40Mbps ,此外它獨有的雙時鐘浮點單元(FPU)和 128 位的數據通路,提供了絕佳的遊戲體驗,提供了極順暢的 3D 圖片表現

下圖表明了威盛凌瓏(VIA Nano)處理器在計算方面優於廣受歡迎的 C7 處理器之處:

高級功耗和熱量管理

強勁的動態電源管理,包括支持新型“C6”電源狀態,PowerSaver科技,全新的電路設計和機制來管理晶片核心溫度,降低功耗提升了熱量管理水平。

通過處理器中的以上創新科技,威盛凌瓏(VIA Nano)處理器在擁有超標量結構,實現顯著的性能提升的同時,功耗卻能維持和之前的威盛 C7 系列 處理器一樣的範圍。

威盛 1.0 GHz 的凌瓏(VIA Nano) ULV 處理器的首樣產品最大的設計功耗(TDP)只有 5 瓦(空閒運行功耗只有100 毫瓦),而 1.8GHz 的威盛凌瓏(VIA Nano)處理器的功耗也只有 25.5 瓦(空閒運行功耗 500 毫瓦)。

威盛凌瓏(VIA Nano) 處理器計算性能雖增加,功耗仍維持不變,這進一步提升了每瓦性能值, 更始其成為業內每瓦性能值最佳的產品。

2007 上測試的性能總分

1.6GHz Celeron-M 的TDP(最大熱功耗) = 31瓦; 1.6GHz 威盛Nano 的TDP = 17 瓦

作業系統 = Windows Vista 企業版

可升級威盛 C7處理器:威盛凌瓏(VIA Nano)處理器與威盛 C7處理器家族產品針腳兼容,使 OEM 廠商和主機板廠商能平順的進行新架構的產品交替,能讓他們僅需透過單一主機板或系統設計,能擴展延伸到不同的市場領域中。

綠色科技:此外還完全符合 RoHS 標準和 WEEE 規則,產品無鹵素、無鉛,對保護環境和可持續計算科技大有裨益。

增強的威盛 PadLock安全引擎

威盛凌瓏(VIA Nano)處理器承繼了威盛處理器家族核心硬體加密加速器和安全特性,包括雙隨機數據生成器(RNG)、一個AES加密引擎、NX Bit 和一個處理 SHA-1/SHA-256 加密計算的安全混編引擎。

AMD Phenom Intel Core 2 Intel Atom VIA C7 VIA Nano

安全混編 No No No 完全 SHA-1 & SHA-256 完全 SHA-1 & SHA-256

緩衝區溢出 NX Bit NX Bit NX Bit NX Bit NX Bit

核心編密碼(On-Die Encryption) No No No 完全 AES 編/譯 acceleration RSA 加速 CBC, CFB-M, AC, CTR modes 25Gb/s 峰值 完全 AES 編/譯 acceleration RSA 加速CBC, CFB-M, AC, CTR modes 25Gb/s 峰值

隨機數字生成器(Random Number Generation) (RNG) No No No 2 個增強的硬體RNG ,Feeds輸出至SHA 引起的速度為 12Mb/s 2 個增強的硬體RNG ,Feeds輸出至SHA 引起的速度為 12Mb/s

巴塞隆納新特性解析:堆疊操作與亂序執行

起源

Intel最早的Pentium M處理器引入了一項名為“dedicated stack manager”(專注堆疊管理器)的新特性,正如其名字所暗示的一樣,專注堆疊管理器專門處理所有的X86堆疊操作(例如push, pop, call, return等)。它將這些伐數據集中處理而無需其他執行單元參與,這尤其簡化了CPU整數執行單元的工作,加快了整數執行單元的處理速度。

技術

AMD在Barcelona中也引入了類似的技術,AMD稱之為Sideband Stack Optimizer(邊帶堆疊最佳化器)。有了邊帶堆疊最佳化器,處理器中的伐指令不再需要經過3路編碼,也不再由整數執行單元處理,這加快了堆疊的處理速度,也同時加快了整數執行單元的處理速度。

在Intel Core微構架中一個重要改進是OOOE亂序執行:當裝載指令佇列發生等待時,處理器可以將佇列後方處於等待的指令優先裝載並執行,而不是一直等待到堵塞結束。平均而言,約30%的指令會發生一定時間的堵塞,這一亂序執行模式的引入,使新構架CPU性能有了明顯的提高。AMD的K8構架並不支持OOOE亂序執行指令,所以即使K8構架有優秀的內置記憶體控制器,也依然被對手的Core構架擊敗。正視這一技術上的落後,AMD在K8L構架的首款晶片Barcelona上及時改進為OOOE技術,這一改進必將為K8L構架的性能帶來極大的提高。

Barcelona將可以亂序執行指令,同樣也可以在前一指令尚未處理完成時,裝載並用空載單元處理下一指令,即使這兩條指令需要讀取不同的記憶體地址。Barcelona擁有3個地址生成單元,可以完成3個暫存指令每周期,而Core構架每周期只能執行1次-K8L構架的暫存速度要比Core構架強大3倍。

K8L構架中加入了新的SSE4指令擴展:SSEEXTRQ/INSERTQ指令和MOVNTSD/MOVNTSS指令。前者可以將多條指令合併為一條指令執行,後者用來計算流量暫存指令。Intel也會將在稍候發布的Penryn處理器中加入。