IIC簡介

即I2C,一種匯流排結構。

例如:記憶體中的SPD信息,通過IIC,與BX晶片組聯繫,IIC 存在於英特爾PIIX4結構體系中。

隨著大規模積體電路技術的發展,把CPU和一個單獨工作系統所必需的ROM、RAM、I/O連線埠、A/D、D/A等外圍電路集成在一個單片內而製成的單片機或微控制器愈來愈方便。目前,世界上許多公司生產單片機,品種很多。其中包括各種字長的CPU,各種容量的ROM、RAM以及功能各異的I/O接口電路等等,但是,單片機的品種規格仍然有限,所以只能選用某種單片機來進行擴展。擴展的方法有兩種:一種是並行匯流排,另一種是串列匯流排。由於串列匯流排的連線少,結構簡單,往往不用專門的母板和插座而直接用導線連線各個設備。因此,採用串列線可大大簡化系統的硬體設計。PHILIPS公司早在十幾年前就推出了I2C串列匯流排,利用該匯流排可實現多主機系統所需的裁決和高低速設備同步等功能。因此,這是一種高性能的串列匯流排。

飛利浦電子公司日前推出新型二選一I2C主選擇器,可以使兩個I2C主設備中的任何一個與共享資源連線,廣泛適用於從MP3播放器到伺服器等計算、通信和網路套用領域,從而使製造商和終端用戶從中獲益。PCA9541可以使兩個I2C主設備在互不連線的情況下與同一個從設備相連線,從而簡化了設計的複雜性。此外,新產品以單器件替代了I2C多個主設備套用中的多個晶片,有效節省了系統成本。

硬體結構

I2C串列匯流排一般有兩根信號線,一根是雙向的數據線SDA,另一根是時鐘線SCL。所有接到I2C匯流排設備上的串列數據SDA都接到匯流排的SDA上,各設備的時鐘線SCL接到匯流排的SCL上。

為了避免匯流排信號的混亂,要求各設備連線到匯流排的輸出端時必須是漏極開路(OD)輸出或集電極開路(OC)輸出。設備上的串列數據線SDA接口電路應該是雙向的,輸出電路用於向匯流排上傳送數據,輸入電路用於接收匯流排上的數據。而串列時鐘線也應是雙向的,作為控制匯流排數據傳送的主機,一方面要通過SCL輸出電路傳送時鐘信號,另一方面還要檢測匯流排上的SCL電平,以決定什麼時候傳送下一個時鐘脈衝電平;作為接受主機命令的從機,要按匯流排上的SCL信號發出或接收SDA上的信號,也可以向SCL線發出低電平信號以延長匯流排時鐘信號周期。匯流排空閒時,因各設備都是開漏輸出,上拉電阻Rp使SDA和SCL線都保持高電平。任一設備輸出的低電平都將使相應的匯流排信號線變低,也就是說:各設備的SDA是“與”關係,SCL也是“與”關係。

匯流排對設備接口電路的製造工藝和電平都沒有特殊的要求(NMOS、CMOS都可以兼容)。在I2C匯流排上的數據傳送率可高達每秒十萬位,高速方式時在每秒四十萬位以上。另外,匯流排上允許連線的設備數以其電容量不超過400pF為限。

匯流排的運行(數據傳輸)由主機控制。所謂主機是指啟動數據的傳送(發出啟動信號)、發出時鐘信號以及傳送結束時發出停止信號的設備,通常主機都是微處理器。被主機尋訪的設備稱為從機。為了進行通訊,每個接到I2C匯流排的設備都有一個唯一的地址,以便於主機尋訪。主機和從機的數據傳送,可以由主機傳送數據到從機,也可以由從機發到主機。凡是傳送數據到匯流排的設備稱為傳送器,從匯流排上接收數據的設備被稱為接受器。

I2C匯流排上允許連線多個微處理器以及各種外圍設備,如存儲器、LED及LCD驅動器、A/D及D/A轉換器等。為了保證數據可靠地傳送,任一時刻匯流排只能由某一台主機控制,各微處理器應該在匯流排空閒時傳送啟動數據,為了妥善解決多台微處理器同時傳送啟動數據的傳送(匯流排控制權)衝突,以及決定由哪一台微處理器控制匯流排的問題,I2C匯流排允許連線不同傳送速率的設備。多台設備之間時鐘信號的同步過程稱為同步化。

數據傳輸

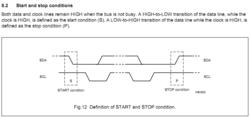

在I2C匯流排傳輸過程中,將兩種特定的情況定義為開始和停止條件(見圖3):當SCL保持“高”時,SDA由“高”變為“低”為開始條件;當SCL保持“高”且SDA由“低”變為“高”時為停止條件。開始和停止條件均由主控制器產生。使用硬體接口可以很容易地檢測到開始和停止條件,沒有這種接口的微機必須以每時鐘周期至少兩次對SDA取樣,以檢測這種變化。

開始和停止條件圖3

開始和停止條件圖3SDA線上的數據在時鐘“高”期間必須是穩定的,只有當SCL線上的時鐘信號為低時,數據線上的“高”或“低”狀態才可以改變。輸出到SDA線上的每個位元組必須是8位,每次傳輸的位元組不受限制,但每個位元組必須要有一個應答ACK。如果一接收器件在完成其他功能(如一內部中斷)前不能接收另一數據的完整位元組時,它可以保持時鐘線SCL為低,以促使傳送器進入等待狀態;當接收器準備好接受數據的其它位元組並釋放時鐘SCL後,數據傳輸繼續進行。I2C數據匯流排傳送時序如圖4所示。

數據傳送具有應答是必須的。與應答對應的時鐘脈衝由主控制器產生,傳送器在應答期間必須下拉SDA線。當定址的被控器件不能應答時,數據保持為高並使主控器產生停止條件而終止傳輸。在傳輸的過程中,在用到主控接收器的情況下,主控接收器必須發出一數據結束信號給被控傳送器,從而使被控傳送器釋放數據線,以允許主控器產生停止條件。合法的數據傳輸格式如下:

I2C匯流排在開始條件後的首位元組決定哪個被控器將被主控器選擇,例外的是“通用訪問”地址,它可以在所有期間定址。當主控器輸出一地址時,系統中的每一器件都將開始條件後的前7位地址和自己的地址進行比較。如果相同,該器件即認為自己被主控器定址,而作為被控接收器或被控傳送器則取決於R/W位。

套用

I2C匯流排是各種匯流排中使用信號線最少,並具有自動定址、多主機時鐘同步和仲裁等功能的匯流排。因此,使用I2C匯流排設計計算機系統十分方便靈活,體積也小,因而在各類實際套用中得到廣泛套用。下面舉二個套用示例。

I2C的運用比如在鐵電存儲器中,用鐵電存儲數據就是用的I2C匯流排協定。

伺服控制系統用I2C擴展LCD顯示器

圖5是一個伺服系統的結構圖。它用8XC752單片機的PWM輸出經放大後來驅動電機,電機的轉速由測速機測取並直接送到8XC752片內的A/D電路。處理後的有關信息經I2C匯流排送到LCD驅動晶片PCF8577以驅動64段LCD顯示板。

通用I/O連線埠作為I2C匯流排接口

目前,51、96系列的單片機套用很廣,但是由於它們都沒有I2C匯流排接口,從而限制了在這些系統中使用具有I2C匯流排接口的器件。通過對I2C匯流排時序的分析,可以用51單片機的兩根I/O線來實現I2C匯流排的功能。接I2C匯流排規定:SCL線和SDA線是各設備對應輸出狀態相“與”的結果,任一設備都可以用輸出低電平的方法來延長SCL的低電平時間,以迫使高速設備進入等待狀態,從而實現不同速度設備間的時鐘同步。因此,即使時鐘脈衝的高、低電平時間長短不一,也能實現數據的可靠傳送,可以用軟體控制I/O口做I2C接口。下面就是用GMS97C2051的通用I/O口來作為I2C匯流排接口,並由軟體控制實現數據傳送的例子,圖6為其連線圖。

在單主控器的系統中,時鐘線僅由主控器驅動,因此可以用51系列的一根I/O線作為SCL的信號線,將其設定為輸出方式,並由軟體控制來產生串列時鐘信號。在實際系統中使用了P1.3。另一根I/O線P1.2作為I2C匯流排的串列數據線,可在軟體控制下在時鐘的低電平期間讀取或輸出數據。系統傳輸數據的過程如下:先由單片機發出一個啟始數據信號,接著送出要訪問器件的7位地址數據,並等待被控器件的應答信號。當收到應答信號後,根據訪問要求進行相應的操作。如果是讀入數據,則數據線可一直設為輸入方式,中間不需要改變SDA線的工作方式,每讀入一個位元組均應依次檢測應答信號;如果是輸出數據,則首先將SDA設定為輸出方式,當傳送完一個位元組後,需要改變SDA線為輸入方式,此時讀入被控器件的應答信號就完成了一個位元組的傳送。當所有數據傳輸完畢後,應向SDA發出一個停止信號,以結束該次數據傳輸。

![iic[Inter-Integrated Circuit(積體電路匯流排)] iic[Inter-Integrated Circuit(積體電路匯流排)]](/img/d/4c4/nBnauM3X3QjNycTOyQTOzkDN1UTM1QDN5MjM5ADMwAjMwUzL0kzLyQzLt92YucmbvRWdo5Cd0FmL0E2LvoDc0RHa.jpg)