工作原理

原理

DMA方式

DMA方式DMA方式的主要優點是速度快。

由於CPU根本不參加傳送操作,因此就省去了CPU取指令、取數、送數等操作。在數據傳送過程中,沒有保存現場、恢復現場之類的工作。記憶體地址修改、傳送字個數的計數等等,也不是由軟體實現,而是用硬體線路直接實現的。所以DMA方式能滿足高速I/O設備的要求,也有利於CPU效率的發揮。

操作

實現DMA傳送的基本操作如下:

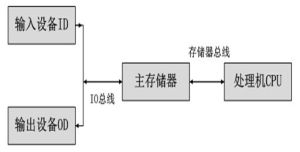

1、外設可通過DMA控制器向CPU發出DMA請求。

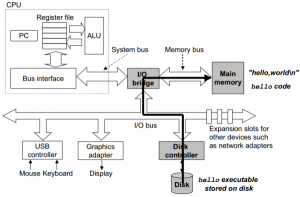

2、CPU回響DMA請求,系統轉變為DMA工作方式,並把匯流排控制權交給DMA控制器。

3、由DMA控制器傳送存儲器地址,並決定傳送數據塊的長度。

4、執行DMA傳送。

5、DMA操作結束,並把匯流排控制權交還CPU。

用途

DMA方式主要適用於一些高速的I/O設備。這些設備傳輸位元組或字的速度非常快。對於這類高速I/O設備,如果用輸入輸出指令或採用中斷的方法來傳輸位元組信息,會大量占用CPU的時間,同時也容易造成數據的丟失。而DMA方式能使I/O設備直接和存儲器進行成批數據的快速傳送。

DMA控制器或接口一般包括四個暫存器:

1:狀態控制暫存器。

2:數據暫存器。

3:地址暫存器。

4:位元組計數器。

這些暫存器在信息傳送之前需要進行初始化設定。即在輸入輸出程式中用彙編語言指令對各個暫存器寫入初始化控制字。

方式特點

DMA方式

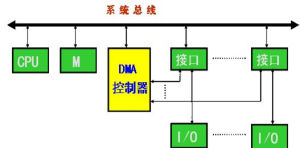

DMA方式DMA傳輸將一個記憶體區從一個裝置複製到另外一個,CPU初始化這個傳輸動作,傳輸動作本身是由DMA控制器來實行和完成。典型的例子就是移動一個外部記憶體的區塊到晶片內部更快的記憶體去。像是這樣的操作並沒有讓處理器工作拖延,反而可以被重新排程去處理其他的工作。DMA傳輸對於高效能嵌入式系統算法和網路是很重要的。

舉個例子,PC ISA DMA控制器擁有8個MA通道,其中的7個通道是可以讓PC的CPU所利用。每一個DMA通道有一個16位元位址暫存器和一個16位元計數暫存器。要初始化資料傳輸時,裝置驅動程式一起設定DMA通道的位址和計數暫存器,以及資料傳輸的方向,讀取或寫入。然後指示DMA硬體開始這個傳輸動作。當傳輸結束的時候,裝置就會以中斷的方式通知CPU。

但是,DMA傳輸方式只是減輕了CPU的工作負擔;系統匯流排仍然被占用。特別是在傳輸大容量檔案時,CPU的占用率可能不到10%,但是用戶會覺得運行部分程式時系統變得相當的緩慢。主要原因就是在運行這些套用程式(特別是一些大型軟體),操作系統也需要從系統匯流排傳輸大量數據;故造成過長的等待時間。

傳送方式

DMA方式

DMA方式(1)單元傳送方式(單位元組傳送方式)

單元傳送方式意味著每個DMA請求對應一對DMA讀/寫周期,即1個單元讀,然後1個單元寫。

(2)塊傳送方式(連續傳送方式)

塊傳送方式意味著在連續4個字的DMA寫周期前有連續的4個字的DMA讀周期,即4個字突發讀,然後4個字突發寫,因此傳輸的數據個數應該是16位元組的倍數。

如果傳送大小或者DMA計數值不是16的倍數,則DMA將不能完整地傳送完數據。假設要傳送的數據為50個位元組,則3*16=48位元組,會導致2個位元組不能被傳送,DMA在傳送48個位元組後停止。所以,選擇DMA塊傳送方式時,一定要注意這一點。

(3)on-the-fly傳送方式(請求傳送方式)

在on-the-fly傳送方式下DMA讀/寫可以同時進行。DMA應答信號通知外部設備去讀或者寫。同時,存儲控制器將產生與讀/寫相關的控制信號給外部存儲器。如果外部設備能夠支持on-the-fly傳送方式,將會使得外設的數據傳輸速率大大地增加。

停止CPU訪問記憶體

當外圍設備要求傳送一批數據時,由DMA控制器發一個停止信號給CPU,要求CPU放棄對地址匯流排、數據匯流排和有關控制匯流排的使用權。DMA控制器獲得匯流排控制權以後,開始進行數據傳送。在一批數據傳送完畢後,DMA控制器通知CPU可以使用記憶體,並把匯流排控制權交還給CPU。在這種DMA傳送過程中,CPU基本處於不工作狀態或者說保持狀態。

優點:控制簡單,它適用於數據傳輸率很高的設備進行成組傳送。

缺點:在DMA控制器訪內階段,記憶體的效能沒有充分發揮,相當一部分記憶體工作周期是空閒的。這是因為,外圍設備傳送兩個數據之間的間隔一般總是大於記憶體存儲周期,即使高速I/O設備也是如此。

周期挪用

當I/O設備沒有DMA請求時,CPU按程式要求訪問記憶體;一旦I/O設備有DMA請求,則由I/O設備挪用一個或幾個記憶體周期。

I/O設備要求DMA傳送時可能遇到兩種情況:

(1)此時CPU不需要訪內,如CPU正在執行乘法指令。由於乘法指令執行時間較長,此時I/O訪內與CPU訪內沒有衝突,即I/O設備挪用一二個記憶體周期對CPU執行程式沒有任何影響。

(2)I/O設備要求訪內時CPU也要求訪內,這就產生了訪內衝突,在這種情況下I/O設備訪內優先,因為I/O訪內有時間要求,前一個I/O數據必須在下一個訪內請求到來之前存取完畢。顯然,在這種情況下I/O設備挪用一二個記憶體周期,意味著CPU延緩了對指令的執行,或者更明確地說,在CPU執行訪內指令的過程中插入DMA請求,挪用了一二個記憶體周期。

與停止CPU訪內的DMA方法比較,周期挪用的方法既實現了I/O傳送,又較好地發揮了記憶體和CPU的效率,是一種廣泛採用的方法。但是I/O設備每一次周期挪用都有申請匯流排控制權、建立匯流排控制權和歸還匯流排控制權的過程,所以傳送一個字對記憶體來說要占用一個周期,但對DMA控制器來說一般要2—5個記憶體周期(視邏輯線路的延遲而定)。因此,周期挪用的方法適用於I/O設備讀寫周期大於記憶體存儲周期的情況。

DMA與CPU交替訪內

如果CPU的工作周期比記憶體存取周期長很多,此時採用交替訪內的方法可以使DMA傳送和CPU同時發揮最高的效率。假設CPU工作周期為1.2μs,記憶體存取周期小於0.6μs,那么一個CPU周期可分為C1和C2兩個分周期,其中C1供DMA控制器訪內,C2專供CPU訪內。

這種方式不需要匯流排使用權的申請、建立和歸還過程,匯流排使用權是通過C1和C2分時進行的。CPU和DMA控制器各自有自己的訪內地址暫存器、數據暫存器和讀/寫信號等控制暫存器。在C1周期中,如果DMA控制器有訪內請求,可將地址、數據等信號送到匯流排上。在C2周期中,如CPU有訪內請求,同樣傳送地址、數據等信號。事實上,對於匯流排,這是用C1,C2控制的一個多路轉換器,這種匯流排控制權的轉移幾乎不需要什麼時間,所以對DMA傳送來講效率是很高的。

這種傳送方式又稱為“透明的DMA”方式,其來由是這種DMA傳送對CPU來說,如同透明的玻璃一般,沒有任何感覺或影響。在透明的DMA方式下工作,CPU既不停止主程式的運行,也不進入等待狀態,是一種高效率的工作方式。當然,相應的硬體邏輯也就更加複雜。

工作過程

預處理階段

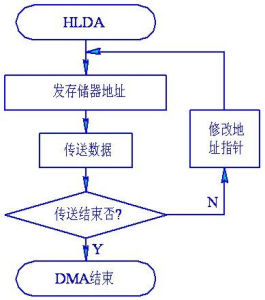

DMA方式

DMA方式外部設備準備好傳送的數據(輸入)或上次接收的數據已處理完畢(輸出)時,將通知DMA控制器發出DMA請求,申請主存匯流排。

①.首先從外部設備讀入一個字(設每字16位)到DMA數據緩衝暫存器IODR中(如果設備是面向位元組的,一次讀入一個位元組,需要將兩個位元組裝配成一個字)。

②.外部設備發選通脈衝,使DMA控制器中的DMA請求標誌觸發器置“1”。

③.DMA控制器向CPU發出匯流排請求信號(HOLD)。

④.CPU在完成了現行機器周期後,即回響DMA請求,發出匯流排允許信號(HLDA),並由DMA控制器發出DMA回響信號,使DMA請求標記觸發器復位。此時,由DMA控制器接管系統匯流排。

⑤.將DMA控制器中主存地址暫存器中的主存地址送地址匯流排。

⑥.將DMA數據緩衝暫存器中的內容送數據匯流排。

⑦.在讀/寫控制信號線上發出寫命令。

⑧.將DMA地址暫存器的內容加1,從而得到下一個地址,字計數器減1。

⑨.判斷字計數器的值是否為“0”。若不為“0”,說明數據塊沒有傳送完畢,返回⑤,傳送下一個數據;若為“0”,說明數據塊已經傳送完畢,則向CPU申請中斷處理。

輸出操作

①.當DMA數據緩衝暫存器已將輸出數據送至I/O設備後,表示數據緩衝暫存器為“空”。

②.外部設備發選通脈衝,使DMA控制器中的DMA請求標誌觸發器置“1”。

③.DMA控制器向CPU發出匯流排請求信號(HOLD)。

④.CPU在完成了現行機器周期後,即回響DMA請求,發出匯流排允許信號(HLDA),並由DMA控制器發出DMA回響信號,使DMA請求標記觸發器復位。此時,由DMA控制器接管系統匯流排。

⑤.將DMA控制器中主存地址暫存器中的主存地址送地址匯流排,在讀/寫控制信號線上發出讀命令。

⑥.主存將相應地址單元的內容通過數據匯流排讀入到DMA數據緩衝暫存器中。

⑦.將DMA數據緩衝暫存器的內容送到輸出設備。

⑧.將DMA地址暫存器的內容加1,從而得到下一個地址,字計數器減1。

⑨.判斷字計數器的值是否為“0”。若不為“0”,說明數據塊沒有傳送完畢,返回到⑤,傳送下一個數據;若為“0”,說明數據塊已經傳送完畢,則向CPU申請中斷處理。

傳送後處理

校驗送入主存的數據是否正確。

決定是否繼續用DMA傳送其他數據塊。

測試在傳送過程中是否發生錯誤。