細節

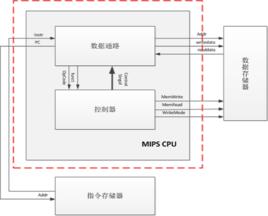

CPU設計關注

數據路徑(如ALU和計算管道)

控制單元:邏輯控制的數據路徑

記憶體元件,如暫存器檔案快取

時脈電路,如時脈驅動器,PLL,時鐘分配網路

墊收發器電路

邏輯門電路的實現

1.數據路徑(如ALU和計算管道)

2.控制單元:邏輯控制的數據路徑

3.記憶體元件,如暫存器檔案快取

4.時脈電路,如時脈驅動器,PLL,時鐘分配網路

5.墊收發器電路

6.邏輯門電路的實現

定製設計

CPU為高性能需求設計,可能需要為每個項目的定製設計以實現變頻。

為性能較低的需求設計的CPU可能實施:

1.購買一些智慧財產權

2.使用控制邏輯的實現技術(使用CAD工具等)來實現其他組成部分.

CPU架構設計的邏輯

在CPU設計中包括的一般邏輯為:

1.非結構化的隨機邏輯

2.有限狀態機

3.微程式設計(常見於1965年到1985年)

4.可程式邏輯陣列(常見於80年代,現在比較罕見)

用來實現邏輯設備類型包括

1.TTL小規模集成邏輯晶片 - 已不被使用

2.可程式陣列邏輯和可程式邏輯器件- 已不被使用

3.射極耦合邏輯(ECL)門陣列- 已不普遍

4.CMOS門陣列- 已不被使用

5.CMOSASICs - 今天常用,它們非常常用以致單詞ASIC並不用於CPU

6.現場可程式邏輯門陣列(FPGA) - 常見於軟微處理器,多少需要可重構計算

CPU設計計畫大致上有這些主要工作

1.程式設計師可見指令集, 各種微架構的實現

2.在ANSI C/C++或者SystemC的體系研究和性能建模

3.高級綜合(HLS) 或RTL(例如邏輯) 執行

4.關鍵速度相關部件(快取、暫存器、算數邏輯單元)電路設計

5.邏輯綜合或邏輯門層設計

6.進行時序分析以確認所有邏輯和電路將以特定頻率運行

7.物理設計,包括布局、布線、版圖設計

8.檢查 RTL,邏輯門層,電晶體層及物理層表示相符

9.檢查信號完整性,晶片可製造性

通過重新設計CPU核心,來獲得更小的裸片面積,有助於實現以上目標中的幾個。

市場情況

研發新的、高端的CPU是一個代價沉重的命題,例如,一般的電腦工程師年薪在每年25萬美元左右。 這包括工資、福利、CAD工具、電腦、辦公場地租金等。假設設計CPU需要100名工程師,那么該項目需要4年。

總支出 = $25萬 / 工程師數/年 x 100 工程師數 x 4 年 = $1億美元。

上述金額只是一個例子.現代通用CPU的設計團隊有幾百個團隊成員。

嵌入式處理器經濟

出貨量最大的嵌入式CPU系列是8051,平均每年有近10億個單位。8051被廣泛使用,因為它非常便宜。現在設計時間大致為零,因為它作為商業智慧財產權被廣泛使用。現在它通常作為晶片上較大系統的一小部分嵌入。8051的矽片成本現在低至0.001美元,因為有些實現使用的邏輯門數少至2,200個,而矽片數量為0.0127平方毫米。

截至2009年,使用ARM架構指令集生成的CPU數量超過了其他32位指令集。ARM架構和第一個ARM晶片的設計大約需要一年半的時間和5年的工作時間。

32位Parallax Propeller微控制器架構和第一個晶片是由兩個人在大約10年的工作時間內設計的。

8位AVR架構和第一款AVR微控制器由挪威理工學院的兩名學生構思和設計。

8位6502架構和第一個MOS技術6502晶片是在13個月內由大約9人設計的。

研究和教育CPU設計

32位Berkeley RISCI和RISC II架構和第一批晶片主要由一系列學生設計,作為四季度研究生課程式列的一部分。這種設計成為商業SPARC處理器設計的基礎。

大約十年之後,每個參加麻省理工學院6.004課程的學生都是團隊的一部分 - 每個團隊都有一個學期在7400系列積體電路中設計和構建一個簡單的8位CPU。一個由4名學生組成的團隊在該學期中設計並構建了一個簡單的32位CPU。

有些本科課程要求由2至5名學生組成的團隊在一個15周的學期內在FPGA中設計,實施和測試一個簡單的CPU。

MultiTitan CPU的設計經過了2.5年的努力,當時被認為是“相對較少的設計工作”。24人參與了3.5年的MultiTitan研究項目,其中包括設計和構建原型CPU。

軟微處理器核心

對於嵌入式系統,由於功耗要求,通常不需要或不需要最高性能級別。這允許使用可以完全由邏輯綜合技術實現的處理器。這些綜合處理器可以在更短的時間內實施,從而縮短產品上市時間。