基本功能

非門

非門實現邏輯代數非的功能,即輸出始終和輸入保持相反。當輸入端為高電平(邏輯“1”)時,輸出端為低電平(邏輯“0”);反之,當輸入端為低電平(邏輯“0”)時,輸出端則為高電平(邏輯“1”) 。非門的數學邏輯表達式為:F= ,其真值表如下所示 :

| 輸入A | 輸出Y |

| 0 | 1 |

| 1 | 0 |

邏輯符號

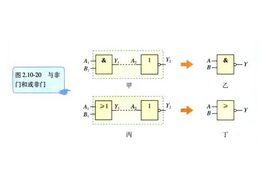

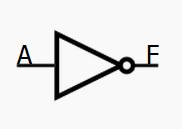

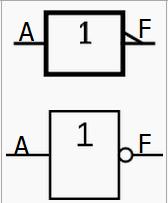

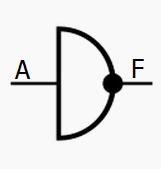

非門共有3種邏輯符號:形狀特徵型符號(ANSI/IEEEStd 91-1984)、IEC矩形國標符號(IEC 60617-12)和DIN符號(DIN 40700),分別如下圖所示:

非門 非門 |  非門 非門 |  非門 非門 |

| 形狀特徵型符號(ANSI/IEEEStd 91-1984) | IEC矩形國標符號(IEC 60617-12) | DIN符號(DIN 40700) |

實現

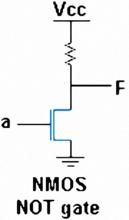

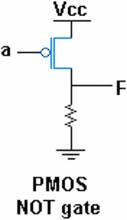

非門(反相器)通常採用CMOS邏輯和TTL邏輯,也可以通過NMOS邏輯、PMOS邏輯等來實現。

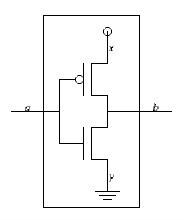

非門 非門 |  非門 非門 |  非門 非門 |

| CMOS反相器 | NMOS反相器 | PMOS反相器 |

CMOS邏輯:

兩管的柵極相連作為輸入端,兩管的漏極相連作為輸出端。TN的源極接地,TP的源極接電源。為了保證電路正常工作, VDD需要大於TN管開啟電壓 VTN和TP管開啟電壓 VTP的絕對值的和,即 UDD> UTN+ | UTP|。當 Ui=0V時,TN截止,TP導通, Uo≈ UDD為高電平;當 Ui= UDD時,TN導通,TP截止, Uo≈0V為低電平。因此實現了邏輯非的功能。

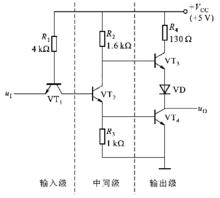

TTL邏輯:

TTL反相器由三部分組成,包括輸入級、倒相級、輸出級組成 。由於輸入和輸出均為三極體結構,因此也成為三極體-三極體邏輯電路。其結構如圖所示。

非門 非門 |

| TTL反相器 |

積體電路

非門是基本的邏輯門,因此在TTL和CMOS積體電路中都是可以使用的。標準的積體電路有74X04和CD4049。74X04TTL晶片有14個引腳,4049CMOS晶片有16個引腳,兩種晶片都各有2個引腳用於電源供電/基準電壓,12個引腳用於6個反相器的輸入和輸出(4049有2個引腳懸空)。

在數字電路中最具代表性的CMOS非門積體電路是CD4069。