這是製作MOS大規模積體電路的一種重要工藝技術。採用該技術即可減小其中MOSFET的寄生電容,大大提高工作頻率和速度。

(1)問題的提出:

對於增強型MOSFET,如果柵電極與源/漏區域之間存在有間隙的話,則器件工作時溝道就不能導通,因此在早期的鋁柵電極MOSFET結構中,考慮到工藝對準的誤差,往往在柵電極與源/漏區域之間設定了一定的重疊覆蓋的部分;但是,假若此重疊部分過大、使得柵-源之間和柵-漏之間的寄生電容增大的話,那就會導致器件的高頻特性變壞(特別,柵-漏之間的寄生電容是密勒電容,影響更大)。所以,為了使器件能夠導通,而又不致使器件的高頻特性劣化,就要求柵-源之間或柵-漏之間的重疊部分儘量的小,即達到高精度的對準。自對準技術就是能實現這種目的的一種有用的技術。

(2)工藝舉例:

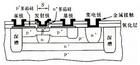

自對準技術與常規技術的工藝步驟完全不同,在常規的MOS技術中是先製作源、漏極,然後再製作柵極;但是自對準技術則是先製作柵極,然後再製作源、漏極。在自對準技術中,實際上就是利用柵極本身作為掩模來進行n源區和漏區的離子注入,使得其間的重疊部分幾乎減小到了0;能夠用作為自對準技術的柵極材料,必須要使用耐熱性好的多晶矽薄膜才行,因為在注入約10cm的P或As離子後還需要在800C~1000C下進行熱處理,這對於Al柵材料是不行的。在用離子注入自對準形成n源區和漏區的同時,也往多晶矽柵極薄膜中注入了P或As離子,這也有效地降低了多晶矽柵極的電阻(熱處理後方塊電阻可低至30Ω/□)。

當然,在某些特殊場合,也有採用不同於這裡所講的自對準技術。