簡介

隨著現代科技的發展,人們的生活已經離不開數字電路。計算機邏輯電路是指數字電路中最基本的邏輯元件,它能按照一定的條件去控制信號的通過或不通過。基本邏輯關係為“與”、“或”、“非”三種。

計算機邏輯電路是一種離散信號的傳遞和處理,以二進制為原理、實現數位訊號邏輯運算和操作的電路。分組合邏輯電路和時序邏輯電路。前者由最基本的“與門”電路、“或門”電路和“非門”電路組成,其輸出值僅依賴於其輸入變數的當前值,與輸入變數的過去值無關—即不具記憶和存儲功能;後者也由上述基本邏輯門電路組成,但存在反饋迴路—它的輸出值不僅依賴於輸入變數的當前值,也依賴於輸入變數的過去值。由於只分高、低電平,抗干擾力強,精度和保密性佳 。

分類

邏輯電路是數字電路中最基本的邏輯元件。所謂門就是一種開關,它能按照一定的條件去控制信號的通過或不通過。電路的輸入和輸出之間存在一定的邏輯關係(因果關係),所以邏輯電路又稱為邏輯門電路。基本邏輯關係為“與”、“或”、“非”三種。邏輯門電路按其內部有源器件的不同可以分為三大類。第一類為雙極型電晶體邏輯門電路,包括TTL、ECL電路和I2L電路等幾種類型;第二類為單極型MOS邏輯門電路,包括NMOS、PMOS、LDMOS、VDMOS、VVMOS、IGT等幾種類型;第三類則是二者的組合BICMOS門電路。常用的是CMOS邏輯門電路。下面選擇幾種介紹。

TTL電路

TTL全稱Transistor-Transistor Logic,即BJT-BJT邏輯門電路,是數字電子技術中常用的一種邏輯門電路,套用較早,技術已比較成熟。TTL主要有BJT(Bipolar Junction Transistor 即雙極結型電晶體,晶體三極體)和電阻構成,具有速度快的特點。最早的TTL門電路是74系列,後來出現了74H系列,74L系列,74LS,74AS,74ALS等系列。但是由於TTL功耗大等缺點,正逐漸被CMOS電路取代。 TTL門電路有74(商用)和54(軍用)兩個系列,每個系列又有若干個子系列。TTL電平信號被利用的最多是因為通常數據表示採用二進制規定,+5V等價於邏輯“1”,0V等價於邏輯“0”,這被稱做TTL(電晶體-電晶體邏輯電平)信號系統,這是計算機處理器控制的設備內部各部分之間通信的標準技術。

TTL電平信號對於計算機處理器控制的設備內部的數據傳輸是很理想的,首先計算機處理器控制的設備內部的數據傳輸對於電源的要求不高以及熱損耗也較低,另外TTL電平信號直接與積體電路連線而不需要價格昂貴的線路驅動器以及接收器電路;再者,計算機處理器控制的設備內部的數據傳輸是在高速下進行的,而TTL接口的操作恰能滿足這個要求。TTL型通信大多數情況下,是採用並行數據傳輸方式,而並行數據傳輸對於超過10英尺的距離就不適合了。這是由於可靠性和成本兩面的原因。因為在並行接口中存在著偏相和不對稱的問題,這些問題對可靠性均有影響。

在超大規模積體電路出現之前,TTL積體電路是構造微型機和主機處理器的標準方法。其原因如下:首先計算機處理器控制的設備內部的數據傳輸對於電源的要求不高以及熱損耗也較低;其次TTL電平信號直接與積體電路連線而不需要價格昂貴的線路驅動器以及接收器電路;再者,計算機處理器控制的設備內部的數據傳輸是在高速下進行的,而TTL接口的操作恰能滿足這個要求。

CMOS電路

CMOS是單詞的首字母縮寫,是互補的金屬氧化物半導體(Complementary Metal-OxideSemiconductor),它指的是一種特殊類型的電子積體電路(IC)。簡單的CMOS反相器的開關模型是由一對互補的場效應管組成,原理圖如下圖所示,一個P型場效應管接電源正極,一個N型場效應管接地。當輸入為高電平時,N型場效應管導通,輸出便為低電平。當輸入是低電平時,電路通過P型場效應管導通,輸出為高電平。CMOS邏輯通過最簡單的反相器從而構造出邏輯關係中與門,或門電路。

特點有以下幾點:

1、功耗低:CMOS積體電路採用場效應管,且都是互補結構,工作時兩個串聯的場效應管總是 處於一個管導通另一個管截止的狀態,電路靜態功耗理論上為零。實際上,由於存在漏電流, CMOS電路尚有微量靜態功耗。單個門電路的功耗典型值僅為20mW,動態功耗(在1MHz工作 頻率時)也僅為幾mW 工作電壓範圍寬:CMOS積體電路供電簡單,供電電源體積小,基本上不需穩壓。國產CC4000 系列的積體電路,可在3~18V電壓下正常工作。

2、邏輯擺幅大:CMOS積體電路的邏輯高電平"1"、邏輯低電平"0"分別接近於電源高電位VDD及電源低電位VSS。當VDD=15V,VSS=0V時,輸出邏輯擺幅近似15V。因此,CMOS積體電路的電壓利用係數在各類積體電路中指標是較高的。 抗干擾能力強:CMOS積體電路的電壓噪聲容限的典型值為電源電壓的45%,保證值為電源電壓的30%。隨著電源電壓的增加,噪聲容限電壓的絕對值將成比例增加。對於VDD=15V的供電電壓(當VSS=0V時),電路將有7V左右的噪聲容限。

3、輸入阻抗高:CMOS積體電路的輸入端一般都是由保護二極體和串聯電阻構成的保護網路,故比一般場效應管的輸入電阻稍小,但在正常工作電壓範圍內,這些保護二極體均處於反向偏置狀態,直流輸入阻抗取決於這些二極體的泄露電流,通常情況下,等效輸入阻抗高達103~1011Ω,因此CMOS積體電路幾乎不消耗驅動電路的功率。

4、溫度穩定性能好:由於CMOS積體電路的功耗很低,內部發熱量少,而且,CMOS電路線路結構和電氣參數都具有對稱性,在溫度環境發生變化時,某些參數能起到自動補償作用,因而CMOS積體電路的溫度特性非常好。一般陶瓷金屬封裝的電路,工作溫度為-55 ~ +125℃;塑膠封裝的電路工作溫度範圍為-45 ~ +85℃。

5、扇出能力強:扇出能力是用電路輸出端所能帶動的輸入端數來表示的。由於CMOS積體電路的輸入阻抗極高,因此電路的輸出能力受輸入電容的限制,但是,當CMOS積體電路用來驅動同類型,如不考慮速度,一般可以驅動50個以上的輸入端。

6、抗輻射能力強:CMOS積體電路中的基本器件是MOS電晶體,屬於多數載流子導電器件。各種射線、輻射對其導電性能的影響都有限,因而特別適用於製作航天及核實驗設備。 可控性好:CMOS積體電路輸出波形的上升和下降時間可以控制,其輸出的上升和下降時間的典型值為電路傳輸延遲時間的125%~140%。

7、接口方便:因為CMOS積體電路的輸入阻抗高和輸出擺幅大,所以易於被其他電路所驅動,也容易驅動其他類型的電路或器件。

雖然製造積體電路的方法有多種,但對於數字邏輯電路而言CMOS是主要的方法。桌面個人計算機、工作站、視頻遊戲以及其它成千上萬的其它產品都依賴於CMOS積體電路來完成所需的功能。當我們注意到所有的個人計算機都使用專門的CMOS晶片,如眾所周知的微處理器,來獲得計算性能時,CMOS的重要性就不言而喻了。

ECL電路

ECL(Emitter Coupled Logic)即發射極耦合邏輯電路,也稱電流開關型邏輯電路。它是利用運放原理通過電晶體射極耦合實現的門電路。在所有數字電路中,它工作速度最高,其平均延遲時間tpd可小至1ns。ECL電路是由一個差分對管和一對射隨器組成的,所以輸入阻抗大,輸出阻抗小,驅動能力強,信號檢測能力高,差分輸出,抗共模干擾能力強。但是由於單元門的開關管對是輪流導通的,對整個電路來講沒有“截止”狀態,所以電路的功耗較大。

基本邏輯

簡單的邏輯電路通常是由門電路構成,也可以用三極體來製作,例如,一個NPN三極體的集電極和另一個NPN三極體的發射極連線,這就可以看作是一個簡單的與門電路,即:當兩個三極體的基極都接高電平的時候,電路導通,而只要有一個不接高電平,電路就不導通。

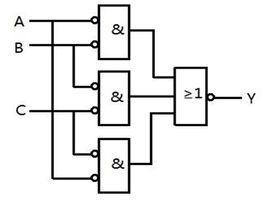

常見的門電路如下所示:

非門:利用內部結構,使輸入的電平變成相反的電平,高電平(1)變低電平(0),低電平(0)變高電平(1)。

與門:利用內部結構,使輸入兩個高電平(1),輸出高電平(1),不滿足有兩個高電平(1),則輸出低電平(0)。

或門:利用內部結構,使輸入至少一個輸入高電平(1),輸出高電平(1),不滿足有兩個低電平(0),輸出高電平(0)。

分析方法

在asic設計和pld設計中組合邏輯電路設計的最簡化是很重要的,在設計時常要求用最少的邏輯門或導線實現。在asic設計和pld設計中需要處理大量的約束項,值為1或0的項卻是有限的,提出組合邏輯電路設計的一種新方法。與邏輯表示只有在決定事物結果的全部條件具備時,結果才發生的因果關係。輸出變數為1的某個組合的所有因子的與表示輸出變數為1的這個組合出現、所有輸出變數為0的組合均不出現,因而可以表示輸出變數為1的這個組合。

邏輯電路的分析分以下幾個步驟:

(1)有給定的邏輯電路圖,寫出輸出端的邏輯表達式;

(2)列出真值表;

(3)通過真值表概括出邏輯功能,看原電路是不是最理想,若不是,則對其進行改進。