肖脫基勢壘

正文

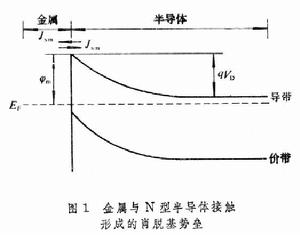

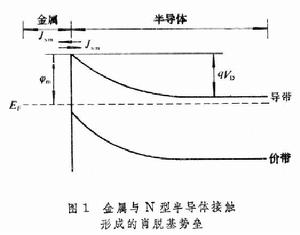

金屬和半導體相接觸時在半導體內形成的勢壘。圖1示意地畫出了金屬和 N型半導體之間形成的肖脫基勢壘。最初認為肖脫基勢壘起因於金屬和半導體具有不同的功函式,它們相接觸時產生的接觸電勢差;近年來的實驗表明,半導體表面態對勢壘的形成有極重要的影響。 肖脫基勢壘

肖脫基勢壘 代表金屬中電子越過勢壘ψm熱發射到半導體中的電流,J

代表金屬中電子越過勢壘ψm熱發射到半導體中的電流,J 代表半導體中的電子越過勢壘qVD熱發射到金屬中的電流。圖2a表示沒有外加電壓的平衡情況,J

代表半導體中的電子越過勢壘qVD熱發射到金屬中的電流。圖2a表示沒有外加電壓的平衡情況,J 與J

與J 相抵,總電流為零。圖2b表示正向偏壓的情況,這時半導體側勢壘高度降低,J

相抵,總電流為零。圖2b表示正向偏壓的情況,這時半導體側勢壘高度降低,J (同時也是總電流)隨外加電壓指數增長。圖2c表示加反向偏壓的情況,勢壘高度qVD增加,J

(同時也是總電流)隨外加電壓指數增長。圖2c表示加反向偏壓的情況,勢壘高度qVD增加,J 隨外加電壓指數減小,總電流趨向飽和值J

隨外加電壓指數減小,總電流趨向飽和值J 。

。  肖脫基勢壘

肖脫基勢壘 肖脫基勢壘

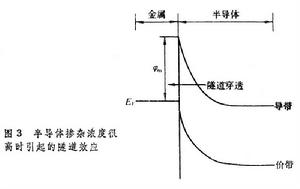

肖脫基勢壘當半導體摻雜濃度很高的時候,肖脫基勢壘區寬度減小,電子可以藉助隧道效應穿過勢壘,如圖3所示。這時不再表現出具有整流性質,而接觸成為歐姆接觸。

參考書目

E. H. Rhoderick, Mctal-Semiconductor Contacts, Clarendon Press, Oxford, 1978.