概述

目前市面上已經有多款雙核手機處理器,這通常指移動處理器的雙核CPU,其中兩種結構。同步雙核是指兩個CPU核心一起以相同頻率和電壓完成同一任務;異步雙核中,兩個核心可以以相同或不同頻率及電壓單獨執行處理指令,不需要兩個一起開動來完成一個任務而造成不必要的能耗。

手機異步雙核處理器:異步雙核可以根據任務需求開啟一個核心或者多個核心並且調整CPU的時鐘頻率,。

同步CPU——Synchronous,Synchronism,是指各個CPU核心必須以相同頻率相同電壓時工作或同時休息,不能輪流工作,二級快取共享。CPU性能得到最大發揮,但同時也帶來更高的功耗。目前手機同步雙核包括三星Exynos4210,德儀OMAP44x0,高通驍龍S4,Nvidia的Tegra2等,代表有三星i9100,MOTO XT910,LG P990。

異步CPU——Asynchronism,各個CPU核心能夠同時以相同或不同頻率電壓處理不同任務,二級快取共享,顯著降低能耗。目前異步雙核手機處理器多採用了高通的處理器,比如高通MSM8260(代表機型是小米M1,HTC的G14,G17,G18等)、MSM8660(代表機型是小米電信定製版、三星GALAXY SII(I929)、酷派9900等)、MSM8960(代表機型華碩PadFone、三星GALAXY SIII (I535)、HTC One XC和海爾W910等)、APQ8060(代表機型三星GALAXY SII HD LTE等)等。

同步異步的區別:同步的2個CPU是一個整體,無論多少個任務指令 ,都同時合力先完成一個,然後再完成下一個,和電腦CPU相似。異步的2個CPU可獨立工作,分別完成不同的任務。在第一個CPU未達到滿載狀態時,第二個CPU首選執行其他任務或者空閒(不啟動);只有在第一個CPU滿載非常嚴重的情況,第二個CPU才會主動分擔第一個CPU的任務。所以並不是網路上謠傳的兩個核心不能同時執行一個任務。

高通aSMP(Asynchronism Symmetric Multiprocessing),是採用在一個CPU滿載情況下再啟用另一個CPU,在待機和運行CPU性能需求較低的軟體程式方面,的確有相對低功耗的優勢。目前,手機大多數都是待機狀態或執行性能要求較低的任務(如網頁瀏覽、即時通訊套用等),而且大多數套用在開發的時候其實都是單執行緒的,也就是說本質上大多數套用只能分配給一個CPU核心處理,所以,異步多處理還是可以很好的降低功耗,因而更加省電。

所以說,相比同步結構的雙核CPU,異步雙核的最大優點是在保證手機性能的同時將功耗降低,表現為更省電。

雙核手機

雙核手機手機異步雙核cpu

主要指由高通Scorpion架構和Krait架構引起。

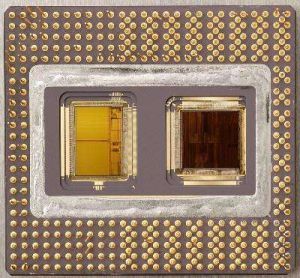

高通自稱MSM8260的aSMP結構

高通自稱MSM8260的aSMP結構2011 年,高通發布雙核手機處理器MSM8x60,集成世界上首款採用Asymmetric SMP(異步對稱多處理)架構的雙核CPU。異步架構與同步架構不同,由於兩個CPU核心可以分別執行不同的任務,引起了一部分人的誤解,認為異步雙核的CPU核心不能同時工作,而只能交替工作,是假雙核,並將MSM8x60戲稱為“膠水雙核”。(“膠水雙核”一詞最早是在PC處理器廠商Intel和AMD的爭論中出現的,並進而引發了“膠水”與“原生”雙核及四核之爭。2005年,Intel將兩顆Pentium 4核心封裝在一個基板上,組成了Pentium D,AMD認為這種架構是假雙核,是用“膠水”將兩個單核CPU“拼”成的雙核。)

intel的Pentium pro膠水核心

intel的Pentium pro膠水核心這裡涉及到對Asymmetric和SMP的理解。

SMP——Symmetric multiprocessing,對稱多處理,作業系統可以同時管理所有CPU核心,套用並不限定某一個核心,任務平均分配到每個cpu核心。

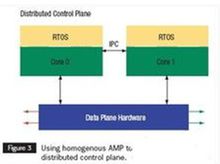

相對SMP的是AMP——Asymmetric multiprocessing,非對稱多處理,作業系統不能同時管理所有CPU核心,每個cpu核心可以由不同的作業系統管理,每個套用只能限定一個核心,特定的任務只能分配給某一個特定的核心。

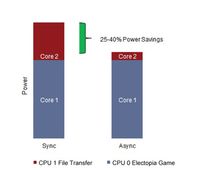

異步對稱式多核處理器(aSMP):以電源效率為設計理念。為了獲得更好的功效、性能表現和熱曲線,高通將最新的Krait微架構設計為異步對稱式多核處理器系統(或稱為aSMP)。aSMP架構和同步SMP 架構之間的區別是: 獨立的時鐘和電壓:aSMP系統中的每個核,包括二級快取,都有一個獨立的電壓和時鐘。這使每個CPU 核心都能夠根據處理的工作類型,以最有效的電壓和頻率運行,從而獲得最佳功耗。

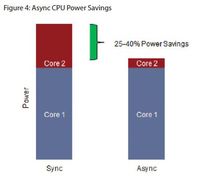

功耗減少25-40%:如圖4 所示,aSMP架構比當前的同步SMP 架構功耗減少25-40%。

待機功耗:在aSMP中,每個不需使用的核心都可以完全獨立關閉,使其在待機狀態時沒有功耗。

降低複雜性:aSMP不需要“伴隨核心”或“小核心”,對每個核心電壓和頻率的單獨控制使aSMP系統中的每個核心均可在低功率模式下操作,從而減少了多核對程式管理或更複雜的軟體管理的需求。

異步CPU 功耗節省

異步CPU 功耗節省異步CPU 功耗節省

典型的AMP處理器如手機的AP+ BP的SOC。

意法u8500的ap+bp的amp結構

意法u8500的ap+bp的amp結構意法u8500的ap+bp的amp結構

大多數手機都含有兩個處理器。作業系統、用戶界面和應用程式都在ApplicationProcessor(AP)上執行,AP一般採用基於ARM架構的CPU(業內多數手機CPU廠商選擇直接購買ARM的CPU設計,然後與其它組件整合,比如GPU、多媒體處理、數據機等等,製造出完整的SoC片上系統。這些現成的CPU都是基於ARM Cortex A5、A8、A9,甚至A15微架構的,而Cortex架構則是基於ARM自主的v7指令集進行開發的。但也有少數手機處理器廠商,如高通,直接在v7指令集的基礎上開發自己的處理器微架構,如Scorpion和Krait,進而設計自主的CPU)。而手機射頻通訊控制系統,則運行在另一個分開的CPU——Baseband Processor(BP),即基帶晶片(Modem)。

BP運行實時作業系統,執行射頻射頻控制(信號調製、編碼、射頻位移等)。BP的好處是,無論採用的作業系統和套用軟體變化,都可以正確的執行通訊功能。應用程式作業系統和驅動的bug也不會導致設備傳送災難性的數據到行動網路中。

AP+BP就是一個典型的AMP:通訊系統和程式系統不能同時控制兩個處理器,通訊任務或應用程式任務不能在兩個處理器之間平分,只能是由一個

AMP結構示意圖

AMP結構示意圖AMP結構示意圖

而同步CPU——Synchronous,Synchronism,是指各個CPU核心同時以同一頻率運行,參與各方必須採用同一時脈。

異步CPU——Asynchronism,各個CPU核心可以各自以不同的頻率運行,參與各方不採用同一時脈。

由此可見,所謂同步和異步的概念源自對Symmetric(對稱)和Asymmetric(非對稱)的理解和翻譯。同步=SMP,異步=AMP,這是大部分人的概念。

SMP或AMP指的是兩個以上的處理單元之間的狀態,一個手機處理器多個處理器單元之間可以存在不同的狀態:CPU和GPU之間,CPU和DSP之間,CPU和FUP之間是BMP;CPU(AP)和基帶晶片(BP)之間是AMP;而CPU和CPU之間是SMP。

另外還有介於SMP和AMP之間的BMP——Bound multiprocessing,作業系統可以同時管理所有CPU核心,但每個套用被鎖定於某個指定的CPU核心。

而Nvidia的Tegra3採取了VSMP——Variable SMP ,可變式對稱多處理,動態地啟用或禁用一個或四個cpu核心,以達到降低功耗的作用。任務平均分配到所有未關閉的cpu核心,未關閉的核心都以同一頻率運行。

高通ASMP示意圖

高通ASMP示意圖而高通的ASMP——Asymmetric SMP,非對稱的對稱處理,根據高通的說法,CPU核心可以以不同的頻率運行,必要時可以關閉部分CPU核心,而任務在CPU核心之間不平均分配。即SMP的兩個CPU核心採取了AMP的方式運行。

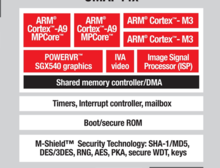

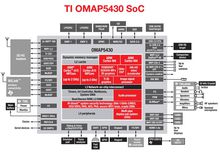

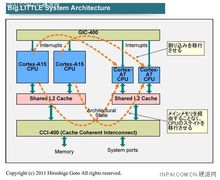

這種情況更類似於ARM結構中big.LITTLE的coretx a15+cortex a7的CPU+SPU(Synergistic Processing Unit,協處理器)的思想,也類似在德州儀器omap4470的SOC中,採用的coretex a9 x2+ cortex m3 x2,和omap5430中採用的coretx a15 x2+cortex m4 x2的cpu+ m系spu的協處理器切換方式,只不過高通將不對稱的SPU——cortex a7或cortex m3(m4)換成了和CPU對稱的CPU核心。

德儀omap4430的a9+m3協處理方式

德儀omap4430的a9+m3協處理方式 omap5430的a15+m4協處理方式

omap5430的a15+m4協處理方式 big.LITTLE的協處理器方式

big.LITTLE的協處理器方式和big.LITTLE,Ax+Mx協處理方式的cpu核心切換,SPU關閉不同,高通的ASMP的cpu核心切換後,作為SPU的CPU核心沒有關閉,SMP的兩個cpu核心以Asymmetric方式運行。如果big.LITTle,Ax+Mx在cpu核心切換後,協處理器沒有關閉,而是繼續運行,那么可以稱為Symmetric AMP,sAMP,AMP的主cpu核心和SPU以Symmetric方式運行。

| | SMP | ASMP | VSMP | AMP | BMP |

| 系統能否同時管理所有CPU | Yes | Yes | Yes | No | Yes |

| 任務在所有cpu核心分配方式 | 平均分配 | 指定某一個cpu 執行 | 平均分配 | 指定某一個cpu 執行 | 只能特定一個cpu 執行 |

| 能否關閉cpu核心 | No | Yes | Yes | Yes | Yes |

| 運行中的cpu核心 是否以同一頻率運行 | Yes | No | Yes | No | No |

| 典型代表 | cpu+cpu gpu+gpu | | tegra3的 a9 x4+ a9 x1(spu) | ap+bp | cpu+gpu cpu+dsp |

以上對比可見,高通的ASMP,從本質上是一個披著SMP外衣的AMP,是一個能夠同時管理所有CPU核心AMP,在CPU核心管理上採取SMP的方式,在任務分配上採取了AMP的方式,與其說是SMP的一種,不如說是AMP的改進型。

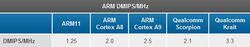

只要各CPU核心不採取同一時脈,就是異步處理器,與架構無關。平時所謂的高通異步雙核如驍龍S3系列(MSM8260,MSM8660,APQ8060)等高通Scorpion架構雙核,驍龍S4系列(MSM8960,MSM8260a,MSM8270)等krait架構雙核,及Krait四核CPU,更準確的說法是ASMP,異步對稱處理器。

總結——無論如何,高通scorpion和krait架構的雙核,四核,都是異步多核,並不是偽雙核,或者非原生雙核。

雙核的概念沒有“真”或“偽”之分,所以也沒有“原生”或”非原生“的絕對標準。就算是omap44x0和exynos代表的同步雙核也有部分異步的概念,異步雙核在某些情況下也能同步。同步或異步主要以是否按照同一頻率時脈來劃分,但並非唯一標準。即使單純考慮性能,很多時候高通雙核並不輸所謂的同步雙核甚至四核,考慮功耗以及散熱的情況下,優勢更明顯。

同步的2個CPU是一個整體,無論多少個任務指令 ,都同時合力先完成一個,然後再完成下一個,和電腦CPU相似。異步的2個CPU可獨立工作,多個任務時分別分開完成不同的任務。第一個在CPU滿載狀態,不能獨立完成任務指令時,第二個CPU首選不管第一CPU去執行下一個任務或者空閒(不啟動),第一CPU在滿載的非常嚴重的情況下才會主動分擔第一CPU的任務。

高通ASMP處理器和標準SMP有較多的差異,兩者不能簡單劃為同一類。

ASMP運行方式

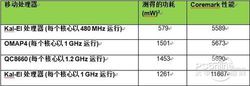

高通的ASMP與標準的SMP存在有差異的cpu運作方式。下面以高通msm8260和德州儀器omap4430來說明。

德州儀器omap4430,cortex-a9架構雙核,默頻1.0ghz,標準SMP。不強制同步,IPC( Instruction Per Clock)為2.5mips/mhz,功耗效率為0.265mw/mips,調頻級數為300mhz——418mhz——536mhz——654mhz——772mhz——890mhz———1008mhz。

高通msm8260,scorpion架構雙核,默頻1.2ghz或1.5ghz,ASMP,異步,IPC為2.1mips/mhz,功耗效率為0. 255mw/mips。調頻級數為384mhz——518mhz———652mhz———786mhz———920mhz———1188mzh。

msm8260和omap4430的功耗比較

msm8260和omap4430的功耗比較 cortex-a9和socrpion架構dmips標準

cortex-a9和socrpion架構dmips標準| 不同的cpu性能需要(假設) | omap4430的SMP | msm8260的ASMP | ||||||||||

| cpu 1的頻率 | cpu 2的頻率 | 總體cpu性能輸出 | 功耗 | 多餘的cpu性能 | 浪費的cpu功耗 | cpu 1的頻率 | cpu 2的頻率 | 總體cpu性能輸出 | 功耗 | 多餘的cpu性能 | 浪費的cpu功耗 | |

| 待機—0mips | 300mhz | 300mhz | 1500mips | 397.5mw | 1500mips | 397.5mw | 384mhz | 0mhz | 806mips | 205.5mw | 806mips | 205.5mw |

| 無外掛程式桌面—700mips | 300mhz | 300mhz | 1500mips | 397.5mw | 800mips | 212mw | 384mhz | omhz | 806mips | 205.5mw | 106mips | 27mw |

| 全外掛程式桌面—1500mips | 300mhz | 300mhz | 1500mips | 397.5mw | 0mips | 0mw | 786mhz | 0mhz | 1650mips | 420.7mw | 150mips | 38.25mw |

| www方式打開新浪首頁—2500mips | 536mhz | 536mhz | 2680mips | 710mw | 180mips | 47.7mw | 1188mihz | 0mhz | 2500mips | 637.5mw | 0mips | 0mw |

| 《極品飛車》遊戲—3500mips | 772mhz | 772mhz | 3860mips | 1023mw | 360mips | 95mw | 1188mhz | 652mhz | 3869mips | 986.6mw | 369mips | 94mw |

| 《質量效應》——45000mips | 890mhz | 890mhz | 4450mips | 1179mw | 0mips | 0mw | 1188mhz | 920mhz | 4427mips | 1129mw | 0mips | 0mw |

以上圖表對比可見:

第一,高通ASMP,是採用在一個cpu滿載情況下再啟用另一個gpu,在待機和低cpu性能需求的軟體程式方面,的確有相對低功耗的優勢,但在高cpu性能需求的軟體和遊戲時,功耗和cortex a9的SMP有是一樣的,在待機狀態還是省電。全負荷狀態時是一樣的。

第二,高通ASMP,在性能載入速度要比AMP慢。

比如,omap4430從桌面啟動《質量效應》遊戲,僅需對cpu進行5次增加電壓,提升頻率即可:

300mhz x2——418mhz x2——536mhz x2——654mhz x2——772mhz x2——890mhz x2

而高通msm8260則需要7次加壓:

786mhz + 0mhz——920mhz + 0mhz———1188mhz + 0mhz———1188mhz + 384mhz————1188mhz + 518mhz——1188mhz + 652mhz——1188mhz + 768mhz——1188mhz + 920mhz

第三,兩個cpu核心長期處於不同狀態,對其使用壽命也會有較大差異。

總之, ASMP的異步cpu運行方式在低性能需求躍遷到高性能需求時,躍遷幅度越大,加電壓的次數越多,需時越長。ASMP的低功耗優勢在待機和低cpu需求時明顯,高cpu需求時優勢縮小甚至沒有。長期將任務由一個cpu核心執行,其相對SMP的cpu核心的壽命會縮短,而長期閒著的cpu核心則相對延長。

ASMP和非強制同步SMP的區別

高通msm8x60的Asynchronous Symmetric Multiprocessing運作方式(Asynchronous SMP),本質仍是SMP,在處理器中,兩個核心的p-state——power state,電源管理狀態,相當於電源門控power gating技術,用電源控制來切換cpu核心功率——是獨立的,可以動態根據負載調整每個核心的電壓和頻率,乃至直接關閉其中的一個核心,是節省電力的一種手段。

從該角度上說目前幾乎所有的多核處理器都是Asynchronous SMP,比如Intel從Nehalem開始引進的p-gating,AMD從Thuban開始引進的Unganged CNQ和Llano/Bobcat的p-gating。TI OMPA4 Series,三星Exynos以及蘋果A5也都無一例外地採取了非強制同步的設計。唯一的例外就是強制同步運作的Tegra 2,而NV將在Kal-El上引入該機制。

但SMP的動態電壓與頻率調整技術(Dynamic Voltage and Frequency Scaling,DVFS)與高通的ASMP還是有明顯差異:SMP支持TLP(Thread level parallelism,執行緒級平行),而不支持TLP;SMP在多執行緒。亂序處理下才能使用DVFS,ASMP無論是否多執行緒亂序處理下都異步運作。

| | SMP的動態調整電壓技術 | 高通ASMP的異步電壓和頻率 |

| 開啟前提 | 亂序處理,多執行緒 | 任何時候 |

| 任務分配方式 | 平均分配 | 指定一個cpu核心完成 |

| 能否關閉cpu核心 | No | Yes |

| 伴核切換後是否關閉 | Yes | No |

| cpu核心之間的頻率差距 | 不能相差太大,只能相差一級到兩級調頻級數。 | 可以相差非常大,一個滿載最高頻率,一個空載關閉。 |

由此可見,在順序處理或單執行緒下,omap4430仍然是按兩個cpu核心同頻,如536mhz x2的方式存在,根本不可能存在536mhz + 654mhz 的方式。在亂序處理和多執行緒下,omap4460允許存在536mhz + 654mhz甚至1008mhz +772mhz的方式,但不可能存在418mhz +0mhz的方式,即一個對稱cpu核心關閉的情況,也不存在890mhz +418mhz的級數相差太大的方式。

但對於ASMP的msm8260,不僅可以1188mhz +0mhz的一個對稱cpu核心關閉情況,也可以1188mhz+384mhz的級數相差非常大的情況。

同步的ASMP和SMP的區別

在cpu最大載入情況下,異步雙核也可以達到兩個cpu核心都按同一個頻率——最高頻率運行,但實際上仍不是采同一時脈,只是兩個時脈恰好同頻。在某些技術手段下,如頻率調節軟體tegrak,可以使異步雙核在除最高頻率外的同一頻率下運行。此時稱為同步asmp。但即使如此,異步雙核的仍然與同步雙核標準SMP有本質上的區別。