將電路製造在半導體晶片表面上的積體電路又稱薄膜(thin-film)積體電路。另有一種厚膜(thick-film)積體電路(hybrid integrated circuit)是由獨立半導體設備和被動組件,集成到襯底或線路板所構成的小型化電路。

從1949年到1957年,維爾納·雅各比(Werner Jacobi)、傑弗里·杜默(Jeffrey Dummer)、西德尼·達林頓(Sidney Darlington)、樽井康夫(Yasuo Tarui)都開發了原型,但現代積體電路是由傑克·基爾比在1958年發明的。其因此榮獲2000年諾貝爾物理獎,但同時間也發展出近代實用的積體電路的羅伯特·諾伊斯,卻早於1990年就過世。

介紹

電晶體發明並大量生產之後,各式固態半導體組件如二極體、電晶體等大量使用,取代了真空管在電路中的功能與角色。到了20世紀中後期半導體製造技術進步,使得積體電路成為可能。相對於手工組裝電路使用個別的分立電子組件,積體電路可以把很大數量的微電晶體集成到一個小晶片,是一個巨大的進步。積體電路的規模生產能力,可靠性,電路設計的模組化方法確保了快速採用標準化積體電路代替了設計使用離散電晶體。

積體電路對於離散電晶體有兩個主要優勢:成本和性能。成本低是由於晶片把所有的組件通過照相平版技術,作為一個單位印刷,而不是在一個時間只製作一個電晶體。性能高是由於組件快速開關,消耗更低能量,因為組件很小且彼此靠近。2006年,晶片面積從幾平方毫米到350 mm²,每mm²可以達到一百萬個電晶體。

第一個積體電路雛形是由傑克·基爾比於1958年完成的,其中包括一個雙極性電晶體,三個電阻和一個電容器。

根據一個晶片上集成的微電子器件的數量,積體電路可以分為以下幾類:

•小型積體電路(SSI英文全名為Small Scale Integration)邏輯門10個以下或電晶體100個以下。

•中型積體電路(MSI英文全名為Medium Scale Integration)邏輯門11~100個或 電晶體101~1k個。

•大規模積體電路(LSI英文全名為Large Scale Integration)邏輯門101~1k個或 電晶體1,001~10k個。

•超大規模積體電路(VLSI英文全名為Very large scale integration)邏輯門1,001~10k個或 電晶體10,001~100k個。

•極大規模積體電路(ULSI英文全名為Ultra Large Scale Integration)邏輯門10,001~1M個或 電晶體100,001~10M個。

•GLSI(英文全名為Giga Scale Integration)邏輯門1,000,001個以上或電晶體10,000,001個以上。

積體電路的發展

最先進的積體電路是微處理器或多核處理器的核心,可以控制計算機到手機到數字微波爐的一切。雖然設計開發一個複雜積體電路的成本非常高,但是當分散到通常以百萬計的產品上,每個積體電路的成本最小化。積體電路的性能很高,因為小尺寸帶來短路徑,使得低功率邏輯電路可以在快速開關速度套用。

這些年來,積體電路持續向更小的外型尺寸發展,使得每個晶片可以封裝更多的電路。這樣增加了每單位面積容量,可以降低成本和增加功能,見摩爾定律,積體電路中的電晶體數量,每1.5年增加一倍。總之,隨著外形尺寸縮小,幾乎所有的指標改善了,單位成本和開關功率消耗下降,速度提高。但是,集成納米級別設備的IC也存在問題,主要是泄漏電流。因此,對於最終用戶的速度和功率消耗增加非常明顯,製造商面臨使用更好幾何學的尖銳挑戰。這個過程和在未來幾年所期望的進步,在半導體國際技術路線圖中有很好的描述。

僅僅在其開發後半個世紀,積體電路變得無處不在,計算機、手機和其他數字電器成為社會結構不可缺少的一部分。這是因為,現代計算、交流、製造和交通系統,包括網際網路,全都依賴於積體電路的存在。甚至很多學者認為有積體電路帶來的數字革命是人類歷史中最重要的事件。IC的成熟將會帶來科技的大躍進,不論是在設計的技術上,或是半導體的工藝突破,兩者都是息息相關。

分類

積體電路的分類方法很多,依照電路屬模擬或數字,可以分為:模擬積體電路、數字積體電路和混合信號積體電路(模擬和數字在一個晶片上)。

數字積體電路可以包含任何東西,在幾平方毫米上有從幾千到百萬的邏輯門、觸發器、多任務器和其他電路。這些電路的小尺寸使得與板級集成相比,有更高速度,更低功耗(參見低功耗設計)並降低了製造成本。這些數字IC,以微處理器、數位訊號處理器和微控制器為代表,工作中使用二進制,處理1和0信號。

模擬積體電路有,例如感測器、電源控制電路和運放,處理模擬信號。完成放大、濾波、解調、混頻的功能等。通過使用專家所設計、具有良好特性的模擬積體電路,減輕了電路設計師的重擔,不需凡事再由基礎的一個個電晶體處設計起。

積體電路可以把模擬和數字電路集成在一個單晶片上,以做出如模擬數字轉換器和數字模擬轉換器等器件。這種電路提供更小的尺寸和更低的成本,但是對於信號衝突必須小心。

製造

參見:半導體器件製造和積體電路設計

從1930年代開始,元素周期表中的化學元素中的半導體被研究者如貝爾實驗室的威廉·肖克利(William Shockley)認為是固態真空管的最可能的原料。從氧化銅到鍺,再到矽,原料在1940到1950年代被系統的研究。今天,儘管元素中期表的一些III-V價化合物如砷化鎵套用於特殊用途如:發光二極體、雷射、太陽能電池和最高速積體電路,單晶矽成為積體電路主流的基層。創造無缺陷晶體的方法用去了數十年的時間。

半導體積體電路工藝,包括以下步驟,並重複使用:

•光刻

•刻蝕

•薄膜(化學氣相沉積或物理氣相沉積)

•摻雜(熱擴散或離子注入)

•化學機械平坦化CMP

使用單晶矽晶圓(或III-V族,如砷化鎵)用作基層,然後使用光刻、摻雜、CMP等技術製成MOSFET或BJT等組件,再利用薄膜和CMP技術製成導線,如此便完成晶片製作。因產品性能需求及成本考量,導線可分為鋁工藝(以濺鍍為主)和銅工藝(以電鍍為主參見Damascene)。主要的工藝技術可以分為以下幾大類:黃光微影、刻蝕、擴散、薄膜、平坦化製成、金屬化製成。

IC由很多重疊的層組成,每層由視頻技術定義,通常用不同的顏色表示。一些層標明在哪裡不同的摻雜劑擴散進基層(成為擴散層),一些定義哪裡額外的離子灌輸(灌輸層),一些定義導體(多晶矽或金屬層),一些定義傳導層之間的連線(過孔或接觸層)。所有的組件由這些層的特定組合構成。

•在一個自排列(CMOS)過程中,所有門層(多晶矽或金屬)穿過擴散層的地方形成電晶體。

•電阻結構,電阻結構的長寬比,結合表面電阻係數,決定電阻。

•電容結構,由於尺寸限制,在IC上只能產生很小的電容。

•更為少見的電感結構,可以製作晶片載電感或由迴旋器模擬。

因為CMOS設備只引導電流在邏輯門之間轉換,CMOS設備比雙極型組件(如雙極性電晶體)消耗的電流少很多。透過電路的設計,將多顆的電晶體管畫在矽晶圓上,就可以畫出不同作用的積體電路。

隨機存取存儲器是最常見類型的積體電路,所以密度最高的設備是存儲器,但即使是微處理器上也有存儲器。儘管結構非常複雜-幾十年來晶片寬度一直減少-但積體電路的層依然比寬度薄很多。組件層的製作非常像照相過程。雖然可見光譜中的光波不能用來曝光組件層,因為他們太大了。高頻光子(通常是紫外線)被用來創造每層的圖案。因為每個特徵都非常小,對於一個正在調試製造過程的過程工程師來說,電子顯微鏡是必要工具。

在使用自動測試設備(ATE)包裝前,每個設備都要進行測試。測試過程稱為晶圓測試或晶圓探通。晶圓被切割成矩形塊,每個被稱為晶片(“die”)。每個好的die被焊在“pads”上的鋁線或金線,連線到封裝內,pads通常在die的邊上。封裝之後,設備在晶圓探通中使用的相同或相似的ATE上進行終檢。測試成本可以達到低成本產品的製造成本的25%,但是對於低產出,大型和/或高成本的設備,可以忽略不計。

在2005年,一個製造廠(通常稱為半導體工廠,常簡稱 fab,指fabrication facility)建設費用要超過10億美元,因為大部分操作是自動化的。

製造過程

晶片製作完整過程包括晶片設計、晶片製作、封裝製作、測試等幾個環節,其中晶片製作過程尤為的複雜。

首先是晶片設計,根據設計的需求,生成的“圖樣”

晶片的原料晶圓

晶圓的成分是矽,矽是由石英沙所精練出來的,晶圓便是矽元素加以純化(99.999%),接著是將這些純矽製成矽晶棒,成為製造積體電路的石英半導體的材料,將其切片就是晶片製作具體所需要的晶圓。晶圓越薄,生產的成本越低,但對工藝就要求的越高。

晶圓塗膜

晶圓塗膜能抵抗氧化以及耐溫能力,其材料為光阻的一種。

晶圓光刻顯影、蝕刻

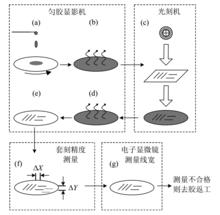

光刻工藝的基本流程如圖1 所示。首先是在晶圓(或襯底)表面塗上一層光刻膠並烘乾。烘乾後的晶圓被傳送到光刻機裡面。光線透過一個掩模把掩模上的圖形投影在晶圓表面的光刻膠上,實現曝光,激發光化學反應。對曝光後的晶圓進行第二次烘烤,即所謂的曝光後烘烤,後烘烤是的光化學反應更充分。最後,把顯影液噴灑到晶圓表面的光刻膠上,對曝光圖形顯影。顯影后,掩模上的圖形就被存留在了光刻膠上。塗膠、烘烤和顯影都是在勻膠顯影機中完成的,曝光是在光刻機中完成的。勻膠顯影機和光刻機一般都是在線上作業的,晶圓通過機械手在各單元和機器之間傳送。整個曝光顯影系統是封閉的,晶圓不直接暴露在周圍環境中,以減少環境中有害成分對光刻膠和光化學反應的影響 。

圖1 現代光刻工藝的基本流程和光刻後的檢測步驟

圖1 現代光刻工藝的基本流程和光刻後的檢測步驟該過程使用了對紫外光敏感的化學物質,即遇紫外光則變軟。通過控制遮光物的位置可以得到晶片的外形。在矽晶片塗上光致抗蝕劑,使得其遇紫外光就會溶解。這時可以用上第一份遮光物,使得紫外光直射的部分被溶解,這溶解部分接著可用溶劑將其沖走。這樣剩下的部分就與遮光物的形狀一樣了,而這效果正是我們所要的。這樣就得到我們所需要的二氧化矽層。

摻加雜質

將晶圓中植入離子,生成相應的P、N類半導體。

具體工藝是是從矽片上暴露的區域開始,放入化學離子混合液中。這一工藝將改變攙雜區的導電方式,使每個電晶體可以通、斷、或攜帶數據。簡單的晶片可以只用一層,但複雜的晶片通常有很多層,這時候將該流程不斷的重複,不同層可通過開啟視窗聯接起來。這一點類似多層PCB板的製作原理。 更為複雜的晶片可能需要多個二氧化矽層,這時候通過重複光刻以及上面流程來實現,形成一個立體的結構。

晶圓測試

經過上面的幾道工藝之後,晶圓上就形成了一個個格狀的晶粒。通過針測的方式對每個晶粒進行電氣特性檢測。一般每個晶片的擁有的晶粒數量是龐大的,組織一次針測試模式是非常複雜的過程,這要求了在生產的時候儘量是同等晶片規格構造的型號的大批量的生產。數量越大相對成本就會越低,這也是為什麼主流晶片器件造價低的一個因素。

封裝

將製造完成晶圓固定,綁定引腳,按照需求去製作成各種不同的封裝形式,這就是同種晶片核心可以有不同的封裝形式的原因。比如:DIP、QFP、PLCC、QFN等等。這裡主要是由用戶的套用習慣、套用環境、市場形式等外圍因素來決定的。

測試、包裝

經過上述工藝流程以後,晶片製作就已經全部完成了,這一步驟是將晶片進行測試、剔除不良品,以及包裝。

封裝

最早的積體電路使用陶瓷扁平封裝,這種封裝很多年來因為可靠性和小尺寸繼續被軍方使用。商用電路封裝很快轉變到雙列直插封裝,開始是陶瓷,之後是塑膠。1980年代,VLSI電路的針腳超過了DIP封裝的套用限制,最後導致插針格線數組和晶片載體的出現。

表面貼著封裝在1980年代初期出現,該年代後期開始流行。它使用更細的腳間距,引腳形狀為海鷗翼型或J型。以Small-Outline Integrated Circuit(SOIC)為例,比相等的DIP面積少30-50%,厚度少70%。這種封裝在兩個長邊有海鷗翼型引腳突出,引腳間距為0.05英寸。

Small-Outline Integrated Circuit(SOIC)和PLCC封裝。1990年代,儘管PGA封裝依然經常用於高端微處理器。PQFP和thin small-outline package(TSOP)成為高引腳數設備的通常封裝。Intel和AMD的高端微處理現在從PGA(Pine Grid Array)封裝轉到了平面格線陣列封裝(Land Grid Array,LGA)封裝。

球柵數組封裝封裝從1970年代開始出現,1990年代開發了比其他封裝有更多管腳數的覆晶球柵數組封裝封裝。在FCBGA封裝中,晶片(die)被上下翻轉(flipped)安裝,通過與PCB相似的基層而不是線與封裝上的焊球連線。FCBGA封裝使得輸入輸出信號陣列(稱為I/O區域)分布在整個晶片的表面,而不是限制於晶片的外圍。如今的市場,封裝也已經是獨立出來的一環,封裝的技術也會影響到產品的質量及良率。

![晶片[半導體元件產品的統稱] 晶片[半導體元件產品的統稱]](/img/b/cab/nBnauM3XwMTN0MDM2ETMzYDM1UTM1QDN5MjM5ADMwAjMwUzLxEzLyQzLt92YucmbvRWdo5Cd0FmLyE2LvoDc0RHa.jpg)