時鐘門控的設計

回寫結構暫存器

回寫結構暫存器如何更加有效地設計時鐘門控對於最大限度地降低功耗,同時保證處理器的性能至關重要。多核多執行緒微處理器中,多個功能部件可能不是同時工作的,對於無執行任務的功能部件就可以將其時鐘關閉,減少其隨時鐘翻轉進行多餘的內部暫存器翻轉,從而降低產生功耗的浪費和熱量聚集。

對於需要控制的暫存器,在一定的情況下關閉暫存器的傳輸功能,阻止無用的數據進入下一級邏輯,避免引起一連串不必要的邏輯翻轉,達到降低功耗的可能。為最大限度地插人Clock-Gating控制邏輯,需要通過多種方式結合的辦法,在電路中插人更多的Clock-Giatgn控制,最大限度地插人門控時鐘設計,關閉更多的空閒功能部件,降低功耗 。

Clock-Gating結構暫存器

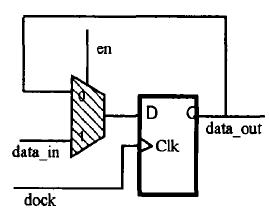

Clock-Gating結構暫存器關閉暫存器的傳播功能通常可以通過“回寫”結構來實現(如圖1),以使能信號en為控制信號在前繼輸人data-in和本級暫存器輸出data-out之間進行選擇,如果不需要傳播數據時,就可以使輸出保持為data-out而不引起後繼部件的翻轉。這種方式可以以最小的面積和功耗代價實現對暫存器傳輸功能的關閉。

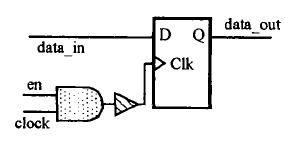

但是,回寫結構只是在功能上實現了關閉傳播和降低後繼組合邏輯功耗的作用,但在時鐘功耗上並沒有較大降低,因為在回寫結構關閉傳播功能後。lock信號仍始終在翻轉。為更大限度地降低功耗,引人暫存器的Clock-Gating設計(如圖2),將使能信號en作用於。lock上與回寫結構相比較,在關閉數據傳播後,圖1和圖2中用斜線標註的部件的動態功耗將被節省掉。

clock一Gatign控制邏輯也會產生一定的功耗(圖2中用點陰影標註的部件功耗),因此不是越多的Clock-Gating控制邏輯就越好,例如在需要添加Clock-Gating控制的暫存器檔案中,如果被控制的dock信號所連線的暫存器位數較小,得到的動態功耗降低還不足以抵消添加控制邏輯所增加的功耗。所以,通常對於需要進行Clock-Cating的暫存器檔案的位寬有一定限制(一般不低於3一8位),保證能有效地降低時鐘功耗。

由於OpenSPARC T2並未全面設計內部電路的時鐘門控控制邏輯,其中存在大量未被門控時鐘邏輯控制的暫存器部件,這就為功耗最佳化提供了巨大的潛力。通過分析和評估,利用基本的Clock-Gating最佳化策略,在原有結構中插人或替換為新的門控時鐘邏輯可以帶來40%一60%的功耗降低。

時鐘門控邏輯的最佳化

通常在設計的初級階段,由於設計者功耗分析手段的缺乏,往往無法考慮具體工藝技術帶來的技術差別,所以基本都採取非工藝相關的方式進行手工功耗分析,無法全面的掌握clock功耗的分布情況。在設計的後續階段,在對設計進行直接分析或在時序分析的基礎上,通過採用各種組合的最佳化技術,可以對Clock-Gating控制邏輯進一步加以最佳化 。

1.向前追溯最佳化

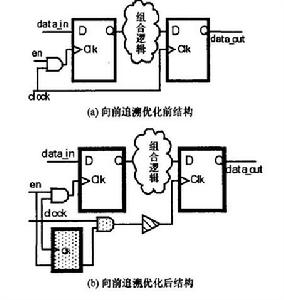

圖3

圖3通過時序分析,向前追溯最佳化可以帶來新的功耗降低,即如果在本級暫存器有Clock-Gating控制邏輯,而下一級暫存器沒有相關的Clock-Gating控制信號en的情況下(如圖3(a)所示),此時在下一級也通過延遲一個時鐘周期的Clock-Gating控制信號en(t+l)對下一級暫存器時鐘關斷進行控制(如圖3(b)),可以更多地降低功耗。在產生新的控制信號en(t+l)時,需要注意將前一級控制信號en與時鐘clock實現同步,以保證控制關斷的正確性。

2.組合邏輯向前追溯最佳化

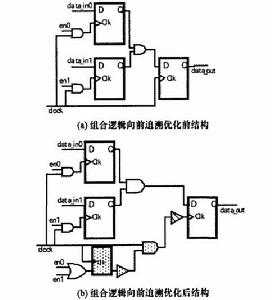

圖4

圖4而實際中的電路結構更為複雜,特別是控制信號en(t+l)的產生就需要根據具體情況具體分析。如圖4(a)所示,控制信號en1和en2對與邏輯門的兩個輸人前繼in1和in2的暫存器時鐘進行控制,為了降低 下一級暫存器的時鐘功耗,需要通過將en1和en2相或得到新的控制信號對下一級的暫存器時鐘進行控制,降低功耗(如圖4(b)所示。

同樣,越複雜的組合邏輯所需要的控制信號產生邏輯也會越複雜,可能帶來的代價也會越大,所以需要對降低的動態功耗和增加的部件功耗加以權衡,上文中關於Clock-Gating的位寬限制在這裡將會變得更加嚴格,一般要在暫存器位寬較大時考慮該措施。

3.向後追溯最佳化

更進一步,向後追溯同樣也能得到另一種新的功能消耗降低可能。即在本級暫存器有Clock-Gating控制,而上一級暫存器沒有相關的Clock-Gating控制的情況下,通過一定的邏輯得到較本級Clock-Gating控制的信號en提前一個時鐘周期的更早的Clock-Gating控制信號en(t-1),用於控制上一級暫存器時鐘的關斷,降低其動態消耗,而且還能降低兩級暫存器之間的組合邏輯部件的動態消耗。