多路選擇器分類

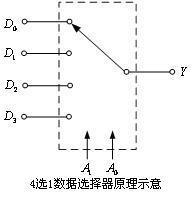

多路選擇器常見分類有4選1數據選擇器(見下圖)、8選1數據選擇器(型號為74151、74LS151、74251、74LS152)、16選1數據選擇器(可以用兩片74151連線起來構成)等之分。多路選擇器還包括匯流排的多路選擇,模擬信號的多路選擇等,相應的器件也有不同的特性和使用方法.具體可以查找相關網站。

多路選擇器

多路選擇器FPGA中多路選擇器結構

典型的 FPGA 器件主要包含 3 類基本資源:可程式邏輯塊(configurable logic block,CLB)、布線資源和可程式輸入/輸出模組。可程式邏輯塊四周被預製的布線資源通道包圍,可程式輸入/輸出模組分布在 FPGA四周,除了上述 3 種資源以外,通常在 FPGA 中還包含塊 RAM、乘法器等可選資源。

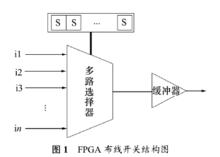

在 FPGA 各種資源中,可程式邏輯塊是實現用戶功能的基本單元,每個可程式邏輯塊包含 1 個互連開關矩陣和 4 個 SLICEs,其中每個 SLICE 包括 2 個查找表(Look-Up-Table,LUT)、2 個觸發器和一些多路選擇器。互連開關矩陣主要由不同長度導線和多個布線開關組成,典型的布線開關結構如圖 1 所示。

多路選擇器

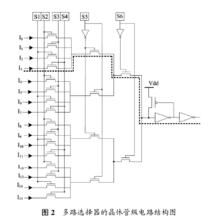

多路選擇器由圖 1 可見:每個布線開關由多路選擇器、緩衝器和一些可程式的 SRAM 單元構成。其中多路選擇器是連線各布線軌道和可程式邏輯塊的橋樑,其結構對FPGA 的性能和功耗都有較大的影響。根據多路選擇器所驅動的導線長度不同,FPGA 中多路選擇器的規模從 4 選 1 到 30 選 1 不等。圖 2 所示為 16 選 1 的多路選擇器電晶體級電路結構。

多路選擇器

多路選擇器多路選擇器的左邊是 16 條輸入線,用於連線布線軌道或可程式邏輯塊等資源,S1~S6 代表 6 個可程式SRAM 單元,通過配置 SRAM 單元的內容可以從 16條輸入線中選出 1 條作為有效輸入端,例如,當 S1~S6存儲單元的存儲值為“000100”時,輸入線 I3被選擇中,信號所經過的有效路徑如圖 2 中虛線所示。多路選擇器的主體部分是傳輸電晶體,由於 NMOS 電晶體載流子的遷移效率高,電路速度快,因此,多路選擇器中的傳輸電晶體均採用 NMOS 電晶體實現。

2選1

EDA和VHDL代碼

library ieee

use ieee.std_logic_1164.all;

entity data is

port(in0,in1,se1:in std_logic;

output:out std_logic);

architecture one of data is

begin

output<=in0 when se1="0"else in1;

end architecture one;

16位選擇器

VHDL語言

16位的多路選擇器,其功能是能夠試16位的信號同時附加到data1和data2上。

其VHDL語言如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity selc is

port(s:in std_logic_vector(1 downto 0);

data:in std_logic_vector(15 downto 0);

data1:out std_logic_vector(15 downto 0);

e: out std_logic;

data2:out std_logic_vector(15 downto 0));

end selc;

architecture fun of selc is

begin

process(s)

begin

case s is

when "00" => data1<=data;e<="1";

when "01" => data2<=data;e<="1";

when others => null;

end case;

end process;

end fun;