“分治法”戰略

英特爾工程師們開發了多核晶片,使之滿足“橫向擴展”(而非“縱向擴充”)方法,從而提高性能。該架構實現了“分治法”戰略。

通過劃分任務,執行緒套用能夠充分利用多個執行核心,並可在特定的時間內執行更多任務。

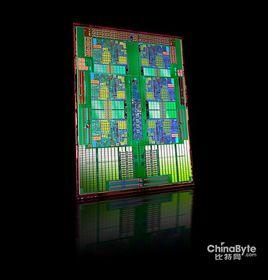

多核處理器是單枚晶片(也稱為“矽核”),能夠直接插入單一的處理器插槽中,但作業系統會利用所有相關的資源,將它的每個執行核心作為分立的邏輯處理器。通過在兩個執行核心之間劃分任務,多核處理器可在特定的時鐘周期內執行更多任務。

多核架構能夠使軟體更出色地運行,並創建一個促進軟體編寫更趨完善的架構。

儘管認真的軟體廠商還在探索全新的軟體並發處理模式,但是,隨著向多核處理器的移植,現有軟體無需被修改就可支持多核平台。

作業系統專為充分利用多個處理器而設計,且無需修改就可運行。為了充分利用多核技術,套用開發人員需要在程式設計中融入更多思路,但設計流程與對稱多處理 (SMP) 系統的設計流程相同,並且現有的單執行緒套用也將繼續運行。

得益於執行緒技術的套用在多核處理器上運行時將顯示出卓越的性能可擴充性。此類軟體包括多媒體套用(內容創建、編輯,以及本地和數據流回放)、工程和其他技術計算套用以及諸如套用伺服器和資料庫等中間層與後層伺服器套用。

多核技術能夠使伺服器並行處理任務,而在以前,這可能需要使用多個處理器,多核系統更易於擴充,並且能夠在更纖巧的外形中融入更強大的處理性能,這種外形所用的功耗更低、計算功耗產生的熱量更少。多核技術 是處理器發展的必然近20年來,推動微處理器性能不斷提高的因素主要有兩個:半導體工藝技術的飛速進步和體系結構的不斷發展。半導體工藝技術的每一次進步都為微處理器體系結構的研究提出了新的問題,開闢了新的領域;體系結構的進展又在半導體工藝技術發展的基礎上進一步提高了微處理器的性能。這兩個因素是相互影響,相互促進的。一般說來, 工藝和電路技術的發展使得處理器性能提高約20倍,體系結構的發展使得處理器性能提高約4倍,編譯技術的發展使得處理器性能提高約1.4倍。但是今天,這種規律性的東西卻很難維持。多核的出現是技術發展和套用需求的必然產物。這主要基於以下事實;

電晶體時代

根據摩爾定律,微處理器的速度以及單片集成度每18個月就會翻一番。經過多年的發展,通用微處理器的主頻已經突破了4GHz,數據寬度也達到64位。在製造工藝方面也同樣以驚人的速度在發展,0.13um工藝的微處理器已經批量生產,90nm工藝以下的下一代微處理器也已問世。照此下去,到2010年左右,晶片上集成的電晶體數目將超過10億個。因此,體系結構的研究又遇到新的問題:如何有效地利用數目眾多的電晶體?國際上針對這個問題的研究方興未艾。多核通過在一個晶片上集成多個簡單的處理器核充分利用這些電晶體資源,發揮其最大的能效。

全局連線

隨著VLSI工藝技術的發展,電晶體特徵尺寸不斷縮小,使得電晶體門延遲不斷減少,但互連線延遲卻不斷變大。當晶片的製造工藝達到0.18微米甚至更小時,線延遲已經超過門延遲,成為限制電路性能提高的主要因素。在這種情況下,由於CMP(單晶片多處理器)的分散式結構中全局信號較少,與集中式結構的超標量處理器結構相比,在克服線延遲影響方面更具優勢。

符合Pollack規則

按照Pollack規則,我們知道處理器性能的提升與其複雜性的平方根成正比。 如果一個處理器的硬體邏輯提高一倍,至多能提高性能40%,而如果採用兩個簡單的處理器構成一個相同硬體規模的雙核處理器,則可以獲得70%~80%的性能提升。同時在面積上也同比縮小。

能耗增長

隨著工藝技術的發展和晶片複雜性的增加,晶片的發熱現象日益突出。多核處理器里單個核的速度較慢,處理器消耗較少的能量,產生較少的熱量。同時,原來單核處理器里增加的電晶體可用於增加多核處理器的核。在滿足性能要求的基礎上,多核處理器通過關閉(或降頻)一些處理器等低功耗技術,可以有效地降低能耗。

設計成本

隨著處理器結構複雜性的不斷提高,和人力成本的不斷攀升,設計成本隨時間呈線性甚至超線性的增長。多核處理器通過處理器IP等的復用,可以極大降低設計的成本。同時模組的驗證成本也顯著下降。

結構發展

超標量(Superscalar)結構和超長指令字(VLIW)結構在高性能微處理器中被廣泛採用。但是它們的發展都遇到了難以逾越的障礙。Superscalar結構使用多個功能部件同時執行多條指令,實現指令級的並行(Instruction-Level Parallelism,ILP)。但其控制邏輯複雜,實現困難,研究表明,Superscalar結構的ILP一般不超過8。VLIW結構使用多個相同功能部件執行一條超長的指令,但也有兩大問題:編譯技術支持和二進制兼容問題。

未來的主流套用需要處理器具備同時執行更多條指令的能力,但是從單一執行緒中已經不太可能提取更多的並行性,主要有以下兩個方面的原因:一是不斷增加的晶片面積提高了生產成本;二是設計和驗證所花費的時間變得更長。在處理器結構上,更複雜化的設計也只能得到有限的性能提高。

對單一控制執行緒的依賴限制了多數套用可提取的並行性,而主流商業套用,如線上資料庫事務處理(Online Database Transaction)與網路服務(如Web伺服器)等,一般都具有較高的執行緒級並行性(TLP,Thread Level Parallelism)。為此,研究人員提出了兩種新型體系結構: 單晶片多處理器(CMP)與同時多執行緒處理器(Simultaneous Multithreading,SMT),這兩種體系結構可以充分利用這些套用的指令級並行性和執行緒級並行性,從而顯著提高了這些套用的性能。

從體系結構的角度看,SMT比CMP對處理器資源利用率要高,在克服線延遲影響方面更具優勢。CMP相對SMT的最大優勢還在於其模組化設計的簡潔性。複製簡單設計非常容易,指令調度也更加簡單。同時SMT中多個執行緒對共享資源的爭用也會影響其性能,而CMP對共享資源的爭用要少得多,因此當套用的執行緒級並行性較高時,CMP性能一般要優於SMT。此外在設計上,更短的晶片連線使CMP比長導線集中式設計的SMT更容易提高晶片的運行頻率,從而在一定程度上起到性能最佳化的效果。

趨勢總結

單晶片多處理器通過在一個晶片上集成多個微處理器核心來提高程式的並行性。每個微處理器核心實質上都是一個相對簡單的單執行緒微處理器或者比較簡單的多執行緒微處理器,這樣多個微處理器核心就可以並行地執行程式代碼,因而具有了較高的執行緒級並行性。由於CMP採用了相對簡單的微處理器作為處理器核心,使得CMP具有高主頻、設計和驗證周期短、控制邏輯簡單、擴展性好、易於實現、功耗低、通信延遲低等優點。此外,CMP還能充分利用不同套用的指令級並行和執行緒級並行,具有較高執行緒級並行性的套用如商業套用等可以很好地利用這種結構來提高性能。單晶片多處理器已經成為處理器體系結構發展的一種必然趨勢。

性能評測方法

評測對於其設計,開發和套用都至關重要。公開的實際評測平台包括COSMIC Heterogeneous Multiprocessor Benchmark Suite 。