晶片介紹

外圍器件PCF8563I2C實時時鐘/日曆晶片

系統套用

摘要

文中介紹了PCF8563的結構、功能及工作原理。結合其在8051系統中的套用實例,給出了PCF8563與8051單片機的硬體接口電路和C語言軟體編程程式。

關鍵字

I2C匯流排串列接口PCF8563BCD碼 C語言

PCF8563簡介

PCF8563是PHILIPS公司生產的低功耗CMOS實時時鐘/日曆晶片,晶片最大匯流排速度為400kbits/s,每次讀寫數據後,其內嵌的字地址暫存器器會自動產生增量。PCF8563可廣泛套用於行動電話、便攜儀器、傳真機、電池電源等產品中。

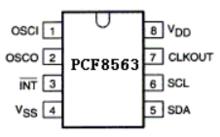

PCF8563的引腳排列如圖1所示,各引腳功能說明如表1所列。

PCF8563有16個8位暫存器,其中包括:可自動增量的地址暫存器、內置32.768kHz的振盪器(帶有一個內部集成電容)、分頻器(用於給實時時鐘RTC提供源時鐘)、可程式時鐘輸出、定時器、報警器、掉電檢測器和400kHz的I2C匯流排接口。所有16個暫存器設計成可定址的8位並行暫存器,但不是所有位都有用。當一個RTC暫存器被讀時,所有計數器的內容將被鎖存,因此,在傳送條件下,可以禁止對時鐘/日曆晶片的錯讀。表2、表3所列為各暫存器概況及對應的記憶體地址和功能,同時列出了它們的BCD格式編碼。表中“——”表示無效位,“0”表示此位應置邏輯。表3中的世紀位C=0指定世紀數為20XX,C=1指定世紀數為19XX。當年暫存器中的99變00時,世紀位才會改變。

其主要特性有:

1、寬電壓範圍 1.0~5.5V, 復位電壓標準值Vlow=0.9V。

2、超低功耗:典型值為 0.25uA (VDD=3.0V,Tamb=25℃)。

3、可程式時鐘輸出頻率為:32.768KHz 、1024Hz 、32Hz 、1Hz。

4、四種報警功能和定時器功能。

5、內含復位電路、振盪器電容和掉電檢測電路。

6、開漏中斷輸出。

7、400kHz I2C匯流排(VDD=1.8~5.5V),其從地址讀 0A3H;寫 0A2H。

管腳描述

PCF8563 管腳圖

PCF8563 管腳圖| 符號 | 管腳號 | 描 述 |

| OSCI | 1 | 振盪器輸入 |

| OSCO | 2 | 振盪器輸出 |

| /INT | 3 | 中斷輸出(開漏:低電平有效) |

| VSS | 4 | 地 |

| SDA | 5 | 串列數據 I/O |

| SCL | 6 | 串列時鐘輸入 |

| CLKOUT | 7 | 時鐘輸出(開漏) |

| VDD | 8 | 正電源 |

工作原理

PCF8563 有 16 個8位暫存器:一個可自動增量的地址暫存器,一個內置 32.768KHz的振盪器(帶有一個內部集成的電容)一個分頻器(用於給實時時鐘RTC 提供源時鐘)一個可程式時鐘輸出,一個定時器,一個報警器,一個掉電檢測器和一個 400KHz I2C匯流排接口。

所有16 個暫存器設計成可定址的 8 位並行暫存器,但不是所有位都有用。前兩個暫存器(記憶體地址 00H,01H)用於控制暫存器和狀態暫存器,記憶體地址 02H~08H 用於時鐘計數器(秒~年計數器) ,地址 09H~0CH 用於報警暫存器(定義報警條件) ,地址 0DH 控制CLKOUT 管腳的輸出頻率,地址 0EH 和 0FH 分別用於定時器控制暫存器和定時器暫存器。秒、分鐘、小時、日、月、年、分鐘報警、小時報警、日報警暫存器,編碼格式為 BCD, 星期和星期報警暫存器不以 BCD 格式編碼。當一個 RTC 暫存器被讀時,所有計數器的內容被鎖存,因此,在傳送條件下,可以禁止對時鐘日曆晶片的錯讀。

暫存器概況

地址 暫存器名稱 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 00H 控制/狀態暫存器1 TEST 0 STOP 0 TESTC 0 0 0 01H 控制/狀態暫存器2 0 0 0 TI/TP AF TF AIE TIE 0DH CLKOUT頻率暫存器 FE — — — — — FD1 FD0 0EH定時器控制暫存器 TE — — — — — TD1 TD0 0FH 定時器倒計數數值暫存器 定時器倒計數數值

BCD暫存器

1.地址暫存器名稱 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0。

02H 秒:VL 00~59BCD碼格式數

03H 分:00~59BCD碼格式數

04H 時:00~23BCD碼格式數

05H 日:01~31BCD碼格式數

06H 星期:0~6

07H 月/世紀:C - - 01~12BCD碼格式數

08H 年:00~99BCD碼格式數

09H分鐘報警:AE - 00~59BCD碼格式數

0AH小時報警:AE - 00~23BCD碼格式數

0BH 日報警: AE -01~31BCD碼格式數

0CH 星期報警:AE - 0~6

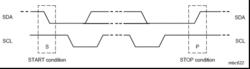

2.開始和停止

STOP和START狀態之間匯流排空置,數據線(SDA)和時鐘線(SCL)保持在高電平。SCL高電平時SDA下降沿,為啟動條件(S);SCL高電平時SDA上升沿為停止條件(P),參見下圖。

開始和停止定義

開始和停止定義3. 位傳送

每個時鐘脈衝傳送一個數據位,SDA線上的數據在時鐘脈衝高電平時應保持穩定,否則將成為控制信號,參見圖4。

4.標誌位

在START和STOP之間,發射器傳送給接收器的數據數量沒有限制。在每個8位位元組後加一個標誌位,發射器便產生一個高電平的標誌位,這時主設備產生一個附加標誌位時鐘脈衝。

“從接收器”必須在接收到每個位元組後產生一個標誌位,“主接收器”也必須在接收“從發射器”傳送的每個位元組後產生一個標誌位。

在標誌位時鐘脈衝出現時,SDA線應保持低電平(應考慮起動和保持時間)。

發射器應在從設備接收到最後一個位元組時變為低電平,而使接收器產生標誌位,這時主設備即可產生停止條件。參見圖5。

5. I2C匯流排協定

用I2C匯流排傳遞數據前,接收的設備應先標明地址,在I2C匯流排起動後,這個地址與第一個傳送位元組一起被傳送出去。PCF8563可以作為一個從接收器或從傳送器,此時的時鐘信號線SCL只能輸入信號線,數據信號線SDA則為一條雙向信號線。PCF8563的從地址參見圖6。

套用概述

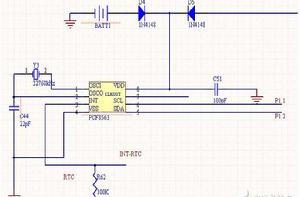

圖7所示為PCF8563的具體套用電路圖,對圖中石英晶片頻率的調整,筆者給出3種可行性方法,供參考: 方法1:定值OSCI電容。計算所需的電容平均值,用此值的定值電容,通電後在CLKOUT管腳上測出的頻率應為32.768kHz,測出的頻率值偏差取決於石英晶片本身,電容偏差和器件之間的偏差平均為±5×10 -6。平均偏差可達5分鐘/年。 方法2:OSCI微調電容。可通過調整OSCI管腳的微調電容式振盪器的頻率來獲得更高的精度,此時可測出通電時管腳CLKOUT上的信號頻率為32.768kHz。 方法3:OSCI輸出。直接測量管腳OSCI的輸出。

程式示例

以下的C語言源程式是用8051單片機的普通I/O口(如P0.0/P0.4)模擬實現PCF8563的I2C時鐘/日曆晶片的操作,有位元組寫/讀兩種狀態。程式中從地址的讀地址為0A3H,寫地址為0A2H.所傳送的數據位元組為9個,傳送的初始數據在rom_sed[9]中,rom_sed[9]定義了暫存器中當前傳送的值:控制/狀態暫存器1為0,控制/狀態暫存器2為0,秒暫存器為0,分鐘暫存器55,小時暫存器為23,日暫存器為31,星期暫存器為6,月/世紀暫存器為0x12,年暫存器為0x99(即1999年12月31日23點55分0秒),當程式運行一段時間(5分鐘)後,從地址暫存器02H開始讀數據,數據存放在rom_rec7中,發現變數rom_rec7變為2000年1月1日0點0分。若外轉帳電路有顯示,則時間可以顯示在面板上。

#include<d:.h>

#define byte unsignedchar sbit scl=0x81; //定義串列I/O口

sbit sda=0x80;

idata byte rom_sed[9];

idata byte rom_rec[7];

idata byte j,k;

bit flag,flag1;

void delay(void)//延時子程式

{

data byte i;

for(i=0;i<6;i++);

}

void I_start(void)//傳送I2C匯流排起始條件子程式

{sda=1; ;

scl=1;

delay();

sda=0;

delay();

scl=0; ;

}

void I_stop(void) //I2C匯流排停止條件子程式

{

sda=0; ;

scl=1;

delay();

sda=1;

delay();

}

bit I_send(byte I_data) //位元組數據傳送子程式

{

data byte i;

for(i=0,i<8;i++)

{

sda-(bit)(I_data&0x80);

I_data=I_data<<1; ;

scl=1;

delay();

scl=0; } ;;

sda=1; ;; //readyfor receiving ACK

bit scl=1; ;; //start receiving ack

bit flag=0;

if(sda= =0)

flag=0;

else flag=1; //

return(~I_clock());

scl=0;return(flag);

}

byte I_receive(void) //位元組數據接收子程式

{

data byte i;

byteI_data=0;

sda=1;

for(i=0;I<8;i++)

{

I_data*=2; ;

scl=0;

delay();

scl=1;

;; if(sda= =1)I_data++; ;;

}

scl=0; ;;; sda=0;

if(flag1==0)

{

;;scl=1;

delay();

scl=0;

} //not last receic_byte ACK

else

{

sda=1;;;scl=1;

delay();

scl=0;

flag1=0;

} //the last receive_byte ~ACK

return(I_data);

}

main() //主程式

{

data byte i;

rom_sed[0]=0x00;

rom_sed[1]=0x00;

rom_sed[2]=0x00;

rom_sed[3]=0x55;

rom_sed[4]=0x23;

rom_sed[5]=0x31;

rom_sed[6]=0x06;

rom_sed[7]=0x92;

rom_sed[8]=0x99;

for(i=0;i<255;i++)

delay();

I_start();

if(~I_send(rom_sed[i]))

;

else

;

}

I_stop();

}

else

;

}

else

;

start: I_start();

if(~I_send(0xa2))//pcf_write address

{

if(~I_send(0x02)) //pcf_status register address

{

I_start();

if(~I_send(0xa3)) //write status register

{for(i=0;i<7;i++)

{

if(i= =6)

flag1=1;

else

flag1=0;

rom_rec[i]=I_receive();

switch(i)

{

case1:rom_rec[i]=rom_rec[i]&0x7f;break;

case2:

case3:

rom_rec[i]=rom_rec[i]&0x3f;break;

case4:

rom_rec[i]=rom_rec[i]&0x07;

break;

case5:

rom_rec[i]=rom_rec[i]&0x9f;

brealk;

default:break;

}

}

I_stop()

}

}

}

goto start;

}