內部結構

AT89C2051是一個帶有2K位元組閃速可程式可擦除唯讀存儲器(EEPROM)的低電壓,高性能8位CMOS微處理器。它採用ATMEL的高密非易失存儲技術製造並和工業標準MCS-51指令集和引腳結構兼容。通過在單塊晶片上組合通用的CPLI和閃速存儲器,ATMEL的AT89C2051是一強勁的微型處理器,它對許多嵌入式控制套用提供一定高度靈活和成本低的解決辦法。

AT89C2051提供以下標準功能:2K位元組閃速存儲器,128位元組RAM,15根I/O口,兩個16位定時器,一個五向量兩級中斷結構,一個全雙工串列口,一個精密模擬比較器以及兩種可選 的軟體節電工作方式。空閒方停止CPU工作但允許RAM、定時器/計數器、串列工作口和中斷系統繼續工作。掉電方式保存RAM內容但振盪器停止工作並禁止有其它部件的工作到下一個硬體復位。

程式保密

AT89C2051設計有2個程式保密位,保密位1被編程之後,程式存儲器不能再被編程除非做一次擦除,保密位2被編程之後,程式不能被讀出。

軟硬體的開發

AT89C2051可以採用下面兩種方法開發套用系統。

1、由於89C2051內部程式存儲器為Flash,所以修改它內部的程式十分方便快捷,只要配備一個可以編程89C2051的編程器即可。調試人員可以採用程式編輯-編譯-固化-插到電路板中試驗這樣反覆循環的方法,對於熟練的MCS-51程式設計師來說,這種調試方法並不十分困難。但是做這種調試不能夠了解片內RAM的內容和程式的走向等有關信息。

2、將普通8031/80C31仿真器的仿真插頭中P1.0~P1.7和P3.0~P3.6引出來仿真2051,這種方法可以運用單步、斷點的調試方法,但是仿真不夠真實,比如,2051的內部模擬比較器功能,P1口、P3口的增強下拉能力等等。

引腳說明

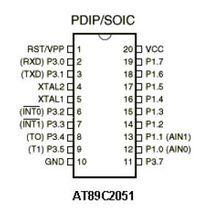

AT89C2051晶片引腳圖

AT89C2051晶片引腳圖AT89C2051的引腳圖如右圖所示。

1、VCC:電源電壓。

2、GND:地。

3、P1口:P1口是一個8位雙向I/O口。口引腳P1.2~P1.7提供內部上拉電阻,P1.0和P1.1要求外部上拉電阻。P1.0和P1.1還分別作為片內精密模擬比較器的同相輸入(ANI0)和反相輸入(AIN1)。P1口輸出緩衝器可吸收20mA電流並能直接驅動LED顯示。當P1口引腳寫入“1”時,其可用作輸入端,當引腳P1.2~P1.7用作輸入並被外部拉低時,它們將因內部的寫入“1”時,其可用作輸入端。當引腳P1.2~P1.7用作輸入並被外部拉低時,它們將因內部的上拉電阻而流出電流。

4、P3口:P3口的P3.0~P3.5、P3.7是帶有內部上拉電阻 的七個雙向I/O口引腳。P3.6用於固定輸入片內比較器的輸出信號並且它作為一通用I/O引腳而不可訪問。P3口緩衝器可吸收20mA電流。當P3口寫入“1”時,它們被內部上拉電阻拉高並可用作輸入端。用作輸入時,被外部拉低的P3口腳將用上拉電阻而流出電流。

P3口還用於實現AT89C2051的各種第二功能,如下表所列:

| 引腳口 | 功 能 |

| P3.0 | RXD串列輸入連線埠 |

| P3.1 | TXD串列輸出連線埠 |

| P3.2 | INT0 外中斷0 |

| P3.3 | INT1 外中斷1 |

| P3.4 | T0定時器0外部輸入 |

| P3.5 | T1定時器1外部輸入 |

P3口還接收一些用於閃速存儲器編程和程式校驗的控制信號。

5、RST:復位輸入。RST一旦變成高電平所有的I/O引腳就復位到“1”。當振盪器正在運行時,持續給出RST引腳兩個機器周期的高電平便可完成復位。每一個機器周期需12個振盪器或時鐘周期。

6、XTAL1:作為振盪器反相器的輸入和內部時鐘發生器的輸入。

7、XTAL2:作為振盪器反相放大器的輸出。

主要性能

1、和MCS-51產品兼容;

2、2KB可重編程FLASH存儲器(10000次);

3、2.7-6V電壓範圍;

4、全靜態工作:0Hz-24MHz;

5、2級程式存儲器保密鎖定;

6、128*8位內部RAM;

7、15條可程式I/O線;

8、兩個16位定時器/計數器;

9、6箇中斷源;

10、可程式 ;

11、高精度電壓比較器(P1.0,P1.1,P3.6);

12、直接驅動LED的輸出連線埠。